การใช้งาน AI สำหรับเร่งความเร็ว บนชุดประเมิน Xilinx VCK190 ด้วย IP Core ของ Design Gateway

2022-11-18

Xilinxอุปกรณ์ซีรีส์ Versal AI Core ได้รับการออกแบบมาเพื่อแก้ปัญหาเฉพาะและยากที่สุดของการอนุมานของ AI โดยใช้เอ็นจิ้นการประมวลผล AI ระดับ ASIC ที่มีประสิทธิภาพในการคำนวณสูง ร่วมกับแฟบริกที่ตั้งโปรแกรมได้ยืดหยุ่นเพื่อสร้างแอปพลิเคชัน AI พร้อมตัวเร่งความเร็วที่เพิ่มประสิทธิภาพสูงสุดสำหรับปริมาณงานที่กำหนดในขณะที่ให้พลังงานต่ำและ เวลาแฝงต่ำ

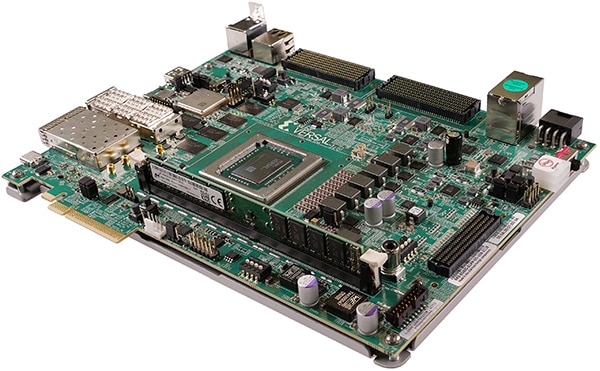

ซีรีส์ Versal AI Core ชุดทดสอบ VCK190 คุณสมบัติอุปกรณ์ VC1902 ซึ่งมีประสิทธิภาพ AI ที่ดีที่สุดในพอร์ตโฟลิโอ ชุดนี้สร้างขึ้นสำหรับการออกแบบที่ต้องการการอนุมานของ AI และการประมวลผลสัญญาณความเร็วสูง มอบพลังการประมวลผลที่มากกว่าซีพียูระดับเซิร์ฟเวอร์ในปัจจุบันถึง 100 เท่า และมีตัวเลือกการเชื่อมต่อที่หลากหลาย ทำให้ชุด VCK190 เป็นแพลตฟอร์มการประเมินและการสร้างต้นแบบในอุดมคติสำหรับการใช้งานที่หลากหลายตั้งแต่คลาวด์ไปจนถึงเอดจ์

รูปที่ 1: ชุดประเมิน Xilinx Versal AI Core series VCK190 (แหล่งรูปภาพ: AMD, Inc)

รูปที่ 1: ชุดประเมิน Xilinx Versal AI Core series VCK190 (แหล่งรูปภาพ: AMD, Inc)

คุณลักษณะสำคัญของชุดประเมิน VCK190

- อุปกรณ์ Onboard ซีรี่ส์ Versal AI Core

- มาพร้อมกับซิลิกอนการผลิต Versal ACAP XCVC1902

- AI และ DSP Engines ให้ประสิทธิภาพการประมวลผลที่สูงกว่า CPU ระดับเซิร์ฟเวอร์ในปัจจุบันถึง 100 เท่า

- การออกแบบอ้างอิงพันธมิตรที่สร้างไว้ล่วงหน้าสำหรับการสร้างต้นแบบอย่างรวดเร็ว

- เทคโนโลยีการเชื่อมต่อล่าสุดสำหรับการพัฒนาการใช้งานระดับแนวหน้า

- PCIe® Gen4 Hard IP ในตัวสำหรับอินเทอร์เฟซอุปกรณ์ประสิทธิภาพสูง เช่น NVMe SSD และโฮสต์โปรเซสเซอร์

- 100G EMAC Hard IP ในตัวสำหรับอินเทอร์เฟซเครือข่ายความเร็วสูง 100G

- อินเทอร์เฟซหน่วยความจำ DDR4 และ LPDDR4

- เครื่องมือเพิ่มประสิทธิภาพร่วมกันและวิธีการดีบัก

- Vivado® ML, แพลตฟอร์มซอฟต์แวร์รวม Vitis™, Vitis AI, เครื่องมือ AI Engine สำหรับการพัฒนาแอปพลิเคชันการอนุมาน AI

AI Interface Acceleration กับอุปกรณ์ Versal AI Core Series ของ Xilinx

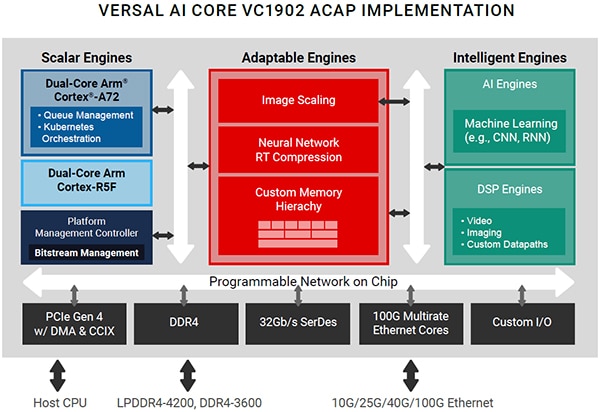

รูปที่ 2: แผนภาพบล็อกอุปกรณ์ Xilinx Versal AI Core VC1902 ACAP (แหล่งรูปภาพ: AMD, Inc)

รูปที่ 2: แผนภาพบล็อกอุปกรณ์ Xilinx Versal AI Core VC1902 ACAP (แหล่งรูปภาพ: AMD, Inc)

Versal® AI Core adaptive Compute Accelerated Platform (ACAP) เป็นอุปกรณ์แบบหลายคอร์ที่ผสมผสานกันอย่างลงตัว ซึ่งสามารถปรับเปลี่ยนได้แบบไดนามิกที่ระดับฮาร์ดแวร์และซอฟต์แวร์สำหรับปริมาณงาน AI ที่หลากหลาย ทำให้เหมาะอย่างยิ่งสำหรับแอปพลิเคชันการประมวลผลขอบ AI หรือตัวเร่งความเร็วบนคลาวด์ การ์ด แพลตฟอร์มดังกล่าวผสานรวม Scalar Engines ยุคหน้าสำหรับการประมวลผลแบบฝังตัว Adaptable Engines สำหรับความยืดหยุ่นของฮาร์ดแวร์ และ Intelligent Engines ที่ประกอบด้วย DSP Engines และ AI Engines ที่ปฏิวัติวงการสำหรับการอนุมานและการประมวลผลสัญญาณ ผลลัพธ์ที่ได้คือตัวเร่งความเร็วแบบปรับได้ที่เหนือกว่าประสิทธิภาพ เวลาแฝง และประสิทธิภาพพลังงานของ FPGA และ GPU แบบดั้งเดิมสำหรับเวิร์กโหลด AI/ML

จุดเด่นของแพลตฟอร์ม Versal ACAP

- เครื่องยนต์ที่ค่าปรับได้

- ลำดับชั้นของหน่วยความจำแบบกำหนดเองช่วยเพิ่มประสิทธิภาพการเคลื่อนย้ายข้อมูลและการจัดการสำหรับเคอร์เนลตัวเร่งความเร็ว

- ฟังก์ชันก่อนและหลังการประมวลผลรวมถึงการบีบอัด RT โครงข่ายประสาทเทียมและการปรับขนาดภาพ

- เครื่องยนต์ AI (DPU)

- อาร์เรย์ของเวกเตอร์โปรเซสเซอร์แบบเรียงต่อกัน ประสิทธิภาพสูงสุด 133 INT8 TOPS พร้อมอุปกรณ์ XCVC1902 เรียกว่า Deep Learning Processing Unit หรือ DPU

- เหมาะอย่างยิ่งสำหรับโครงข่ายประสาทเทียมตั้งแต่ CNN, RNN และ MLP; ฮาร์ดแวร์ที่ปรับเปลี่ยนได้เพื่อเพิ่มประสิทธิภาพสำหรับอัลกอริธึมที่กำลังพัฒนา

- เครื่องยนต์สเกลาร์

- ระบบย่อยการประมวลผล Quad-Core ARM, ตัวควบคุมการจัดการแพลตฟอร์มเพื่อความปลอดภัย พลังงาน และการจัดการบิตสตรีม

VCK190 AI ประสิทธิภาพสรุป

VCK190 สามารถมอบประสิทธิภาพการประมวลผลที่สูงขึ้นกว่า 100 เท่าเมื่อเทียบกับ CPU ระดับเซิร์ฟเวอร์ปัจจุบัน ด้านล่างนี้คือตัวอย่างประสิทธิภาพตามการใช้งาน AI Engine โดย C32B6 DPU Core ที่มีแบตช์ = 6 โปรดดูตารางต่อไปนี้สำหรับประสิทธิภาพการรับส่งข้อมูล (ในเฟรม/วินาทีหรือ fps) สำหรับตัวอย่างโครงข่ายประสาทเทียมต่างๆ บน VCK190 ที่มี DPU ทำงานที่ 1250 MHz

|

ตารางที่ 1: ตัวอย่างประสิทธิภาพการอนุมาน VCK190 AI

ดูรายละเอียดประสิทธิภาพ VCK190 AI เพิ่มเติมจาก Vitis AI Library User Guide (UG1354), r2.5.0 ได้ที่https://docs.xilinx.com/r/en-US/ug1354-xilinx-ai-sdk/VCK190-Evaluation-Board

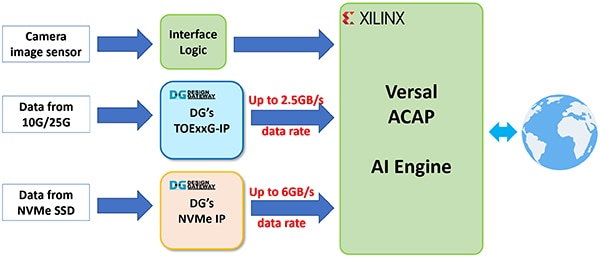

แกน IP ของ Design Gateway ช่วยเร่งประสิทธิภาพของการใช้งาน AI ได้อย่างไร

IP Core จาก Design Gateway ได้รับการออกแบบมาเพื่อจัดการเครือข่ายและโปรโตคอลการจัดเก็บข้อมูลโดยไม่จำเป็นต้องมีการแทรกแซงของ CPU สิ่งนี้ทำให้เหมาะอย่างยิ่งที่จะลดโหลดระบบ CPU จากการประมวลผลโปรโตคอลที่ซับซ้อน และช่วยให้พวกเขาใช้พลังการประมวลผลส่วนใหญ่สำหรับแอปพลิเคชัน AI รวมถึงการอนุมาน AI การประมวลผลข้อมูลก่อนและหลัง อินเทอร์เฟซผู้ใช้ การสื่อสารเครือข่าย และการเข้าถึงที่เก็บข้อมูลที่ดีที่สุดเท่าที่จะเป็นไปได้ ประสิทธิภาพ.

รูปที่ 3: บล็อกไดอะแกรมของตัวอย่างการใช้งาน AI ที่มี IP Core ของ Design Gateway (ที่มาของรูปภาพ: Design Gateway)

รูปที่ 3: บล็อกไดอะแกรมของตัวอย่างการใช้งาน AI ที่มี IP Core ของ Design Gateway (ที่มาของรูปภาพ: Design Gateway)

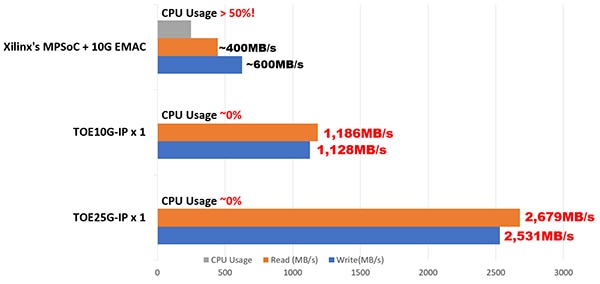

ประสิทธิภาพของ TCP Offload Engine IP (TOExxG-IP) ของ Design Gateway

การประมวลผลความเร็วสูง สตรีมข้อมูล TCP ความเร็วสูงมากกว่า 10GbE หรือ 25GbE โดยระบบ CPU แบบดั้งเดิมต้องการเวลา CPU มากกว่า 50% ซึ่งลดประสิทธิภาพโดยรวมของแอปพลิเคชัน AI จากการทดสอบประสิทธิภาพ 10G TCP บนระบบ MPSoC Linux ของ Xilinx การใช้งาน CPU ระหว่างการส่งข้อมูล 10GbE TCP นั้นมากกว่า 50% ความเร็วในการส่งและรับข้อมูล TCP สามารถทำได้เพียงประมาณ 40% ถึง 60% ของความเร็ว 10GbE หรือ 400 MB/s ถึง 600 เมกะไบต์/วินาที

ด้วยการใช้ TOExxG-IP Core จาก Design Gateway การใช้งาน CPU สำหรับการส่งผ่าน TCP ที่มากกว่า 10GbE และ 25GbE สามารถลดลงเหลือเกือบ 0% ในขณะที่การใช้แบนด์วิธอีเธอร์เน็ตสามารถทำได้เกือบ 100% ซึ่งช่วยให้สามารถส่งและรับข้อมูลผ่านเครือข่าย TCP ได้โดยตรงโดยใช้ตรรกะของฮาร์ดแวร์ล้วนๆ และป้อนเข้าสู่ Versal AI Engine โดยใช้ CPU ขั้นต่ำและเวลาแฝงที่ต่ำที่สุดเท่าที่จะเป็นไปได้ รูปที่ 4 ด้านล่างแสดงการใช้งาน CPU และการเปรียบเทียบความเร็วในการส่งข้อมูล TCP ระหว่างระบบ TOExxG-IP และ MPSoC Linux

รูปที่ 4: การเปรียบเทียบประสิทธิภาพของการส่งผ่าน 10G/25G TCP โดยระบบ MPSoC Linux และ TOExxG-IP Core ของ Design Gateway (ที่มาของรูปภาพ: Design Gateway)

รูปที่ 4: การเปรียบเทียบประสิทธิภาพของการส่งผ่าน 10G/25G TCP โดยระบบ MPSoC Linux และ TOExxG-IP Core ของ Design Gateway (ที่มาของรูปภาพ: Design Gateway)

ออกแบบ TOExxG-IP ของ Gateway สำหรับอุปกรณ์ Versal

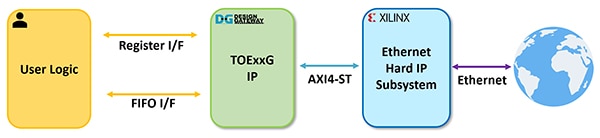

รูปที่ 5: ภาพรวมระบบ TOExxG-IP (ที่มาของรูปภาพ: Design Gateway)

รูปที่ 5: ภาพรวมระบบ TOExxG-IP (ที่มาของรูปภาพ: Design Gateway)

แกน TOExxG-IP ใช้สแต็ค TCP/IP (ในตรรกะฮาร์ดไวร์) และเชื่อมต่อกับโมดูล EMAC Hard IP และ Ethernet ของ Xilinx สำหรับอินเทอร์เฟซฮาร์ดแวร์ชั้นล่างด้วยความเร็วอีเธอร์เน็ต 10G/25G/100G ส่วนต่อประสานผู้ใช้ของ TOExxG-IP ประกอบด้วยส่วนต่อประสานการลงทะเบียนสำหรับสัญญาณควบคุมและส่วนต่อประสาน FIFO สำหรับสัญญาณข้อมูล TOExxG-IP ออกแบบมาเพื่อเชื่อมต่อกับระบบย่อย Ethernet ของ Xilinx ผ่านอินเทอร์เฟซ AXI4-ST ความถี่สัญญาณนาฬิกาของอินเทอร์เฟซผู้ใช้ขึ้นอยู่กับความเร็วของอินเทอร์เฟซอีเทอร์เน็ต (เช่น 156.625 MHz หรือ 322.266 MHz)

คุณสมบัติของ TOExxG-IP

- การใช้งานสแต็ก TCP/IP เต็มรูปแบบโดยไม่จำเป็นต้องใช้ CPU

- รองรับหนึ่งเซสชันกับ TOExxG-IP หนึ่งรายการ

- สามารถใช้หลายเซสชันได้โดยใช้ TOExxG-IP หลายอินสแตนซ์

- รองรับทั้งโหมดเซิร์ฟเวอร์และไคลเอ็นต์ (เปิดและปิดแบบพาสซีฟ/แอคทีฟ)

- รองรับเฟรมจัมโบ้

- อินเทอร์เฟซข้อมูลอย่างง่ายโดยอินเทอร์เฟซ FIFO มาตรฐาน

- อินเทอร์เฟซการควบคุมอย่างง่ายโดยอินเทอร์เฟซ RAM พอร์ตเดียว

การใช้ทรัพยากร FPGA บนอุปกรณ์ FPGA XCVC1902-VSVA2197-2MP-ES แสดงอยู่ในตารางที่ 2 ด้านล่าง

|

ตารางที่ 2: ตัวอย่างสถิติการใช้งานสำหรับอุปกรณ์ Versal

รายละเอียดเพิ่มเติมของ TOExxG-IP ได้อธิบายไว้ในเอกสารข้อมูลซึ่งสามารถดาวน์โหลดได้จากเว็บไซต์ของ Design Gateway ที่ลิงค์ต่อไปนี้:

- ตารางข้อมูล TOE10G-IP Core Xilinx

- ตารางข้อมูล TOE25G-IP Core Xilinx

- TOE100G-IP Core Xilinx เอกสารข้อมูล

ออกแบบประสิทธิภาพของ NVMe Host Controller IP ของเกตเวย์

ความเร็วอินเทอร์เฟซ NVMe Storage พร้อม PCIe Gen3 x4 หรือ PCIe Gen4 x4 มีอัตราข้อมูลสูงสุด 32 Gbps และ 64 Gbps ซึ่งสูงกว่าความเร็วอีเธอร์เน็ต 10GbE สามถึงหกเท่า การประมวลผลโปรโตคอลหน่วยเก็บข้อมูล NVMe ที่ซับซ้อนโดย CPU เพื่อให้ได้ความเร็วสูงสุดในการเข้าถึงดิสก์ ต้องใช้เวลา CPU มากกว่าโปรโตคอล TCP ที่มากกว่า 10GbE

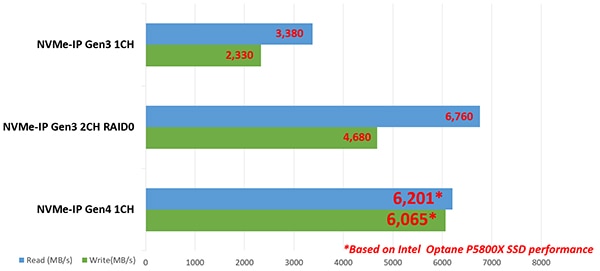

Design Gateway แก้ปัญหานี้ด้วยการพัฒนาคอร์ NVMe IP ที่สามารถทำงานเป็นตัวควบคุมโฮสต์ NVMe แบบสแตนด์อโลน สามารถสื่อสารกับ NVMe SSD ได้โดยตรงโดยไม่ต้องใช้ CPU สิ่งนี้ทำให้การเข้าถึง SSD ของ NVMe PCIe Gen3 และ Gen4 มีประสิทธิภาพและประสิทธิผลสูง ซึ่งช่วยลดความซับซ้อนของอินเทอร์เฟซผู้ใช้และคุณสมบัติมาตรฐานเพื่อความสะดวกในการใช้งานโดยไม่จำเป็นต้องมีความรู้เรื่องโปรโตคอล NVMe ประสิทธิภาพของ NVMe PCIe Gen4 SSD สามารถบรรลุความเร็วการถ่ายโอนสูงสุด 6 GB/s ด้วย NVMe IP ดังแสดงในรูปที่ 6

รูปที่ 6: การเปรียบเทียบประสิทธิภาพของ NVMe PCIe Gen3 และ Gen4 SSD กับ NVMe-IP Core ของ Design Gateway (ที่มาของรูปภาพ: Design Gateway)

รูปที่ 6: การเปรียบเทียบประสิทธิภาพของ NVMe PCIe Gen3 และ Gen4 SSD กับ NVMe-IP Core ของ Design Gateway (ที่มาของรูปภาพ: Design Gateway)

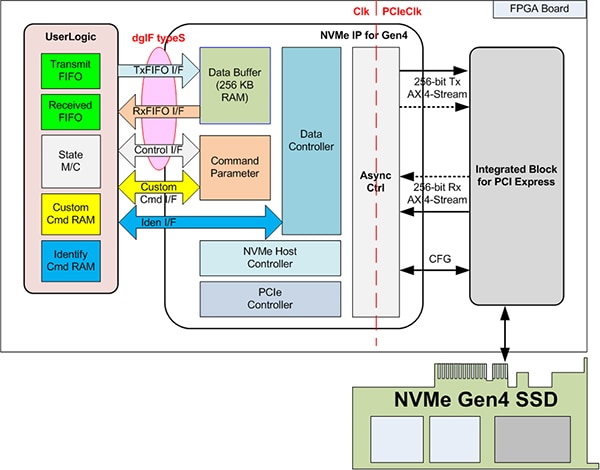

ออกแบบ NVMe-IP ของ Gateway สำหรับอุปกรณ์ Versal

รูปที่ 7: ภาพรวมของระบบ NVMe-IP (ที่มาของรูปภาพ: Design Gateway)

รูปที่ 7: ภาพรวมของระบบ NVMe-IP (ที่มาของรูปภาพ: Design Gateway)

คุณสมบัติของ NVMe-IP

- สามารถใช้งานในชั้นแอปพลิเคชัน ชั้นธุรกรรม ชั้นเชื่อมโยงข้อมูล และบางส่วนของชั้นกายภาพเพื่อเข้าถึง NVMe SSD โดยไม่ต้องใช้ CPU หรือหน่วยความจำ DDR ภายนอก

- ทำงานร่วมกับ Xilinx PCIe Gen3 และ Gen4 Hard IP

- ความสามารถในการใช้ BRAM และ URAM เป็นบัฟเฟอร์ข้อมูลโดยไม่ต้องใช้อินเทอร์เฟซหน่วยความจำภายนอก

- รองรับหกคำสั่ง: Identify, Shutdown, Write, Read, SMART และ Flush (รองรับคำสั่งเสริมเพิ่มเติมได้)

การใช้ทรัพยากร FPGA บนอุปกรณ์ FPGA XCVC1902-VSVA2197-2MP-ES แสดงอยู่ในตารางที่ 2

|

ตารางที่ 3: ตัวอย่างสถิติการใช้งานสำหรับอุปกรณ์ Versal

รายละเอียดเพิ่มเติมของ NVMe-IP สำหรับอุปกรณ์ Versal ได้อธิบายไว้ในเอกสารข้อมูลซึ่งสามารถดาวน์โหลดได้จากเว็บไซต์ของ Design Gateway ที่ลิงค์ด้านล่าง:

NVMe IP Core สำหรับ Gen4 Xilinx Datasheet

สรุป

ทั้งแกน TOExxG-IP และ NVMe-IP สามารถช่วยเร่งประสิทธิภาพของแอปพลิเคชัน AI ได้โดยการถ่ายระบบ CPU ออกจากการประมวลผลและโปรโตคอลที่ต้องใช้หน่วยความจำ เช่น TCP และโปรโตคอล NVMe Storage ซึ่งมีความสำคัญอย่างยิ่งต่อแอปพลิเคชัน AI แบบเรียลไทม์ ซึ่งช่วยให้อุปกรณ์ซีรีส์ Versal AI Core ของ Xilinx สามารถดำเนินการอนุมาน AI และแอปพลิเคชันคอมพิวเตอร์ประสิทธิภาพสูงได้โดยไม่มีคอขวดหรือความล่าช้าจากการประมวลผลโปรโตคอลเครือข่ายและการจัดเก็บข้อมูล

ชุดประเมิน VCK190 และโซลูชันเครือข่ายและสตอเรจ IP ของ Design Gateway ช่วยให้เกิดประสิทธิภาพสูงสุดในแอปพลิเคชัน AI โดยใช้ทรัพยากร FPGA ต่ำที่สุดเท่าที่จะเป็นไปได้ และประสิทธิภาพพลังงานที่สูงมากบนอุปกรณ์ Versal AI Core ของ Xilinx

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.