พื้นฐานของตัวสังเคราะห์ความถี่ลูปเฟสล็อค

Contributed By DigiKey's North American Editors

2021-02-03

อัตราข้อมูลที่เพิ่มขึ้นในบัสการสื่อสารแบบอนุกรมความเร็วสูงต้องการสัญญาณนาฬิกาของระบบที่มีความถี่สูงขึ้น, เสถียรภาพที่เหนือกว่า, ความละเอียดของความถี่ที่มากขึ้น และความบริสุทธิ์ของสัญญาณที่สูงขึ้น ซินธิไซเซอร์ดิจิตอลมีคุณสมบัติเหล่านี้โดยตรง แต่เฉพาะที่ความถี่ต่ำกว่า 2 หรือ 3 กิกะเฮิรตซ์ (GHz) จำเป็นต้องมีโซลูชันสำหรับความถี่สูงถึงหลายสิบกิกะเฮิรตซ์

โซลูชันนี้เริ่มต้นด้วยเฟสล็อกลูป (PLL) - ซินธิไซเซอร์ความถี่อนาล็อกที่สร้างความถี่สัญญาณนาฬิกาสูงสุด 30 GHz จากนั้นซินธิไซเซอร์จำนวนเต็ม N (ซึ่งคูณความถี่อ้างอิงด้วยค่าจำนวนเต็ม) และซินธิไซเซอร์ N เศษส่วน (ซึ่งคูณความถี่อ้างอิงด้วยค่าเศษส่วนที่ไม่ใช่จำนวนเต็ม) ใช้เทคนิคพิเศษที่ลดสัญญาณรบกวนเฟสและสิ่งที่แทรกมาในสัญญาณที่คล้ายกัน

บทความนี้อธิบายการออกแบบซินธิไซเซอร์ความถี่ N จำนวนเต็มและเศษส่วนโดยใช้อุปกรณ์ตัวอย่างจาก Analog Devices บทความนี้ยังเน้นถึงนวัตกรรมที่ช่วยให้อุปกรณ์เหล่านี้สามารถใช้สำหรับการเชื่อมโยงข้อมูลอนุกรมความเร็วสูงรวมถึงเรดาร์แบบ Agile ความถี่

จำนวนเต็ม N เฟสล็อคซินธิไซเซอร์ลูป

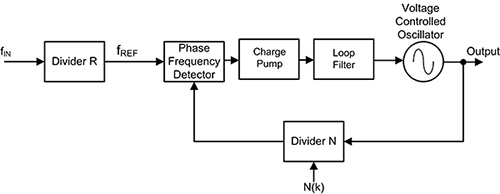

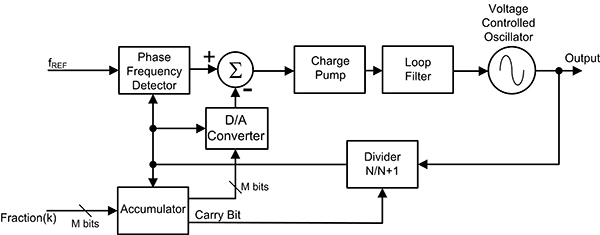

วงจร PLL ใช้สำหรับการควบคุมความถี่และเฟส สามารถกำหนดค่าเป็นแหล่งสัญญาณนาฬิกาตัวคูณความถี่เครื่องแยกสัญญาณการติดตามเครื่องกำเนิดไฟฟ้าหรือวงจรการกู้คืนนาฬิกา แต่ละแอปพลิเคชันเหล่านี้ต้องการลักษณะที่แตกต่างกัน แต่ทั้งหมดใช้แนวคิดวงจรพื้นฐานเดียวกัน รูปที่ 1 แสดงแผนภาพบล็อกของ PLL พื้นฐานที่กำหนดค่าเป็นตัวคูณความถี่

รูปที่ 1: แผนภาพบล็อกของซินธิไซเซอร์ความถี่ลูปล็อคเฟส N จำนวนเต็มคลาสสิก (แหล่งรูปภาพ: DigiKey)

รูปที่ 1: แผนภาพบล็อกของซินธิไซเซอร์ความถี่ลูปล็อคเฟส N จำนวนเต็มคลาสสิก (แหล่งรูปภาพ: DigiKey)

การทำงานของวงจรนี้เป็นเรื่องปกติของลูปที่ล็อกเฟสทั้งหมด โดยพื้นฐานแล้วเป็นระบบควบคุมป้อนกลับที่ควบคุมเฟสของออสซิลเลเตอร์ที่ควบคุมด้วยแรงดันไฟฟ้า (VCO) สัญญาณอินพุตถูกนำไปใช้กับตัวแบ่งมาตราส่วนล่วงหน้าซึ่งแบ่งความถี่อินพุตด้วยปัจจัย R เอาต์พุตของ pre-scaler คือความถี่อ้างอิงซึ่งเป็นอินพุตหนึ่งของเครื่องตรวจจับความถี่เฟส (PFD)

อินพุต PFD อื่นเป็นสัญญาณตอบรับจากเอาต์พุตของตัวนับหารด้วย N โดยปกติถ้า PLL ถูกล็อคความถี่ของสัญญาณทั้งสองจะใกล้เคียงกัน เอาต์พุตของเครื่องตรวจจับเฟสเป็นแรงดันไฟฟ้าที่เป็นสัดส่วนกับความแตกต่างของเฟสระหว่างอินพุตทั้งสอง หากลูปถูกปลดล็อกเช่นเดียวกับที่เกิดขึ้นเมื่อเริ่มต้นหรือหากมีการเปลี่ยนความถี่ของอินพุตขนาดใหญ่ในทันที เครื่องตรวจจับความถี่เฟสจะทำงานเพื่อควบคุมความถี่ในการทำงานของ PLL ให้เป็นค่าที่ต้องการ เมื่อได้ความถี่นั้น PFD จะกลับเข้าสู่โหมดตรวจจับเฟสและมีเอาต์พุตเป็นสัดส่วนกับความแตกต่างของเฟสระหว่างความถี่อ้างอิงและสัญญาณป้อนกลับ

เครื่องตรวจจับความถี่เฟสจะขับเคลื่อนปั๊มประจุซึ่งเป็นแหล่งกระแสไฟฟ้าสลับสองขั้ว ซึ่งหมายความว่ามันสามารถส่งออกพัลส์กระแสบวกและลบไปยังตัวกรองลูปของ PLL

ตัวกรองลูปจะทำให้สัญญาณผิดพลาดของเฟสเรียบขึ้นและยังกำหนดลักษณะไดนามิกของ PLL สัญญาณที่กรองแล้วจะควบคุม VCO โปรดทราบว่าเอาต์พุตของ VCO อยู่ที่ความถี่ N คูณอินพุตที่จ่ายให้กับอินพุตอ้างอิงความถี่ไปยังเครื่องตรวจจับความถี่เฟสและเป็น N/R คูณอินพุตความถี่ สัญญาณเอาท์พุตนี้จะถูกส่งกลับไปยังเครื่องตรวจจับเฟสโดยการหารด้วยตัวนับ N

โดยปกติตัวกรองลูปได้รับการออกแบบให้ตรงกับลักษณะที่ต้องการโดยแอปพลิเคชันของ PLL หาก PLL ต้องการรับและติดตามสัญญาณแบนด์วิดท์ของตัวกรองลูปจะมากกว่าหากคาดว่าจะมีความถี่อินพุตคงที่ ช่วงความถี่ที่ PLL ยอมรับและล็อกไว้เรียกว่า "ช่วงการจับภาพ" เมื่อ PLL ถูกล็อคและติดตามสัญญาณช่วงความถี่ที่ PLL จะติดตามเรียกว่า "ช่วงการติดตาม" โดยทั่วไปช่วงการติดตามจะใหญ่กว่าช่วงการจับภาพ ตัวกรองลูป PLL ยังกำหนดว่าความถี่ของสัญญาณสามารถเปลี่ยนแปลงได้เร็วเพียงใดและยังคงล็อคอยู่นั่นคืออัตราการฆ่าสูงสุด ยิ่งแบนด์วิดท์ตัวกรองลูปแคบลงเท่าใดข้อผิดพลาดเฟสที่ทำได้ก็จะยิ่งน้อยลงเท่านั้น สิ่งนี้มาพร้อมกับค่าใช้จ่ายของการตอบสนองที่ช้าลงและช่วงการจับภาพที่ลดลง PLL ที่ใช้ในแอพพลิเคชั่นนาฬิกาทำงานที่ความถี่คงที่เป็นหลัก โดยทั่วไปแบนด์วิดท์ของตัวกรองลูปควรน้อยกว่าความถี่อ้างอิงมาก

เนื่องจากความถี่เอาต์พุต PLL เป็นจำนวนเต็มผลคูณของความถี่อ้างอิงความละเอียดความถี่จึงเท่ากับความถี่อ้างอิง การได้รับความละเอียดความถี่ที่ละเอียดยิ่งขึ้นจำเป็นต้องลดความถี่อ้างอิงซึ่งทำได้ด้วยตัวนับก่อนมาตราส่วน R

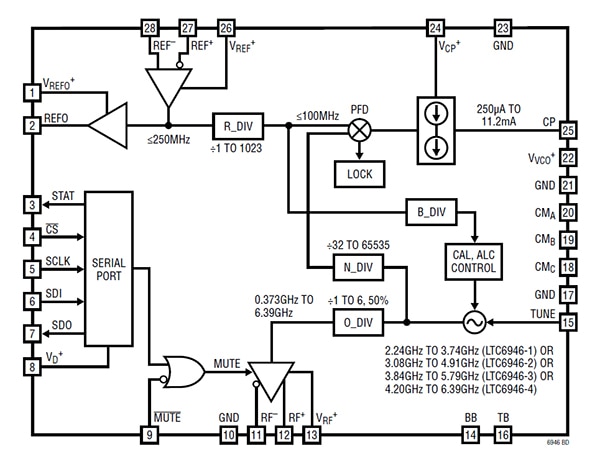

ตัวอย่างเชิงพาณิชย์ของซินธิไซเซอร์ความถี่ N จำนวนเต็มคือ Analog Devices LTC6946IUFD-3#PBFซินธิไซเซอร์ 0.64 ถึง 5.790 GHz สัญญาณรบกวนต่ำพร้อม VCO ในตัวและประสิทธิภาพปลอมที่ยอดเยี่ยม (รูปที่ 2) เป็นสมาชิกของตระกูล IC ซินธิไซเซอร์สี่ตัวแต่ละตัวมีช่วงความถี่ที่แตกต่างกันครอบคลุมช่วงทั้งหมด 0.373 ถึง 6.390 GHz

รูปที่ 2: แผนภาพบล็อกของอุปกรณ์อนาล็อก LTC6946IUFD-3 # PBF จำนวนเต็มเครื่องสังเคราะห์ความถี่ N พร้อมด้วย VCO ในตัว (แหล่งรูปภาพ: Analog Devices)

รูปที่ 2: แผนภาพบล็อกของอุปกรณ์อนาล็อก LTC6946IUFD-3 # PBF จำนวนเต็มเครื่องสังเคราะห์ความถี่ N พร้อมด้วย VCO ในตัว (แหล่งรูปภาพ: Analog Devices)

ซินธิไซเซอร์นี้ต้องการตัวกรองลูปที่ผู้ใช้ภายนอกให้มาซึ่งสามารถปรับให้เหมาะสมสำหรับแอปพลิเคชันเฉพาะ มีตัวนับตัวนับล่วงหน้าภายในที่มีช่วงการแบ่งตั้งแต่ 1 ถึง 1023 ตัวแบ่งวงมีตั้งแต่ 32 ถึง 65535 กระแสของปั๊มประจุสามารถปรับได้จาก 250 microamperes (mA) ถึง 11.2 milliamperes (mA) เพื่อให้ตรงกับความต้องการของตัวกรองลูป

Fractional N เฟสล็อคซินธิไซเซอร์ลูป

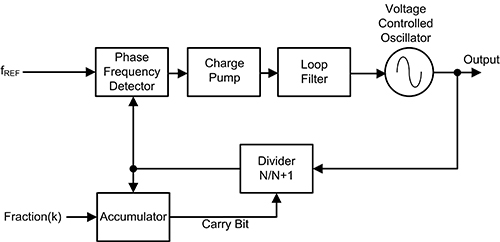

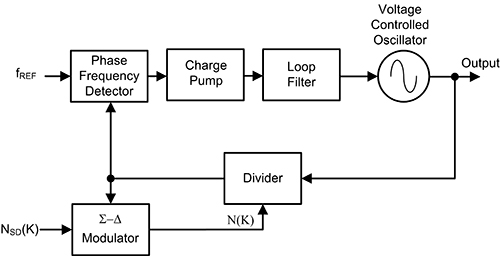

ความละเอียดความถี่ของซินธิไซเซอร์ PLL สามารถปรับปรุงได้โดยการลดขนาดขั้นตอนให้น้อยกว่าค่าจำนวนเต็ม เช่น การสร้างขั้นตอนเศษส่วนในตัวแบ่งวง (N) ซึ่งทำได้โดยการเปลี่ยนแปลงแบบไดนามิกหรือ "ลดทอน" ค่าการนับถอยหลัง ซึ่งหมายความว่าการตั้งค่าตัวแบ่งจะเก็บค่า N ไว้สำหรับจำนวนรอบคงที่ของความถี่เอาต์พุต PLL และจะก้าวไปเป็นค่าที่แตกต่างกันเป็นระยะ ๆ เช่น N + 1 ตัวอย่างเช่นหากการตั้งค่าตัวแบ่งเป็น 4 สำหรับช่วงเวลาอ้างอิงสามช่วงและ 5 สำหรับรอบการอ้างอิงที่สี่การนับถอยหลังที่มีประสิทธิผลคือ 4.25 วิธีหนึ่งในการบรรลุเป้าหมายนี้คือการใช้เครื่องสะสมดังแสดงในรูปที่ 3

รูปที่ 3: แผนภาพบล็อกของซินธิไซเซอร์ N PLL แบบเศษส่วนโดยใช้ตัวสะสมเพื่อปรับจำนวนตัวแบ่ง (แหล่งรูปภาพ: DigiKey)

รูปที่ 3: แผนภาพบล็อกของซินธิไซเซอร์ N PLL แบบเศษส่วนโดยใช้ตัวสะสมเพื่อปรับจำนวนตัวแบ่ง (แหล่งรูปภาพ: DigiKey)

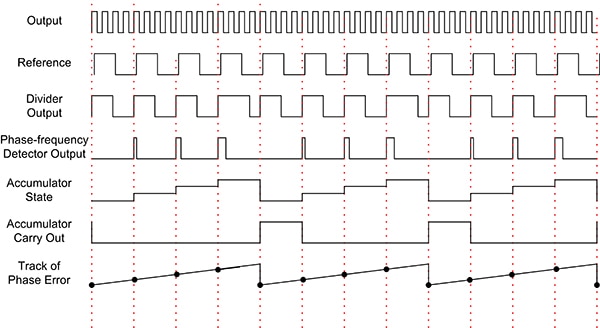

แอคคูมูเลเตอร์จะนับพัลส์เอาท์พุตจากตัวแบ่งและทุก ๆ M โดยที่ M คือโมดูลัสของตัวสะสมจะส่งออกบิตพกพาซึ่งจะเปลี่ยนอินพุตตัวแบ่ง รูปที่ 4 ยังคงเป็นตัวอย่างของการตั้งค่าตัวแบ่งเศษส่วนเป็น 4.25

รูปที่ 4: แผนภาพเวลาสำหรับซินธิไซเซอร์ N เศษส่วนโดยใช้ตัวสะสม (แหล่งรูปภาพ: DigiKey)

รูปที่ 4: แผนภาพเวลาสำหรับซินธิไซเซอร์ N เศษส่วนโดยใช้ตัวสะสม (แหล่งรูปภาพ: DigiKey)

แอคคูมูเลเตอร์ขับเคลื่อนด้วยเอาต์พุตที่แบ่งออกและนับโมดูโลสี่นั่นคือ M เท่ากับสี่ ทุกพัลส์ที่สี่จะสร้างเอาท์พุตพกพาซึ่งจะเพิ่มการนับตัวแบ่งทีละหนึ่ง ตัวสะสมจะรีเซ็ตและเริ่มนับใหม่อีกครั้ง การเพิ่มขึ้นของการตั้งค่าตัวแบ่งจะเปลี่ยนความถี่เอาต์พุตซึ่งส่งผลให้เกิดข้อผิดพลาดออฟเซ็ตเฟสสะสม การติดตามข้อผิดพลาดของเฟสแสดงค่าพัลส์ตามฟังก์ชันของเวลา

การตั้งค่าตัวแบ่งเฉลี่ยคือ 4.25 แต่เอาต์พุตของซินธิไซเซอร์เป็นเฟสมอดูเลตส่งผลให้โทนเสียงปลอมในเอาต์พุต เมื่อมองไปที่สถานะตัวสะสมจะเห็นได้ชัดว่ามันติดตามข้อผิดพลาดของเฟส สามารถใช้เพื่อลบการมอดูเลตดังแสดงในรูปที่ 5

รูปที่ 5: การใช้สถานะตัวสะสมที่แปลง D/A เพื่อยกเลิกการมอดูเลตเฟสเนื่องจากการแยกเศษ N (แหล่งรูปภาพ: DigiKey)

รูปที่ 5: การใช้สถานะตัวสะสมที่แปลง D/A เพื่อยกเลิกการมอดูเลตเฟสเนื่องจากการแยกเศษ N (แหล่งรูปภาพ: DigiKey)

สถานะตัวสะสมจะถูกแปลงเป็นอนาล็อกโดยตัวแปลงดิจิตอลเป็นอนาล็อก (D / A) และปรับขนาดและลบออกจากเอาต์พุตตัวตรวจจับความถี่เฟสเพื่อยกเลิกการมอดูเลตเฟสเนื่องจากการแยกเศษ N สิ่งนี้จะต้องทำด้วยความระมัดระวังเป็นอย่างยิ่ง หากสัญญาณการแก้ไขไม่ตรงกับข้อผิดพลาดของเฟสอย่างแม่นยำเสียงปลอมที่เอาต์พุตจะส่งผลให้

ป้อนโมดูเลเตอร์ sigma-delta

ระยะเวลาในตัวสะสมเป็นสาเหตุของเอาท์พุตปลอมจากซินธิไซเซอร์ หากตัวสะสมถูกแทนที่ด้วยโมดูเลเตอร์ sigma-delta ก็สามารถนำเทคนิคดิจิทัลมาปรับใช้เพื่อปรับจำนวนตัวแบ่งเพื่อลดการตอบสนองและเสียงรบกวนปลอม การเปลี่ยนนี้แสดงในรูปที่ 6

รูปที่ 6: การเปลี่ยนแอคคูมูเลเตอร์ด้วยโมดูเลเตอร์ sigma-delta ช่วยให้สามารถใช้เทคนิคดิจิทัลเพื่อปรับจำนวนตัวแบ่งที่แตกต่างกันเพื่อลดการตอบสนองปลอม (แหล่งรูปภาพ: DigiKey)

รูปที่ 6: การเปลี่ยนแอคคูมูเลเตอร์ด้วยโมดูเลเตอร์ sigma-delta ช่วยให้สามารถใช้เทคนิคดิจิทัลเพื่อปรับจำนวนตัวแบ่งที่แตกต่างกันเพื่อลดการตอบสนองปลอม (แหล่งรูปภาพ: DigiKey)

มีเทคนิคดิจิทัลทั่วไปสองอย่างที่ใช้ในโทโพโลยีการมอดูเลต sigma-delta ประการแรกเกี่ยวข้องกับการเพิ่มจำนวนตัวแบ่ง N ในช่วงค่าที่กว้างขึ้นเพื่อให้ตัวประกอบการหารเฉลี่ยจะสร้างค่าตัวแบ่งเศษส่วนที่ต้องการ สิ่งนี้จะลดสเปอร์เศษส่วนหลัก ซินธิไซเซอร์ที่ใช้ตัวสะสมจะแตกต่างกันไปตามจำนวนระหว่างสองสถานะ นี่เป็นวิธีการมอดูเลตลำดับแรก คำสั่งที่ n sigma-delta เศษส่วน PLL ปรับตัวนับ N ระหว่าง 2n ค่าที่แตกต่างกัน ตัวอย่างเช่นมอดูเลเตอร์ลำดับที่สามจะสลับระหว่างค่าตัวหารแปดค่าที่แตกต่างกันและโมดูเลเตอร์ลำดับที่สี่จะสลับระหว่างค่าตัวแบ่ง 16 ค่า

เทคนิคดิจิทัลที่สองซึ่งเรียกอีกอย่างว่าการแยกส่วนเกี่ยวข้องกับการสุ่ม 2n ลำดับเพื่อให้เป็น pseudorandom ในขณะที่ยังคงรักษาอัตราส่วนตัวแบ่งเศษส่วนโดยเฉลี่ยมันจะแปลงเดือยเศษส่วนให้เป็นสัญญาณรบกวนแบบสุ่มที่มีรูปร่างในลักษณะที่ PLL สามารถกรองได้

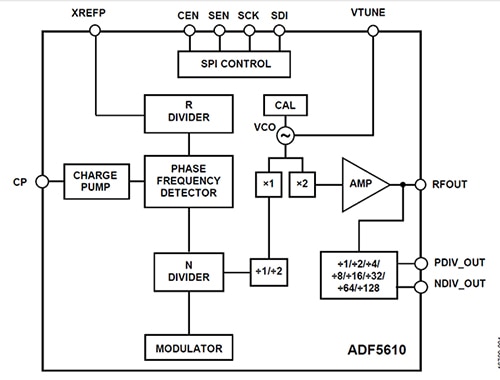

ซินธิไซเซอร์ N เศษส่วน sigma-delta ในเชิงพาณิชย์คือ ADF5610BCCZจาก Analog Devices ซึ่งเป็นซินธิไซเซอร์สัญญาณรบกวนต่ำ 0.57 เมกะเฮิรตซ์ (MHz) ถึง 14.6 GHz เศษส่วน N พร้อม VCO ในตัว (รูปที่ 7)

รูปที่ 7: แผนภาพบล็อกของอุปกรณ์อะนาล็อก ADF5610BCCZ ซึ่งรองรับการกำหนดค่าซินธิไซเซอร์ N เศษส่วนหรือจำนวนเต็ม (แหล่งรูปภาพ: Analog Devices)

รูปที่ 7: แผนภาพบล็อกของอุปกรณ์อะนาล็อก ADF5610BCCZ ซึ่งรองรับการกำหนดค่าซินธิไซเซอร์ N เศษส่วนหรือจำนวนเต็ม (แหล่งรูปภาพ: Analog Devices)

ADF5610 ต้องการออสซิลเลเตอร์อ้างอิงภายนอกและตัวกรองลูป มี VCO ในตัวที่มีความถี่พื้นฐาน 3650 MHz ถึง 7300 MHz ความถี่เหล่านี้จะเพิ่มเป็นสองเท่าภายในและถูกส่งไปยังพิน RFOUT มีเอาต์พุตที่แตกต่างกันที่ช่วยให้ความถี่ VCO สองเท่าหารด้วยปัจจัย 1, 2, 4, 8, 16, 32, 64 หรือ 128 ซึ่งช่วยให้สามารถสร้างความถี่เอาต์พุต RF ได้ต่ำถึง 57 MHz

ADF5610 ใช้โมดูเลเตอร์ sigma-delta ขั้นสูงที่มีโมดูลัสเศษส่วน 24 บิตซึ่งมีระดับปลอมที่ต่ำมาก เช่นเดียวกับซินธิไซเซอร์ทั้งหมดที่ใช้โมดูเลเตอร์ซิกมา - เดลต้าอุปกรณ์นี้ใช้เทคนิคการประมวลผลสัญญาณดิจิทัลเพื่อค้นหาอัตราส่วนตัวแบ่งเศษส่วนเฉลี่ยที่ต้องการ กระบวนการนี้โอเวอร์คล็อกที่อัตรา PFD ทำให้เกิดสัญญาณรบกวนการมอดูเลตเอาท์พุตที่เรียกว่า Quantization Noise พร้อมการตอบสนองความถี่สูง ตัวกรองลูปความถี่ต่ำภายนอกใช้เพื่อกรองสัญญาณรบกวนเชิงปริมาณนี้ให้อยู่ในระดับที่อยู่ใต้สัญญาณรบกวนเฟสของ VCO ดังนั้นจึงป้องกันไม่ให้เสียงรบกวนที่ก่อให้เกิดสัญญาณรบกวนเฟสโดยรวมของระบบ

ADF5610 ยังมีโหมดความถี่ที่แน่นอนสำหรับข้อผิดพลาดความถี่ 0 เฮิรตซ์ (Hz) โหมดนี้สามารถสร้างความถี่ที่แน่นอนระหว่างขั้นตอนขอบเขตจำนวนเต็ม N ที่อยู่ติดกันในขณะที่ยังคงใช้โมดูลัสสะสมเฟส 24 บิตเต็มรูปแบบ อีกทั้งยังบรรลุขั้นตอนความถี่ที่แน่นอนด้วยอัตราการเปรียบเทียบเครื่องตรวจจับเฟสสูงทำให้ PLL สามารถรักษาสัญญาณรบกวนเฟสที่ยอดเยี่ยมและประสิทธิภาพปลอมในโหมดนี้

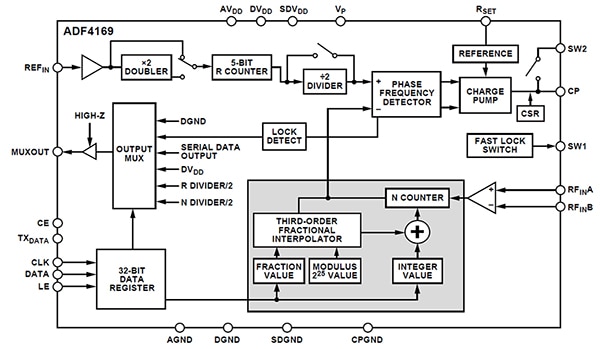

ADF4169CCPZ-RL7 จาก Analog Devices เป็นซินธิไซเซอร์ PLL อื่นที่สามารถกำหนดค่าเป็นจำนวนเต็ม N หรืออุปกรณ์ N เศษส่วน ทำงานด้วยแบนด์วิดท์ RF สูงถึง 13.5 GHz พร้อมการมอดูเลตและการสร้างรูปคลื่น ใช้อินพุตความถี่อ้างอิงภายนอก VCO และตัวกรองลูป มันมีโมดูเลเตอร์ sigma-delta ลำดับที่สามสำหรับการสังเคราะห์ N ที่เป็นเศษส่วนซึ่งสามารถปิดใช้งานได้ทำให้อุปกรณ์ทำงานในโหมด N จำนวนเต็ม (รูปที่ 8)

รูปที่ 8: อุปกรณ์อนาล็อก ADF4169CCPZ-RL7 ใช้โมดูเลเตอร์ sigma-delta ลำดับที่สาม (แหล่งรูปภาพ: Analog Devices)

รูปที่ 8: อุปกรณ์อนาล็อก ADF4169CCPZ-RL7 ใช้โมดูเลเตอร์ sigma-delta ลำดับที่สาม (แหล่งรูปภาพ: Analog Devices)

ซินธิไซเซอร์ ADF4158WCCPZ-RL7 มีไว้สำหรับใช้ในเรดาร์คลื่นต่อเนื่องแบบมอดูเลตความถี่ (FMCW) มีความสามารถในรูปแบบคลื่นมอดูเลตประเภทต่าง ๆ ในโดเมนความถี่รวมถึงฟันเลื่อยและทางลาดสามเหลี่ยม นี่เป็นคุณสมบัติพิเศษที่จำเป็นในการใช้งานเรดาร์

สรุป

อัตราข้อมูลที่เพิ่มขึ้นในบัสการสื่อสารแบบอนุกรมความเร็วสูงต้องการให้นักออกแบบมองข้ามซินธิไซเซอร์ดิจิทัลโดยตรงซึ่งทำงานได้ดีที่สุดที่ต่ำกว่า 3 GHz สำหรับโซลูชันนาฬิการะบบ ซินธิไซเซอร์ความถี่ที่ใช้ PLL โดยใช้โทโพโลยีจำนวนเต็ม N และเศษส่วน N ให้สัญญาณรบกวนต่ำที่เสถียรสำหรับนาฬิกาความถี่สูงการสื่อสารข้อมูลแบบอนุกรมและการใช้งานเรดาร์สำหรับความถี่สูงถึงหลายสิบกิกะเฮิรตซ์

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.