เหตุใดและอย่างไรจึงควรใช้ฟิลเตอร์ดิจิทัลสำหรับการแปลง อนาล็อกเป็นดิจิทัลที่มีความละเอียดสูง ความเร็วสูง

2021-03-17

ยังคงเป็นโลกอนาล็อก แต่อุปกรณ์อิเล็กทรอนิกส์ดิจิทัลก็แพร่หลายและด้วยเหตุผลที่ดี แม้ว่าดิจิทัลจะแก้ปัญหาหลายอย่างด้วยวิธีการแบบอัลกอริธึม แม้แต่อัลกอริธึมดิจิทัลที่ดีที่สุดก็มีข้อบกพร่องในการจัดการกับเอนทิตีในโลกแห่งความเป็นจริงที่มีอยู่ในโดเมนอนาล็อก โดยเฉพาะอย่างยิ่งในการใช้งานที่ต้องการการรับข้อมูลความเร็วสูงและความละเอียดสูง เช่น เครื่องมือวัด การควบคุมมอเตอร์ และระบบการรับข้อมูล

ปัญหาสำหรับนักออกแบบที่ต้องการจับภาพและประมวลผลสัญญาณในโลกแห่งความเป็นจริงดังกล่าวคือความจำเป็นในการเข้าสู่โดเมนดิจิทัลโดยเร็วที่สุดโดยไม่กระทบต่อข้อมูลสัญญาณนั้น โซลูชันนี้มาจากอัลกอริธึมการเฉลี่ยอย่างง่าย (เพื่อลดสัญญาณรบกวน) ที่มีฟิลเตอร์กรองความถี่ต่ำแบบอะนาล็อกส่วนหน้า (LPF) ด้วยเทคนิคเหล่านี้ อุปกรณ์ที่เหมาะสมสามารถให้ความละเอียดสูง การแปลงความเร็วสูงด้วยการกรองแบบอนาล็อกและดิจิทัลแบบออนบอร์ด

บทความนี้กล่าวถึงปัญหาที่เกี่ยวข้องกับการบรรลุการแปลงความละเอียดสูงและความเร็วสูงด้วยตัวแปลงอนาล็อกเป็นดิจิทัล (ADC) แบบอนาล็อกการประมาณค่าที่ต่อเนื่องกัน (SAR) โดยใช้ LPF แบบอนาล็อกและตัวกรองดิจิทัลเฉลี่ย และเหตุใดตัวกรองนี้จึงรวมกัน เป็นตัวเลือกที่ดีสำหรับการใช้งานส่วนใหญ่ จากนั้นจะแนะนำอุปกรณ์อนาล็อกAD7606C-18 SAR ADC แปดช่องสัญญาณและแสดงวิธีใช้ประโยชน์จากอัตราการแปลง 1 เมกะตัวอย่าง/วินาที (MSPS) อาร์เรย์ตัวแปลงตัวอย่างพร้อมกัน และฟังก์ชันตัวกรองดิจิทัลที่ยืดหยุ่น

บทความนี้ได้รวม AD7606C-18 เข้ากับ . เพื่อแสดงวิธีการบรรลุประสิทธิภาพโดยรวมที่ดีที่สุดADR4525 สัญญาณรบกวนต่ำมาก การอ้างอิงแรงดันไฟฟ้าที่มีความแม่นยำสูง รวมถึงจากอุปกรณ์อะนาล็อก เพื่อเพิ่มความแม่นยำของ SAR ที่จำเป็นสำหรับการแปลง 18 บิต

ตัวกรองอนาล็อกเทียบกับดิจิตอล

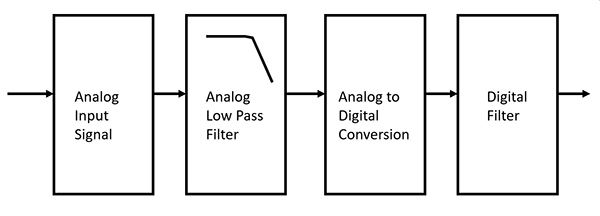

หากวิศวกรอนาล็อกและวิศวกรดิจิทัลพูดถึงตัวกรอง วิศวกรดิจิทัลอาจปลดตัวกรองอนาล็อกออกไป ซึ่งนี่อาจจะจะเป็นความผิดพลาด มาตรฐานการกรองที่มีการแปลงอนาล็อกเป็นดิจิทัล (A/D) ใด ๆ จะต้องมี LPF แบบอะนาล็อกก่อนตัวกรองดิจิทัล (รูปที่ 1)

รูปที่ 1: บล็อกไดอะแกรมของห่วงโซ่สัญญาณอนาล็อกถึงดิจิทัลพร้อมตัวกรองอนาล็อกก่อนตัวกรองดิจิทัล (แหล่งรูปภาพ: DigiKey)

รูปที่ 1: บล็อกไดอะแกรมของห่วงโซ่สัญญาณอนาล็อกถึงดิจิทัลพร้อมตัวกรองอนาล็อกก่อนตัวกรองดิจิทัล (แหล่งรูปภาพ: DigiKey)

หลังจากที่ LPF แบบอะนาล็อกลดความถี่ที่สูงกว่าแบนด์วิดท์ที่น่าสนใจแล้ว ADC จะแปลงสัญญาณเป็นคำดิจิทัล หลังจากนั้นตัวกรองดิจิทัลจะสามารถทำงานกับสัญญาณภายในแบนด์วิดท์ที่ต้องการได้

ตัวกรองอนาล็อกในสภาพแวดล้อมการรับข้อมูล

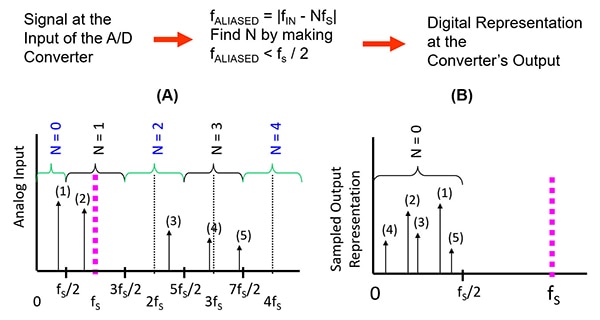

ความสำคัญของ LPF แบบอะนาล็อกนั้นชัดเจนที่เอาต์พุตของ ADC สัญญาณใด ๆ ที่ผ่าน ADC นั้นมีขนาดและความถี่ที่เกี่ยวข้อง ที่เอาต์พุตของ ADC ขนาดของสัญญาณจะยังคงเหมือนเดิมหากความถี่ของสัญญาณต่ำกว่าแบนด์วิดท์อินพุตของ ADC แม้ว่าการแปลง A/D จะรักษาขนาดสัญญาณไว้ แต่ก็ไม่เป็นความจริงสำหรับความถี่ของสัญญาณ สามารถสังเกตการเปลี่ยนแปลงความถี่ที่สูงกว่า ½ ของความถี่สุ่มตัวอย่างของ ADC, fSหรือที่เรียกว่าอัตราการสุ่มตัวอย่าง Nyquist (รูปที่ 2)

รูปที่ 2: ในกราฟ (A) การแสดงการแปลง Fourier อย่างรวดเร็ว (FFT) ของสัญญาณอินพุตมีส่วนประกอบความถี่ห้าส่วน หลังจากการแปลง A/D การแสดง FFT ในกราฟ (B) แสดงทั้งห้าสัญญาณที่เกิดขึ้นต่ำกว่าครึ่งหนึ่งของความถี่การสุ่มตัวอย่างของ ADC (fS) (แหล่งรูปภาพ: DigiKey)

รูปที่ 2: ในกราฟ (A) การแสดงการแปลง Fourier อย่างรวดเร็ว (FFT) ของสัญญาณอินพุตมีส่วนประกอบความถี่ห้าส่วน หลังจากการแปลง A/D การแสดง FFT ในกราฟ (B) แสดงทั้งห้าสัญญาณที่เกิดขึ้นต่ำกว่าครึ่งหนึ่งของความถี่การสุ่มตัวอย่างของ ADC (fS) (แหล่งรูปภาพ: DigiKey)

ในรูปที่ 2 พล็อต FFT ทั้งสองใช้ความถี่ลอการิทึมบนแกน x และแรงดันหรือขนาดเชิงเส้นบนแกน y ในกราฟ (A) การแสดงแทน FFT ของสัญญาณอนาล็อกจะแสดงสัญญาณอินพุตของ ADC ที่มีสัญญาณหรือสัญญาณรบกวนหลายตัวที่อยู่เหนือความถี่การสุ่มตัวอย่าง ADC หรือ fS/2

การเปรียบเทียบกราฟทั้งสองนี้จะเป็นประโยชน์ในการปฏิบัติตามสัญญาณ FFT ห้าแบบ หลังจากการแปลง ADC ขนาดของสัญญาณดั้งเดิมยังคงเท่าเดิม แต่ความถี่ที่สูงกว่าครึ่งหนึ่งของความถี่สุ่มตัวอย่างใน (A) จะ "พลิก" กลับด้านล่าง fS/2 ใน (B) ปรากฏการณ์นี้เรียกว่าสัญญาณแฝง (signal aliasing) เพื่อให้รับสัญญาณได้อย่างแม่นยำ อัตราการสุ่มตัวอย่าง fS ของ ADC ต้องมากกว่าสองเท่าของ fMAXโดยที่ fMAX เท่ากับแบนด์วิดท์ที่ใช้งานได้ของสัญญาณ ตามทฤษฎีบทการสุ่มตัวอย่าง Shannon-Nyquist

สามารถดูได้ว่า ADC ปลูกฝังสัญญาณรบกวนและสัญญาณที่ไม่ต้องการอย่างถาวรลงในสัญญาณเอาต์พุตดิจิทัลได้อย่างไร การเปลี่ยนแปลงนี้ทำให้ไม่สามารถบอกความแตกต่างระหว่างสัญญาณอินแบนด์และสัญญาณนอกแบนด์ที่เอาต์พุตของคอนเวอร์เตอร์

บางคนอาจคาดหวังว่าจะมีเส้นทางไปมาระหว่างการแสดง FFT ทั้งสองนี้ เมื่อการเปลี่ยนแปลงนี้เกิดขึ้นแล้ว จะไม่มีการย้อนกลับและยกเลิกการเปลี่ยนแปลงนั้น น่าเสียดายที่คณิตศาสตร์ไม่สนับสนุนการสลับไปมานี้

กลับไปที่การอภิปรายแบบอนาล็อก/ดิจิทัล: ตัวกรองดิจิทัลสามารถใช้การกรองค่าเฉลี่ย การตอบสนองต่อแรงกระตุ้น (FIR) หรือการตอบสนองต่อแรงกระตุ้นไม่สิ้นสุด (IIR) ได้อย่างไม่ต้องสงสัย และด้วยเหตุนี้จึงลดเสียงรบกวนของระบบ อย่างไรก็ตาม ตัวกรองดิจิทัลทุกตัวต้องมีการสุ่มตัวอย่างมากเกินไป (กระบวนการสุ่มตัวอย่างสัญญาณที่ความถี่การสุ่มตัวอย่างสูงกว่าอัตราข้อมูลเอาต์พุตขั้นสุดท้ายอย่างมาก) ซึ่งต้องใช้เวลา กำลัง และลดความเร็วในการสุ่มตัวอย่างของ ADC ฟังก์ชันตัวกรองและตัวแปลงดิจิทัลไม่เคยเอาชนะปรากฏการณ์สัญญาณแฝงได้ ดังนั้นทางที่ดีที่สุดคือการลดสัญญาณรบกวนความถี่ที่สูงขึ้นจากการโจมตีถึงแม้จะใช้ LPF ลำดับแรกแบบอนาล็อกเป็นพื้นฐานก็ตาม

ค่าเฉลี่ยตัวกรองดิจิทัล

SAR ADCs ปรับปรุงการวัดสัญญาณรบกวน DC ด้วยตัวกรองดิจิตอลเฉลี่ย ตัวกรองดิจิทัลโดยเฉลี่ยจะได้รับการแปลงหลายครั้งด้วยมาตราส่วนเวลาที่สอดคล้องกันเพื่อเพิ่มจำนวนบิต ผู้ใช้ ADC ใช้อัลกอริธึมการเฉลี่ยกับคอนโทรลเลอร์ โปรเซสเซอร์ หรือเอ็นจินการเฉลี่ยบนชิปที่รวบรวมตัวอย่างตัวแปลงหลายตัว กระบวนการหาค่าเฉลี่ย “ทำให้กลุ่มการแปลงราบรื่น” และปรับปรุงความละเอียดที่มีประสิทธิภาพด้วยการลดสัญญาณรบกวนของระบบ

การนำข้อมูลที่แปลงไปใช้อย่างราบรื่นนั้นเกี่ยวข้องกับการได้มาซึ่งสัญญาณหลายครั้งที่อัตราการสุ่มตัวอย่างคงที่และการหาค่าเฉลี่ยจำนวนตัวอย่างที่กำหนดไว้ล่วงหน้า กระบวนการหาค่าเฉลี่ยเป็นที่รู้จักกันดี ผลรวมของผลลัพธ์ ADC (ตัวอย่างที่ต่อเนื่องกัน x) หารด้วยจำนวนตัวอย่าง (N) ได้ค่าเฉลี่ย (สมการที่ 1)

![]() สมการที่ 1

สมการที่ 1

กระบวนการนี้ลดอัตราการส่งข้อมูลออกด้วยปัจจัย N แต่เพิ่มเวลาในการชำระของระบบ

ค่าเบี่ยงเบนมาตรฐานของค่าเฉลี่ยตัวอย่างที่มีสัญญาณรบกวน (σavg) คือค่าเบี่ยงเบนมาตรฐานของสัญญาณดั้งเดิม (σsig) หารด้วยรากที่สองของ N (สมการที่ 2)

![]() สมการ 2

สมการ 2

ตัวอย่างที่ต่อเนื่องกัน ซึ่งรวมถึงสัญญาณรบกวนที่ไม่สัมพันธ์กัน จะส่งผลให้มีการลดสัญญาณรบกวนมากขึ้นในค่าเฉลี่ยของสัญญาณคงที่ ค่าเฉลี่ยตัวอย่างที่ต่อเนื่องกันแต่ละรายการจะทำให้อัตราส่วนสัญญาณต่อสัญญาณรบกวน (SNR) ดีขึ้นหากสัญญาณเป็น DC และส่วนประกอบสัญญาณรบกวนเป็นแบบสุ่ม

การปรับปรุง SNR เป็นสัดส่วนกับรากที่สองของจำนวนตัวอย่างเฉลี่ย ตัวอย่างสัญญาณ DC เฉลี่ยสี่ตัวอย่าง (41 ) จะเพิ่มความละเอียดที่มีประสิทธิภาพของคอนเวอร์เตอร์ขึ้นหนึ่งโดยที่ SNR เพิ่มขึ้น 6 เดซิเบล (dB) A 16 หรือ 42 ค่าเฉลี่ยของตัวอย่างจะเพิ่มความละเอียดที่มีประสิทธิภาพขึ้น 2 และ SNR 12 dB ด้วยตรรกะนี้ ขนาดกลุ่ม 4N จะเพิ่มจำนวนบิตที่มีประสิทธิภาพจากการแปลงโดย N ทำให้สัญญาณรบกวนของระบบเป็นศูนย์และค่า SNR เป็นอนันต์

ความแปรปรวนของ Allan

แน่นอนว่าค่า SNR ที่เท่ากับอนันต์นั้นไม่เป็นจริง ในโลกแห่งความเป็นจริง การได้มาซึ่งจำนวนตัวอย่างที่ต้องการนั้นต้องใช้เวลา ซึ่งในระหว่างนั้นระบบอาจเปลี่ยนแปลงในแง่ของระดับการเคลื่อนตัว

ความแปรปรวนของ Allan หรือที่เรียกว่าความแปรปรวนสองตัวอย่าง จะวัดความเสถียรของความถี่ในนาฬิกา ออสซิลเลเตอร์ ADC และแอมพลิฟายเออร์โดยแสดงการเปลี่ยนแปลงของสัญญาณรบกวนเมื่อจำนวนตัวอย่างที่ใช้ในการหาค่าเฉลี่ยของสัญญาณเพิ่มขึ้น เครื่องมือวิเคราะห์ทางสถิติความแปรปรวนของ Allan จะกำหนดจำนวนตัวอย่างสูงสุดที่ต้องการซึ่งจะเหมาะสมที่สุดสำหรับระบบใดระบบหนึ่ง ดังนั้นจึงประเมินความเสถียรโดยชี้ให้เห็นความเบี่ยงเบนของความถี่หรือผลกระทบของอุณหภูมิ

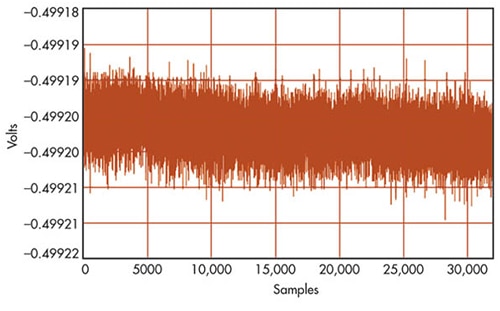

ตัวอย่างเช่น ข้อมูลในระบบจาก ADC เมื่อเวลาผ่านไปสามารถแสดงการเปลี่ยนแปลงได้ดังแสดงในรูปที่ 3

รูปที่ 3: จุดข้อมูลเอาท์พุต ADC 30,000 จุดที่จับได้ตลอดเก้านาทีแสดงการเบี่ยงเบนเล็กน้อยในข้อมูลในช่วงเวลานั้น ทำให้เกิดการลดลงในการคำนวณความแปรปรวนของ Allan (ที่มาของภาพ: การออกแบบทางอิเล็กทรอนิกส์)

รูปที่ 3: จุดข้อมูลเอาท์พุต ADC 30,000 จุดที่จับได้ตลอดเก้านาทีแสดงการเบี่ยงเบนเล็กน้อยในข้อมูลในช่วงเวลานั้น ทำให้เกิดการลดลงในการคำนวณความแปรปรวนของ Allan (ที่มาของภาพ: การออกแบบทางอิเล็กทรอนิกส์)

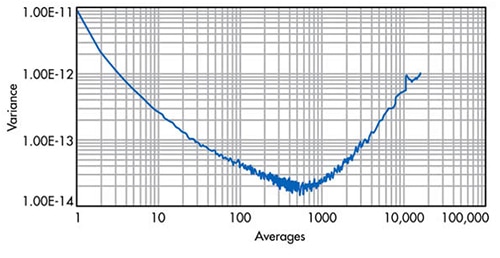

อัลกอริธึมความแปรปรวนใช้ค่าเฉลี่ยที่ยาวขึ้นและยาวขึ้นหลายแบทช์ และประเมินสัญญาณรบกวนที่เป็นผลของแต่ละแบทช์ (รูปที่ 4)

รูปที่ 4: การคำนวณความแปรปรวน Allan ประยุกต์สำหรับจุดข้อมูลในรูปที่ 3 ที่ค่าเฉลี่ย 500 จุด ระบบ ADC โดยเฉพาะนี้จะได้รับ 4.48 บิตหรือเพิ่มขึ้น 27 dB SNR (ที่มาของภาพ: การออกแบบทางอิเล็กทรอนิกส์)

รูปที่ 4: การคำนวณความแปรปรวน Allan ประยุกต์สำหรับจุดข้อมูลในรูปที่ 3 ที่ค่าเฉลี่ย 500 จุด ระบบ ADC โดยเฉพาะนี้จะได้รับ 4.48 บิตหรือเพิ่มขึ้น 27 dB SNR (ที่มาของภาพ: การออกแบบทางอิเล็กทรอนิกส์)

รูปที่ 4 แสดงให้เห็นว่าความแปรปรวนขั้นต่ำของจุดข้อมูลของระบบนี้เกิดขึ้นที่ค่าเฉลี่ยเอาต์พุต ADC ประมาณ 500 ค่า ซึ่งเป็นจำนวนเฉลี่ยของตัวอย่างที่เหมาะสมที่สุดสำหรับการลดสัญญาณรบกวน ที่ค่าเฉลี่ย 500 จุด ระบบ ADC นี้รับ 4.48 บิตหรือเพิ่มขึ้น 27 dB SNR ก่อนหน้าและเกินค่าเฉลี่ยที่ 500 ผลลัพธ์จะแย่ลงในรูปที่ 4 เนื่องจากความเบี่ยงเบนของข้อมูลกลายเป็นปัจจัยที่ใหญ่ขึ้น ตัวแปรที่ส่งผลต่อการคำนวณความแปรปรวนของ Allan ได้แก่ เวลา ความเสถียรของสัญญาณ การเลื่อน การแปรผันของแหล่งจ่ายไฟ และอายุผลิตภัณฑ์ หากใช้ตัวกรองการเฉลี่ยดิจิทัล ควรประเมินระบบโดยรวมด้วยเครื่องมือความแปรปรวนของ Allan

โซลูชันในโลกแห่งความเป็นจริง

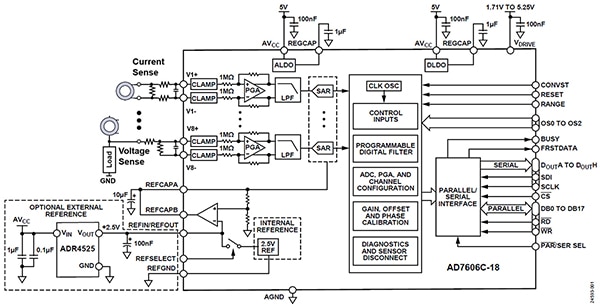

ตัวแปลง SAR สามารถนำเสนอเครื่องขยายสัญญาณแบบตั้งโปรแกรมได้ (PGA) และฟังก์ชันตัวกรองแบบดิจิตอลเพื่อเพิ่มความละเอียดที่มีประสิทธิภาพและแรงดันไฟฟ้าบิตที่มีนัยสำคัญน้อยที่สุด (LSB) ตัวอย่างเช่น AD7606C-18 ของ Analog Devices คือ 18 บิต, 1 MSPS สุ่มตัวอย่างพร้อมกัน, ระบบเก็บข้อมูล A/D (DAS) ที่มีแปดช่องสัญญาณ แต่ละช่องมีการป้องกันแคลมป์อินพุตแบบอะนาล็อก, PGA, LPF และ 18 บิต สสวท.

อุปกรณ์ยังมีบัฟเฟอร์อินพุตแบบอะนาล็อกที่มีอิมพีแดนซ์อินพุต 1 เมกะโอห์ม (MW) และการกำหนดค่าแรงดันไฟฟ้าอินพุตแบบขั้วเดี่ยวแบบขั้วเดี่ยวและแบบขั้วเดียวที่ตั้งโปรแกรมได้ AD7606C-18 ช่วยให้สามารถเชื่อมต่อเซ็นเซอร์อินพุทอิสระหรือช่องสัญญาณได้แปดแบบ

ตัวกรองดิจิตอลของ AD7606C-18 มีโหมดการสุ่มตัวอย่างเกินซึ่งเฉลี่ยตัวอย่างที่ซ้ำกันตั้งแต่ 1 ถึง 256 (44) ตามเครื่องมือความแปรปรวนของ Allan คุณลักษณะการสุ่มตัวอย่างเกินนี้ช่วยปรับปรุงประสิทธิภาพเสียงที่เอาต์พุตดิจิตอลของตัวแปลง ADR4525 สัญญาณรบกวนต่ำ แรงดันอ้างอิงความแม่นยำ 2.5 โวลต์ช่วยเสริมระบบ AD7606C-18 DAS ด้วยค่าสัมประสิทธิ์อุณหภูมิสูงสุด 1 ส่วนต่อล้านต่อองศาเซลเซียส (ppm/°C) และ 1 ไมโครโวลต์ (mV) สัญญาณรบกวนจากเอาต์พุตทั่วไปสูงสุดถึงจุดสูงสุด (รูปที่ 5)

รูปที่ 5: AD7606C-18 SAR-ADC พร้อมการอ้างอิงแรงดันไฟฟ้าที่แม่นยำ ADR4525 2.5 โวลต์ ตัวเหนี่ยวนำที่มี LPF ลำดับแรกบนช่องสัญญาณอินพุต V1 ถึง V8 สุ่มตัวอย่างทั้งแปดช่องพร้อมกัน (แหล่งรูปภาพ: Analog Devices)

รูปที่ 5: AD7606C-18 SAR-ADC พร้อมการอ้างอิงแรงดันไฟฟ้าที่แม่นยำ ADR4525 2.5 โวลต์ ตัวเหนี่ยวนำที่มี LPF ลำดับแรกบนช่องสัญญาณอินพุต V1 ถึง V8 สุ่มตัวอย่างทั้งแปดช่องพร้อมกัน (แหล่งรูปภาพ: Analog Devices)

ดังรูปที่ 5 แสดงให้เห็นว่าอาร์เรย์ SAR อิมพีแดนซ์อินพุตสูงประเภทนี้สามารถเชื่อมต่อโดยตรงกับเซ็นเซอร์ลบด้วยแอมพลิฟายเออร์ภายนอกทั่วไป และระยะเกนของเซ็นเซอร์ภายนอกก็ไม่จำเป็นเช่นกัน พร้อมกันนี้ ตัวแปลง SAR มีระยะ PGA และ LPF ภายในที่ให้การประมวลผลสัญญาณ ตามด้วยตัวกรองดิจิตอลโดยเฉลี่ยเพื่อลดสัญญาณรบกวนเพิ่มเติมโดยให้ความละเอียดที่มีประสิทธิภาพสูงขึ้น DAS ดังกล่าวสามารถเสนอความละเอียดที่มีประสิทธิภาพ 17.1 บิตด้วยความเร็วในการแปลง 3.9 กิโลตัวอย่างต่อวินาที (ksps) อีกด้านหนึ่งของสเปกตรัมความเร็วในการแปลง อุปกรณ์นี้มีความละเอียดที่มีประสิทธิภาพ 15 บิตพร้อมความเร็วในการแปลง 1 MSPS

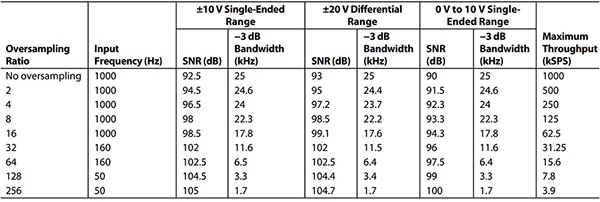

ความเร็วในการแปลงที่เร็วที่สุดของ AD7606C-18 คือ 1 MSPS โดยมีการสุ่มตัวอย่างเกินเท่ากับหนึ่ง หากการสุ่มตัวอย่างช่องสัญญาณเกินของตัวแปลงเป็นสอง หรือเฉลี่ยตัวอย่างช่องสองครั้ง ความเร็วในการแปลงจะเป็นครึ่งหนึ่งของความเร็วในการแปลงสูงสุดที่ 500 ksp สำหรับการสุ่มตัวอย่างเกินเท่ากับสี่หรือ 41 ตามจำนวนตัวอย่างเฉลี่ย ความเร็วในการแปลงของแชนเนลนั้นคือ 250 ksp เป็นต้น สำหรับแต่ละช่องสัญญาณแปดช่อง ระบบที่มีค่าการสุ่มตัวอย่างเกิน 256 ให้ช่วง ±10 โวลต์ single-ended ความละเอียด 17.1 บิตที่มีประสิทธิภาพ (105 dB SNR) ด้วยความเร็วในการแปลง 3.9 ksps (ตารางที่ 1)

ตารางที่ 1: ประสิทธิภาพการสุ่มตัวอย่างมากเกินไป โหมดแบนด์วิดท์ต่ำของ AD7606C-18 (ที่มาของตาราง: Analog Devices)

ตารางที่ 1: ประสิทธิภาพการสุ่มตัวอย่างมากเกินไป โหมดแบนด์วิดท์ต่ำของ AD7606C-18 (ที่มาของตาราง: Analog Devices)

สูตรการแปลง SNR ต่อประสิทธิผล (จำนวนบิตที่มีประสิทธิผลหรือ ENOB) แสดงในสมการที่ 3

![]() สมการ 3

สมการ 3

ในส่วนอื่น ๆ ของสเปกตรัมความเร็วในการแปลงด้วยปัจจัยการสุ่มตัวอย่างเกินที่ 1 อุปกรณ์นี้ให้ความละเอียดที่มีประสิทธิภาพ 15 บิต (92.5 dB SNR) พร้อมความเร็วในการแปลง 1 MSPS (ตารางที่ 1)

มีการปรับปรุงเพิ่มเติมที่ AD7606C-18 ได้นำเสนอ เนื่องจากมี SAR ADC แยกจากกันแปดตัวบนชิป ทั้งแปดช่องจึงมีฟังก์ชันสุ่มตัวอย่างพร้อมกัน ด้วยฟังก์ชันนี้ คุณสามารถใช้ตัวกรองดิจิทัลเพื่อให้ได้ความละเอียดสูงหรือความเร็วสูงพร้อมกันในทุกช่องสัญญาณ นอกจากนี้ ทุกช่องสัญญาณยังมีความสามารถในการสอบเทียบและวินิจฉัย

ตัวอย่างเช่น การปรับเทียบเฟสของระบบของ AD7606C-18 จะตรวจจับความไม่ตรงกันของตัวกรองอินพุตแบบแยกส่วน คุณลักษณะที่มีค่านี้ระบุความไม่ตรงกันบนส่วนประกอบที่ไม่ต่อเนื่องหรือในเซ็นเซอร์ที่ใช้ซึ่งอาจทำให้เฟสไม่ตรงกันระหว่างช่องสุ่มตัวอย่างพร้อมกัน โหมดซอฟต์แวร์ของอุปกรณ์จะชดเชยเฟสที่ไม่ตรงกันในแต่ละช่องสัญญาณโดยการหน่วงเวลาการสุ่มตัวอย่างแต่ละช่องในทันที

การสอบเทียบที่ได้รับจากระบบจะตรวจจับตัวต้านทานที่ไม่ตรงกันของตัวกรองอินพุตแบบแยกส่วน ความสามารถนี้ช่วยเอาชนะตัวต้านทานภายนอกที่ไม่ตรงกัน โหมดซอฟต์แวร์จะชดเชยข้อผิดพลาดเกนบนพื้นฐานต่อช่องสัญญาณโดยการเขียนค่าตัวต้านทานแบบอนุกรมที่ใช้บนรีจิสเตอร์ที่เกี่ยวข้อง

การสอบเทียบออฟเซ็ตของระบบรองรับการชดเชยสัญญาณอินพุตระหว่างกิจกรรมการปรับเทียบ ซอฟต์แวร์สามารถปรับออฟเซ็ตของเซ็นเซอร์ภายนอกของแต่ละช่องสัญญาณหรือค่าชดเชยที่ไม่ตรงกันของตัวต้านทานภายนอกใด ๆ ก็ได้

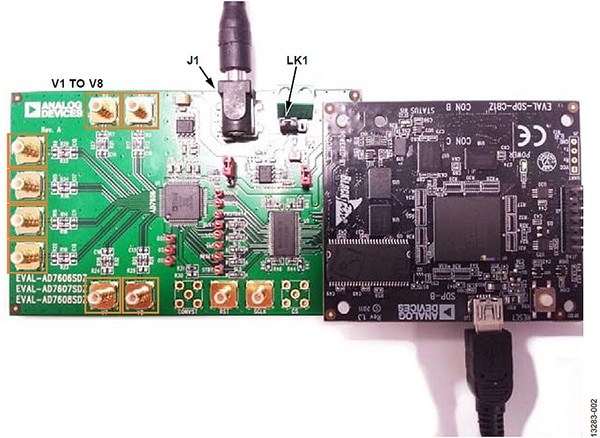

สำหรับการใช้งานเฉพาะ EVAL-AD7606SDZ บอร์ดสำหรับ AD7606 มีซอฟต์แวร์เพื่อช่วยในการประเมินอุปกรณ์ด้วยการเขียนโปรแกรมอุปกรณ์ ตลอดจนรูปคลื่น ฮิสโตแกรม และการจับ FFT (รูปที่ 6)

รูปที่ 6: บอร์ดประเมินผล AD7606 (ซ้าย) ที่เชื่อมต่อกับบอร์ดแพลตฟอร์มสาธิตระบบ (SDP) (ขวา) ซึ่งช่วยให้ควบคุมบอร์ดประเมินผลผ่านพอร์ต USB ของพีซีได้ (แหล่งรูปภาพ: Analog Devices)

รูปที่ 6: บอร์ดประเมินผล AD7606 (ซ้าย) ที่เชื่อมต่อกับบอร์ดแพลตฟอร์มสาธิตระบบ (SDP) (ขวา) ซึ่งช่วยให้ควบคุมบอร์ดประเมินผลผ่านพอร์ต USB ของพีซีได้ (แหล่งรูปภาพ: Analog Devices)

ซอฟต์แวร์ของบอร์ดประเมินผลทำให้ผู้ใช้สามารถกำหนดค่าค่าการสุ่มตัวอย่างเกินขอบเขต ช่วงอินพุต จำนวนตัวอย่าง และการเลือกช่องสัญญาณที่ใช้งานอยู่ได้ นอกจากนี้ ซอฟต์แวร์นี้ยังทำให้สามารถบันทึกและเปิดไฟล์ข้อมูลทดสอบได้อีกด้วย

สรุป

แม้จะเปลี่ยนไปใช้ดิจิทัล แต่ก็ยังเป็นโลกอนาล็อก และนักออกแบบต้องการอุปกรณ์อิเล็กทรอนิกส์แบบอนาล็อกเป็นศูนย์กลางเพื่อแก้ปัญหาการแปลงที่มีความละเอียดสูงและความเร็วสูง ดังที่แสดงไว้ การผสมผสานอย่างง่ายของ LPF แบบอนาล็อกและตัวกรองการเฉลี่ยดิจิทัล ใช้งานด้วยจำนวนตัวอย่างเฉลี่ยที่เหมาะสม จะช่วยเพิ่มประสิทธิภาพการทำงานของตัวแปลง 1 MSPS SAR ได้อย่างมาก

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.