วิธีใช้ FPGA SoC สำหรับระบบเรียลไทม์แบบฮาร์ดที่ปลอดภัยและมีการเชื่อมต่อ

Contributed By DigiKey's North American Editors

2023-02-16

ระบบย่อยเกทอาร์เรย์ลอจิกแบบโปรแกรมได้ (FPGA), ไมโครคอนโทรลเลอร์ยูนิต (MCU) RISC-V ที่รองรับ Linux, สถาปัตยกรรมหน่วยความจำขั้นสูง และอินเทอร์เฟซการสื่อสารประสิทธิภาพสูงเป็นเครื่องมือสำคัญสำหรับนักออกแบบ โดยเฉพาะอย่างยิ่งสำหรับนักออกแบบระบบที่มีการเชื่อมต่ออย่างปลอดภัย ระบบที่มีความสำคัญต่อความปลอดภัย และระบบที่กำหนดได้ที่หลากหลาย เช่น ปัญญาประดิษฐ์ (AI) และแมชชีนเลิร์นนิง (ML)

อย่างไรก็ตาม การรวมองค์ประกอบที่หลากหลายเหล่านั้นเข้ากับระบบที่ปลอดภัย เชื่อมต่อ และกำหนดได้อาจเป็นกิจกรรมที่ท้าทายและใช้เวลานาน เช่นเดียวกับการวางโครงข่ายความเร็วสูงสำหรับองค์ประกอบต่าง ๆ ของระบบ นักออกแบบจำเป็นต้องมีหน่วยจัดการหน่วยความจำ หน่วยป้องกันหน่วยความจำ ความสามารถในการบู๊ตอย่างปลอดภัย และตัวรับส่งสัญญาณระดับกิกะบิตสำหรับการเชื่อมต่อความเร็วสูง โดยการออกแบบจะต้องมีการจัดการพลังงานทั้งแบบแอคทีฟและแบบคงที่ รวมถึงการควบคุมกระแสพุ่งเข้า การออกแบบบางอย่างจะต้องใช้งานในช่วงเชิงพาณิชย์ที่เพิ่มขึ้นโดยมีค่าอุณหภูมิที่จุดต่อ (TJ) ตั้งแต่ 0°C ถึง +100°C ในขณะที่ระบบในสภาพแวดล้อมอุตสาหกรรมมี TJ ตั้งแต่ -40°C ถึง +100°C

เพื่อรับมือกับความท้าทายเหล่านี้และความท้าทายอื่นๆ นักออกแบบสามารถหันไปใช้อุปกรณ์ FPGA System-on-chip (SoC) ที่รวมการใช้พลังงานต่ำ ประสิทธิภาพเชิงความร้อน และการรักษาความปลอดภัยระดับที่ใช้งานงานความมั่นคงสำหรับระบบอัจฉริยะ มีการเชื่อมต่อ และกำหนดได้

บทความนี้ศึกษาสถาปัตยกรรมของ FPGA SoC และวิธีการสนับสนุนการออกแบบระบบที่มีการเชื่อมต่อและกำหนดได้ที่มีประสิทธิภาพ จากนั้นจึงนำเสนอประสิทธิภาพการประมวลผลของ EEMBC CoreMark-Pro เทียบกับเกณฑ์มาตรฐานการใช้พลังงาน พร้อมกับมุมมองของประสิทธิภาพเกณฑ์มาตรฐานของตัวอย่าง FPGA SoC ซึ่งจะพิจารณาว่าการรักษาความปลอดภัยรวมอยู่ใน FPGA SoC ได้อย่างไรและอธิบายรายละเอียดตัวอย่าง FPGA SoC จาก Microchip Technology พร้อมด้วยแพลตฟอร์มการพัฒนา เพื่อเร่งกระบวนการออกแบบ ปิดท้ายด้วยตัวอย่างบอร์ดเสริมจาก MikroElektronika ที่สามารถใช้ในการปรับใช้อินเทอร์เฟซการสื่อสารที่หลากหลาย เช่นเดียวกับความสามารถในการระบุตำแหน่งของระบบนำทางด้วยดาวเทียม (GNSS)

SoC สร้างขึ้นจาก FPGA Fabric

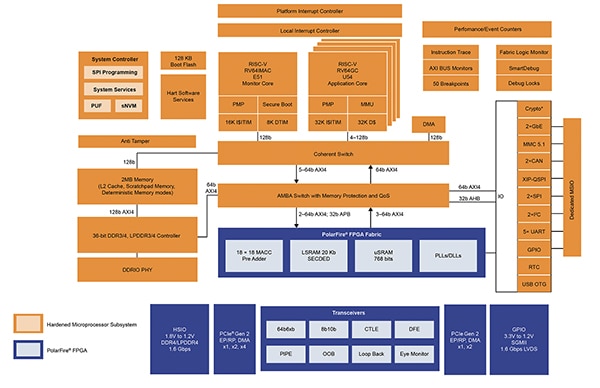

'ชิป' สำหรับ SoC นี้เป็น FPGA Fabric ที่มีองค์ประกอบของระบบ ตั้งแต่ FPGA ไปจนถึงระบบย่อย RISC-V MCU ที่สร้างขึ้นด้วยลอจิก FPGA แบบฮาร์ด ระบบย่อย MCU ประกอบด้วยคลัสเตอร์ RISC-V MCU แบบ Quad-Core, แกนตรวจสอบ RISC-V, ตัวควบคุมระบบ และระบบย่อยหน่วยความจำเชิงกำหนดระดับ 2 (L2) โดย FPGA ใน SoC เหล่านี้ประกอบด้วยองค์ประกอบลอจิกสูงสุด 460 K ตัวรับส่งสัญญาณสูงสุด 12.7 กิกะบิตต่อวินาที (Gbps) และบล็อกอินพุต/เอาต์พุต (I/O) อื่น ๆ รวมถึง I/O อเนกประสงค์ (GPIO) และ ระบบบัสแบบพีซีไอเอกเพรส (Peripheral Component Interconnect Express, PCIe)2 ซึ่งสถาปัตยกรรมโดยรวมได้รับการออกแบบเพื่อความน่าเชื่อถือ ประกอบด้วยการแก้ไขข้อผิดพลาดครั้งเดียวและการตรวจจับข้อผิดพลาดสองครั้ง (SECDED) ในหน่วยความจำทั้งหมด, การวิเคราะห์พลังงานที่แตกต่างกัน (DPA), การป้องกันหน่วยความจำทางกายภาพ และหน่วยความจำแฟลชบูต 128 กิโลบิต (Kbits) (รูปที่ 1)

รูปที่ 1: องค์ประกอบทั้งหมดใน FPGA SoC นี้ รวมถึงระบบย่อย RISC-V ถูกนำไปใช้งานบน FPGA Fabric (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 1: องค์ประกอบทั้งหมดใน FPGA SoC นี้ รวมถึงระบบย่อย RISC-V ถูกนำไปใช้งานบน FPGA Fabric (แหล่งที่มาภาพ: Microchip Technology)

Microchip นำเสนอระบบนิเวศ Mi-V (อ่านว่า “my Five”) ของเครื่องมือและทรัพยากรการออกแบบของบุคคลที่สาม เพื่อสนับสนุนการนำระบบ RISC-V ไปใช้ ซึ่งสร้างขึ้นเพื่อเพิ่มความเร็วในการปรับใช้สถาปัตยกรรมชุดคำสั่ง RISC-V (ISA) สำหรับแกน RISC-V แบบฮาร์ดคอร์และ RISC-V แบบซอฟต์คอร์ องค์ประกอบของระบบนิเวศ Mi-V ประกอบไปด้วยการเข้าถึง:

- ใบอนุญาตทรัพย์สินทางปัญญา (IP)

- ฮาร์ดแวร์

- ระบบปฏิบัติการและมิดเดิลแวร์

- ดีบักเกอร์ คอมไพเลอร์ และบริการออกแบบ

RISC-V MCU แบบฮาร์ดใน FPGA SoC มีความสามารถในการดีบักหลายอย่าง เช่น อินเทอร์เฟซขยายขั้นสูง (AXI) แบบพาสซีฟรันไทม์ที่กำหนดค่าได้ และการติดตามคำสั่ง AXI ช่วยให้นักออกแบบสามารถตรวจสอบข้อมูลที่กำลังเขียนหรืออ่านจากหน่วยจำต่าง ๆ และทราบเมื่อมีการเขียนหรืออ่าน

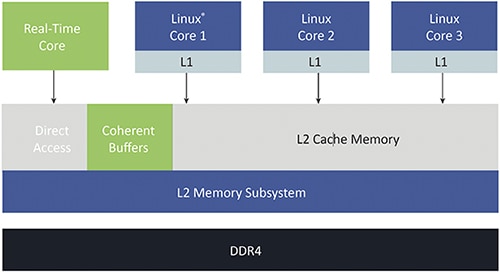

ระบบย่อย RISC-V MCU ใช้ไปป์ไลน์ตามลำดับงานเดียวห้าระดับ โดยไม่เสี่ยงต่อช่องโหว่ Spectre หรือ Meltdown ที่สามารถสร้างความเสียหายให้กับสถาปัตยกรรมที่ไม่อยู่ในลำดับได้ โดย MCU ทั้งห้าเชื่อมโยงกับระบบย่อยหน่วยความจำ รองรับการผสมผสานระหว่างระบบเรียลไทม์ในโหมดการประมวลผลหลายตัว (AMP) และ Linux ความสามารถของระบบย่อย RISC-V ได้แก่ (รูปที่ 2):

- เรียกใช้ Linux และการดำเนินการแบบเรียลไทม์

- กำหนดค่า L1 และ L2 เป็นหน่วยความจำเชิงกำหนด

- ระบบย่อยหน่วยความจำ DDR4

- ปิด/เปิดใช้ตัวคาดการณ์การแยกไปทำงาน

- การดำเนินการไปป์ไลน์ตามลำดับ

รูปที่ 2: ระบบย่อย RISC-V ประกอบด้วยโปรเซสเซอร์และองค์ประกอบหน่วยความจำหลายตัว (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 2: ระบบย่อย RISC-V ประกอบด้วยโปรเซสเซอร์และองค์ประกอบหน่วยความจำหลายตัว (แหล่งที่มาภาพ: Microchip Technology)

ประมวลผลได้มากขึ้นโดยใช้พลังงานลดลง

นอกเหนือจากประโยชน์ด้านการทำงานของระบบ ซึ่งรวมถึงการรองรับการประมวลผลแบบเรียลไทม์อย่างหนักแล้ว FPGA SoC เหล่านี้ยังประหยัดพลังงานอีกด้วย เกณฑ์มาตรฐาน EEMBC CoreMark-PRO เป็นมาตรฐานอุตสาหกรรมสำหรับการเปรียบเทียบประสิทธิภาพและประสิทธิภาพของ MCU ในระบบฝังตัว ซึ่งได้รับการออกแบบมาโดยเฉพาะเพื่อประเมินประสิทธิภาพฮาร์ดแวร์และใช้แทนที่เกณฑ์มาตรฐาน Dhrystone

ปริมาณงาน CoreMark-PRO มีลักษณะการทำงานที่หลากหลาย การขนานในระดับการไหลของแต่ละคำสั่ง และการใช้หน่วยความจำตามปริมาณงานทศนิยมสี่ตำแหน่งและปริมาณงานจำนวนเต็มทั่วไปห้ารายการ ปริมาณงานทศนิยมประกอบด้วยรูทีนพีชคณิตเชิงเส้นที่ได้มาจาก LINPACK, การแปลงฟูเรียร์แบบเร็ว, อัลกอริทึมโครงข่ายประสาทเทียมสำหรับการประเมินรูปแบบ และเกณฑ์มาตรฐาน Livermore loops เวอร์ชันปรับปรุง การบีบอัด JPEG, ตัวแยกวิเคราะห์ XML, การบีบอัด ZIP และอัลกอริธึมแฮชที่ปลอดภัย 256 บิต (SHA-256) เป็นพื้นฐานของปริมาณงานจำนวนเต็ม

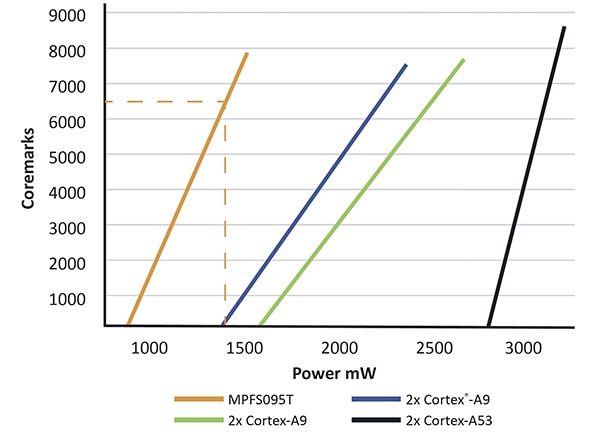

โมเดล MPFSO95T ของ FPGA SoC เหล่านี้ เช่น MPFS095TL-FCSG536E สามารถให้ได้ถึง 6,500 Coremarks ที่ 1.3 วัตต์ (รูปที่ 3)

รูปที่ 3: MPFS095T FPGA SoC (เส้นสีส้ม) ให้ 6500 Coremarks ที่ 1.3 วัตต์ (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 3: MPFS095T FPGA SoC (เส้นสีส้ม) ให้ 6500 Coremarks ที่ 1.3 วัตต์ (แหล่งที่มาภาพ: Microchip Technology)

ข้อควรพิจารณาด้านความปลอดภัย

การใช้งานแบบเรียลไทม์ที่เน้นความปลอดภัยและเข้มงวดสำหรับ FPGA SoC เหล่านี้ต้องการการรักษาความปลอดภัยที่แข็งแกร่ง นอกเหนือจากประสิทธิภาพการใช้พลังงานสูงและความสามารถในการประมวลผลที่ทรงพลัง ฟังก์ชันความปลอดภัยพื้นฐานของ FPGA SoC เหล่านี้รวมถึงการเขียนโปรแกรมบิตสตรีมที่ต้านทานการวิเคราะห์พลังงานที่แตกต่างกัน (DPA) ตัวสร้างตัวเลขสุ่มอย่างแท้จริง (TRNG) และฟังก์ชันที่ไม่สามารถโคลนได้จริง (PUF) นอกจากนี้ยังรวมถึงการบู๊ตแบบปลอดภัยแบบมาตรฐานและแบบที่ผู้ใช้กำหนด การป้องกันหน่วยความจำทางกายภาพที่มีการจำกัดการเข้าถึงหน่วยความจำที่เกี่ยวข้องกับสถานะสิทธิ์ของเครื่อง รวมถึงเครื่อง ผู้ควบคุม หรือโหมดผู้ใช้ และป้องกันจากการโจมตีของ Meltdown และ Spectre

การรักษาความปลอดภัยเริ่มต้นด้วยการจัดการซัพพลายเชนที่ปลอดภัย รวมถึงการใช้โมดูลการรักษาความปลอดภัยฮาร์ดแวร์ (HSM) ระหว่างการทดสอบเวเฟอร์และบรรจุภัณฑ์ ซึ่งการใช้ใบรับรอง x.509 FPGA ขนาด 768 ไบต์ที่ลงนามแบบดิจิทัลซึ่งฝังอยู่ใน FPGA SoC ทุกเครื่องช่วยเพิ่มการรับประกันซัพพลายเชน

เครื่องตรวจจับการงัดแงะบนชิปจำนวนมากรวมอยู่ใน FPGA SoC เหล่านี้เพื่อให้มั่นใจในการทำงานที่ปลอดภัยและเชื่อถือได้ หากตรวจพบการงัดแงะ จะมีการส่งสัญญาณเตือนเพื่อให้ระบบสามารถตอบสนองได้ตามต้องการ เครื่องตรวจจับการงัดแงะที่มีอยู่เช่น:

- จอภาพแรงดันไฟฟ้า

- เซ็นเซอร์อุณหภูมิ

- เครื่องตรวจจับความผิดพลาดของนาฬิกาและความถี่สัญญาณนาฬิกา

- ตัวตรวจจับที่ใช้งาน JTAG

- เครื่องตรวจจับที่ใช้งานตาข่าย

เราสามารถมั่นใจได้ถึงความปลอดภัยเพิ่มเติมด้วยมาตรการตอบโต้การโจมตีด้วยกำลังค่าสหสัมพันธ์ (CPA) บล็อกการเข้ารหัสแบบสมมาตรมาตรฐานการเข้ารหัสขั้นสูง 256 บิต (AES-256) ความสามารถในการแยกย่อยการเข้ารหัสแบบบูรณาการเพื่อให้มั่นใจถึงความสมบูรณ์ของข้อมูล, PUF ในตัวสำหรับการจัดเก็บคีย์ และความสามารถในการทำให้เป็นศูนย์สำหรับ FPGA Fabric และหน่วยความจำบนชิปทั้งหมด

ตัวอย่าง FPGA SoC

Microchip Technology รวมเอาความสามารถและเทคโนโลยีเหล่านี้ไว้ใน PolarFire FPGA SoC ที่มีความเร็วและพิกัดอุณหภูมิหลายระดับ รวมทั้งมีขนาดแพ็คเกจขนาดต่าง ๆ เพื่อรองรับความต้องการของนักออกแบบสำหรับโซลูชันที่หลากหลาย โดยมีองค์ประกอบลอจิกตั้งแต่ 25 K ถึง 460 K อุณหภูมินั้นมีอยู่สี่ระดับ (ทั้งหมดคือค่า TJ ) ซึ่งประกอบไปด้วยช่วงใช้งานเชิงพาณิชย์ 0°C ถึง +100°C, ช่วงใช้งานอุตสาหกรรม -40°C ถึง +100°C, ช่วงใช้งานด้านยานยนต์ -40°C ถึง +125°C และช่วงใช้งานทางการทหาร -55°C ถึง +125°C

นักออกแบบสามารถเลือกจากอุปกรณ์เกรดความเร็วมาตรฐาน หรืออุปกรณ์เกรดความเร็ว -1 ที่เร็วขึ้น 15% โดย FPGA SoC เหล่านี้สามารถทำงานได้ที่ 1.0 โวลต์สำหรับการใช้พลังงานต่ำสุด หรือที่ 1.05 โวลต์เพื่อประสิทธิภาพที่ดีขึ้น ซึ่งมีตัวเลือกหลายขนาด ได้แก่ 11 x 11 มม. (มม.), 16 x 16 มม. และ 19 x 19 มม.

สำหรับการใช้งานที่ต้องการเพิ่มอุณหภูมิใช้งานเชิงพาณิชย์ การทำงานความเร็วมาตรฐาน และองค์ประกอบลอจิก 254 K ในแพ็คเกจขนาด 19 x 19 มม. นักออกแบบสามารถใช้ MPFS250T-FCVG484EES แต่สำหรับโซลูชันที่ง่ายกว่าที่ต้องการองค์ประกอบลอจิก 23 K นักออกแบบสามารถหันไปใช้ MPFS025T-FCVG484E นอกจากนี้ยังมีการทำงานที่อุณหภูมิเชิงพาณิชย์และเกรดความเร็วมาตรฐานที่กว้างขึ้นในแพ็คเกจขนาด 19 x 19 มม. MPFS250T-1FCSG536T2 ที่มีองค์ประกอบลอจิก 254 K ได้รับการออกแบบมาสำหรับระบบยานยนต์ที่มีประสิทธิภาพสูง และมีช่วงอุณหภูมิในการทำงานที่ -40 ถึง 125°C และระดับความเร็ว -1 สำหรับสัญญาณนาฬิกาที่เร็วขึ้น 15% ในแพ็คเกจขนาดกะทัดรัด 16 x 16 มม. พร้อมบอล 536 ลูก ห่างกัน 0.5 มม. (รูปที่ 4)

รูปที่ 4: MPFS250T-1FCSG536T2 มีทำงานสำหรับยานยนต์มาในแพ็คเกจขนาด 16 x 16 มม. มีบอล 536 ลูกและระยะพิทช์ 0.5 มม. (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 4: MPFS250T-1FCSG536T2 มีทำงานสำหรับยานยนต์มาในแพ็คเกจขนาด 16 x 16 มม. มีบอล 536 ลูกและระยะพิทช์ 0.5 มม. (แหล่งที่มาภาพ: Microchip Technology)

แพลตฟอร์มพัฒนา FPGA SoC

เพื่อให้ใช้ PolarFire FPGA SoC การออกแบบระบบเร็วขึ้น Microchip จึงขอนำเสนอ MPFS-ICICLE-KIT-ES ซึ่งเป็นชุดอุปกรณ์ PolarFire SoC Icicle ที่ช่วยให้สามารถสำรวจระบบย่อยของไมโครโปรเซสเซอร์ RISC-V ที่รองรับ Linux แบบห้าคอร์ พร้อมการดำเนินการแบบเรียลไทม์ที่ใช้พลังงานต่ำ ชุดอุปกรณ์ประกอบด้วยใบอนุญาต Libero Silver ฟรีที่จำเป็นสำหรับการประเมินการออกแบบ รองรับคุณสมบัติการเขียนโปรแกรมและการดีบักในภาษาเดียว

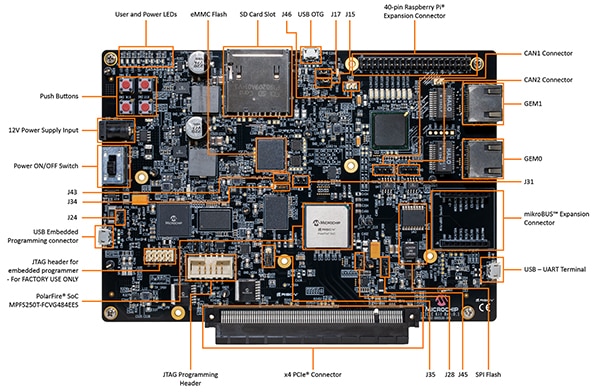

FPGA SoC เหล่านี้ได้รับการสนับสนุนด้วยชุดพัฒนาซอฟต์แวร์เร่งความเร็ว (SDK) VectorBlox สำหรับงาน AI/ML ที่มีฟอร์มแฟกเตอร์ขนาดเล็กและใช้พลังงานต่ำ ความสำคัญคือการทำให้กระบวนการออกแบบง่ายขึ้นจนถึงจุดที่นักออกแบบไม่จำเป็นต้องมีประสบการณ์การออกแบบ FPGA มาก่อน VectorBlox Accelerator SDK ช่วยให้นักพัฒนาสามารถเขียนโปรแกรมโครงข่ายประสาทเทียมที่ประหยัดพลังงานโดยใช้ C/C++ โดยที่ชุด Icicle มีคุณสมบัติมากมายเพื่อให้สภาพแวดล้อมการพัฒนาที่ครอบคลุม รวมถึงระบบเซ็นเซอร์พลังงานแบบหลายรางเพื่อตรวจสอบโดเมนพลังงานต่าง ๆ พอร์ตรูท PCIe และหน่วยความจำออนบอร์ด รวมถึง LPDDR4, QSPI และ eMMC Flash เพื่อเรียกใช้ Linux และ Raspberry Pi และพอร์ตส่วนขยาย mikroBUS สำหรับโฮสต์ของตัวเลือกการเชื่อมต่อแบบใช้สายและไร้สาย รวมถึงส่วนขยายการทำงาน เช่น ความสามารถในการระบุตำแหน่ง GNSS (รูปที่ 5)

รูปที่ 5: สภาพแวดล้อมการพัฒนา FPGA SoC ที่ครอบคลุมนี้รวมถึงตัวเชื่อมต่อสำหรับ Raspberry Pi (บนขวา) และบอร์ดเสริม mikroBUS (ล่างขวา) (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 5: สภาพแวดล้อมการพัฒนา FPGA SoC ที่ครอบคลุมนี้รวมถึงตัวเชื่อมต่อสำหรับ Raspberry Pi (บนขวา) และบอร์ดเสริม mikroBUS (ล่างขวา) (แหล่งที่มาภาพ: Microchip Technology)

บอร์ดเสริม

ตัวอย่างของบอร์ดเสริม mikroBUS ได้แก่:

MIKROE-986 สำหรับการเชื่อมต่อ CAN บัสโดยใช้อินเทอร์เฟซอุปกรณ์ต่อพ่วงแบบอนุกรม (SPI)

MIKROE-1582 สำหรับการเชื่อมต่อระหว่าง MCU กับบัส RS-232

MIKROE-989 สำหรับเชื่อมต่อกับบัสสื่อสาร RS422/485

MIKROE-3144 รองรับเทคโนโลยี LTE Cat M1 และ NB1 ช่วยให้สามารถเชื่อมต่อกับอุปกรณ์ 3GPP IoT ที่เชื่อถือได้และง่ายดาย

MIKROE-2670 เปิดใช้งานฟังก์ชัน GNSS ด้วยการรับสัญญาณ GPS และกลุ่มดาวเทียมกาลิเลโอพร้อมกัน รวมทั้ง BeiDou หรือ GLONASS ส่งผลให้ได้ค่าตำแหน่งที่แม่นยำสูงในกรณีที่มีสัญญาณอ่อนหรือการรบกวนในเมืองที่มีตึกหนาแน่น

สรุป

นักออกแบบสามารถหันไปใช้ FPGA SoC เมื่อพัฒนาระบบที่ให้ความสำคัญต่อความปลอดภัย กำหนดได้แบบเรียลไทม์ และมีการเชื่อมต่อ FPGA SoC มีองค์ประกอบของระบบที่หลากหลาย รวมถึง FPGA Fabric, ระบบย่อย RISC-V MCU พร้อมหน่วยความจำประสิทธิภาพสูง อินเทอร์เฟซการสื่อสารความเร็วสูง และฟังก์ชันความปลอดภัยมากมาย เพื่อช่วยให้นักออกแบบเริ่มต้นใช้งาน มีบอร์ดพัฒนาและสภาพแวดล้อมที่มีองค์ประกอบที่จำเป็นทั้งหมด รวมถึงบอร์ดเสริมที่สามารถใช้เพื่อปรับใช้ฟังก์ชันการสื่อสารและตำแหน่งที่หลากหลาย

บทความที่แนะนำ

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.