สร้างนาฬิกาความถี่สูงที่มีความแปรปรวนต่ำอย่างรวดเร็วโดยใช้โมดูลลูปการแปล

Contributed By DigiKey's North American Editors

2021-08-04

นักออกแบบเครื่องมือวัดและระบบการวัดต้องการสัญญาณที่ปราศจากการแปรปรวนเพื่อให้อัตราส่วนสัญญาณต่อสัญญาณรบกวน (SNR) หรือขนาดเวกเตอร์ข้อผิดพลาด (EVM) ที่จำเป็นต่อการตอบสนองความต้องการของลูกค้าที่มีความต้องการมากขึ้น ในขณะเดียวกัน พวกเขายังต้องเผชิญกับแรงกดดันอย่างมากในการลดรอยเท้าของบอร์ด รวมถึงต้นทุนการออกแบบ และความซับซ้อน อย่างหลังมีความสำคัญอย่างยิ่งในการย่นระยะเวลาในการพัฒนาเพื่อให้สอดคล้องกับกรอบเวลาสู่ตลาดที่แคบลง

เพื่อจัดการกับความท้าทายในการใช้งานต่าง ๆ วิศวกรจำเป็นต้องเปลี่ยนโซลูชันเครื่องมือวัดและนาฬิกาวัดจากการออกแบบที่ไม่ต่อเนื่องแบบสั่งทำพิเศษเป็นโซลูชันแบบบูรณาการมากขึ้น ขั้นตอนสำคัญในการดำเนินการนี้คือการใช้ลูปล็อกเฟสการแปลแบบบูรณาการ (PLL) ซึ่งช่วยให้สามารถแปลงความถี่ขึ้นของสัญญาณออสซิลเลเตอร์ที่ควบคุมด้วยแรงดันไฟฟ้า (VCO) แบบเดิม ในขณะที่ยังคงความกระวนกระวายใจและสัญญาณรบกวนของเฟสของออสซิลเลเตอร์เฉพาะที่ภายนอกแบบตายตัว (LO)

บทความนี้กล่าวถึงบทบาทของลูปการแปลที่นำไปสู่การบรรลุจุดรบกวนของเฟสแบบบูรณาการที่ต่ำที่สุดในอุตสาหกรรม โดยตัวอย่างนี้จะขอแนะนำADF4401A Translation Loop system-in-package (TL SiP) จากAnalog Devices และแสดงให้เห็นว่ามันตอบสนองความต้องการด้านประสิทธิภาพได้อย่างไรผ่านสัญญาณเอาท์พุตที่มีความสามารถในการกระวนกระวายใจแบบรวม sub-10 femtosecond (fs) rms และการแยกที่ได้รับการปรับปรุงเพื่อลดทอนส่วนประกอบปลอมในขณะเดียวกันก็ตอบสนองการผสานรวมของนักออกแบบ ต้นทุน ความซับซ้อน และความต้องการด้านเวลาสู่ตลาด

PLL แบบดั้งเดิมกับการดำเนินการวนรอบการแปล

วัตถุประสงค์หลักของลูปการแปลคือการสร้างสัญญาณเอาต์พุตที่ล็อกไว้กับสัญญาณอ้างอิงอินพุตโดยมีสัญญาณรบกวนเฟสในแบนด์ที่ลดลงอย่างมากเมื่อเทียบกับ PLL แบบเดิม

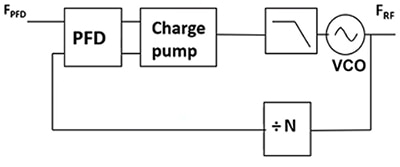

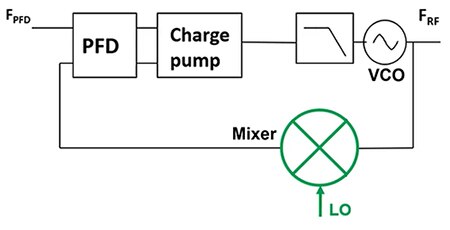

PLL มาตรฐานประกอบด้วยระบบป้อนกลับที่มีตัวตรวจจับความถี่เฟส (PFD) ปั๊มประจุ ตัวกรองความถี่ต่ำผ่าน (LPF) VCO และตัวแบ่งความถี่ป้อนกลับ N (รูปที่ 1)

รูปที่ 1: PLL มาตรฐานล็อคไปที่ความถี่ที่ต่ำกว่า (FPFD) อ้างอิงและสร้างความถี่เอาต์พุต (FRF) (ที่มาของภาพ: บอนนี่ เบเกอร์)

รูปที่ 1: PLL มาตรฐานล็อคไปที่ความถี่ที่ต่ำกว่า (FPFD) อ้างอิงและสร้างความถี่เอาต์พุต (FRF) (ที่มาของภาพ: บอนนี่ เบเกอร์)

PFD จะเปรียบเทียบเฟสของการอ้างอิงอินพุตและเฟสของสัญญาณป้อนกลับ และสร้างชุดพัลส์ตามสัดส่วนกับข้อผิดพลาดของเฟสระหว่างกัน ปั๊มชาร์จจะรับพัลส์ PFD และแปลงเป็นพัลส์แหล่งกระแสหรือพัลส์ซิงก์ที่จะปรับความถี่ VCO ขึ้นหรือลงในความถี่ LPF จะขจัดพลังงานความถี่สูงทั้งหมดของพัลส์และแปลงเป็นแรงดันไฟฟ้าที่ VCO สามารถใช้ได้ สัญญาณเอาท์พุตของ VCO จะถูกป้อนกลับไปยังบล็อก PFD ผ่านตัวแบ่ง N เพื่อให้ลูปสมบูรณ์

ฟังก์ชันการถ่ายโอนความถี่ของรูปที่ 1 คำนวณโดยใช้สมการที่ 1:

![]() สมการที่ 1

สมการที่ 1

เมื่อ FRF คือ ความถี่เอาท์พุต

N คืออัตราส่วนตัวหารป้อนกลับ (อาจเป็นจำนวนเต็มหรือเศษส่วนได้)

FPFD คือความถี่ PFD

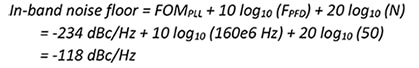

สัญญาณรบกวนพื้นฐานในแถบคลื่นความถี่ของรูปที่ 1 คำนวณโดยใช้สมการที่ 2:

![]() สมการ 2

สมการ 2

ที่ FOMPLL เป็น figure of merit (FOM) ของสัญญาณรบกวนพื้นฐานในแถบคลื่นความถี่ของ PLL

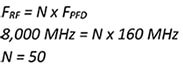

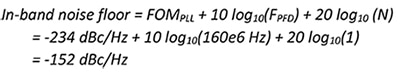

ลองพิจารณาตัวอย่างที่มี FOM ของเฟสสัญญาณรบกวนในวงที่ -234 เดซิเบลต่อเฮิรตซ์ (dB/Hz) ความถี่ PFD (FPFD) 160 เมกะเฮิรตซ์ (MHz) และความถี่เอาต์พุต (FRF) ที่ 8 กิกะเฮิรตซ์ (GHz)

สำหรับระบบนี้ สมการที่ 1 ใช้ในการคำนวณค่าของ N:

สมการที่ 2 ใช้ในการคำนวณพื้นเสียงในแถบความถี่:

ในการคำนวณข้างต้น ตัวแบ่ง N มีส่วนอย่างมากต่อพื้นเสียงรบกวนภายในวงดนตรีโดยรวม โดยมีค่า 20 log10 (50) เท่ากับ 34 เดซิเบล ค่า N ที่น้อยกว่าจะลดระดับเสียงในแถบความถี่ อย่างไรก็ตาม มันจะลดความถี่เอาต์พุตด้วย แล้วเราจะสร้างความถี่เอาต์พุตที่สูงและรักษาค่าเกนที่ต่ำกว่า (N) ได้อย่างไร?

รูปที่ 2: สำหรับ PLL มาตรฐานในตัวอย่างนี้ สัญญาณรบกวนจากตัวแบ่งป้อนกลับ (20 log10(N)) มีสัญญาณรบกวนในแถบความถี่สูงกว่า 34 dB เมื่อเทียบกับจุดสีเหลืองด้านล่างโดยที่ N = 1 (ที่มาของภาพ: บอนนี่ เบเกอร์)

รูปที่ 2: สำหรับ PLL มาตรฐานในตัวอย่างนี้ สัญญาณรบกวนจากตัวแบ่งป้อนกลับ (20 log10(N)) มีสัญญาณรบกวนในแถบความถี่สูงกว่า 34 dB เมื่อเทียบกับจุดสีเหลืองด้านล่างโดยที่ N = 1 (ที่มาของภาพ: บอนนี่ เบเกอร์)

วิธีแก้ปัญหานี้คือการเปลี่ยน N-divider ด้วยขั้นตอนการผสมแบบ down-converting (รูปที่ 3)

รูปที่ 3: ลูปการแปลใช้เครื่องผสมเพื่อแปลงความถี่ VCO ลงเป็นความถี่ PFD แทนการใช้ตัวแบ่งป้อนกลับแบบเดิม (ที่มาของภาพ: บอนนี่ เบเกอร์)

รูปที่ 3: ลูปการแปลใช้เครื่องผสมเพื่อแปลงความถี่ VCO ลงเป็นความถี่ PFD แทนการใช้ตัวแบ่งป้อนกลับแบบเดิม (ที่มาของภาพ: บอนนี่ เบเกอร์)

ในรูปที่ 3 เครื่องผสมจะแทนที่ตัวแบ่งผลป้อนกลับ N ส่งผลให้มีการเพิ่มของลูปเท่ากับ 1 (N=1) การดำเนินการนี้จะช่วยลดการมีส่วนร่วมของลูปป้อนกลับกับพื้นเสียงในแถบความถี่ได้อย่างมาก สำหรับการคำนวณสัญญาณรบกวนในแถบความถี่ ตอนนี้ค่าของ N จะเท่ากับ 1 เมื่อใช้สมการที่ 2 ระดับสัญญาณรบกวนในแถบความถี่สำหรับระบบที่ดัดแปลงจะเป็นดังนี้:

สัญญาณรบกวนในแถบความถี่ใหม่แสดงการปรับปรุง 34 dBc/Hz

ในรูปที่ 3 เครื่องผสมขึ้นอยู่กับ LO ที่มีสัญญาณรบกวนต่ำมาก เรียกว่า Offset LO NSLO ± FRF ต้องเท่ากับ FPFD เพื่อให้บรรลุล็อค

ด้วยสถาปัตยกรรมลูปการแปล สัญญาณรบกวนของเฟสของ Offset LO มีความสำคัญมากในการบรรลุประสิทธิภาพที่ดีที่สุดที่เอาต์พุต RF ด้วยเหตุผลนี้ วิศวกรมักจะออกแบบ Offset LO โดยยึดตามคลื่นเสียงที่ควบคุมด้วยแรงดันไฟฟ้า (SAW) หรือออสซิลเลเตอร์ (VCSO) หรือเครื่องกำเนิดหวี หรือไดอิเล็กตริกเรโซเนเตอร์ออสซิลเลเตอร์ (DRO) หมายเหตุ: สำหรับการสนับสนุนในการออกแบบ Offset LO โปรดติดต่อ Analog Devices

ความท้าทายในการแปลง

ในวิธีการแบบเก่า การออกแบบลูปการแปลสัญญาณรบกวนต่ำนั้นเกี่ยวข้องกับการนำวงจรบล็อกจำนวนมากมาใช้ ส่งผลให้มีการออกแบบที่ซับซ้อน ซึ่งมักจะมีขนาดใหญ่ และมีความยืดหยุ่นจำกัด นอกจากนี้ วงจรทั้งหมดจะต้องได้รับการตรวจสอบและกำหนดลักษณะเฉพาะสำหรับการทำงานของเป้าหมาย ตัวอย่างเช่น ความกังวลในการออกแบบที่สำคัญอย่างหนึ่งคือการรั่วไหลของ LO (การแยก LO ถึง RF) ไปยังสัญญาณเอาท์พุต RF นี่เป็นความท้าทายที่สำคัญสำหรับวิศวกรที่จะต้องแก้ไข ด้วยการออกแบบแบบดั้งเดิม วิศวกรมักจะดำเนินการออกแบบซ้ำหลายครั้งเพื่อให้ได้ประสิทธิภาพที่ดีที่สุดและการแยกตัวที่เหมาะสม

รูปที่ 3 แสดงให้เห็นว่า ADF4401A รวมบล็อกวงจรหลักอย่างไรเพื่อให้มีโซลูชันที่มีลักษณะเฉพาะอย่างสมบูรณ์ และขจัดพื้นที่ที่ยากในแบบดั้งเดิมซึ่งเกี่ยวข้องกับประสิทธิภาพและการแยกตัวออกจากการออกแบบลูปการแปล โซลูชันที่ตั้งโปรแกรมได้นี้ช่วยให้วิศวกรสามารถบรรลุประสิทธิภาพสูงสุดในความพยายามครั้งแรกและลดเวลาในการออกสู่ตลาด

การประเมิน ADF4401A

ADF4401A ได้รับการออกแบบมาเพื่อช่วยให้วิศวกรลดเวลาในการนำเครื่องมือที่มีประสิทธิภาพสูงออกสู่ตลาด โดยใช้โซลูชันการสร้างความถี่ที่มีแบนด์วิดท์ RF 62.5 MHz ถึง 8 GHz ด้วยการใช้มิกเซอร์แบบแปลงลง ADF4401A มีสัญญาณรบกวนในแบนด์ที่ต่ำมาก โดยมีไวด์แบนด์ที่กระวนกระวายใจอยู่ที่ ~9 femtoseconds (fs) ที่รวมจาก 100 Hz ถึง 100 MHz เทคนิคการออกแบบและเลย์เอาต์ภายใน ADF4401A ช่วยให้มีช่วงไดนามิกที่ปราศจากการปลอมแปลงทั่วไปที่ 90 dBc ขนาดบรรจุภัณฑ์ 18 x 18 x 2.018 มม. (มม.) ช่วยลดพื้นที่บอร์ดลงอย่างมากเมื่อเทียบกับการออกแบบแบบแยกส่วนแบบดั้งเดิม

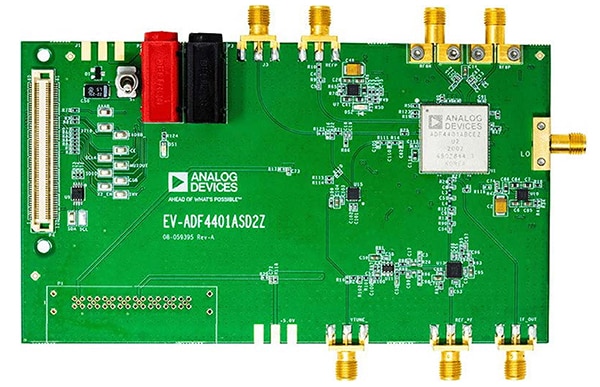

ในการประเมินประสิทธิภาพของอุปกรณ์ นักออกแบบสามารถใช้ EV-ADF4401ASD2Z บอร์ดประเมินผล (ภาพที่ 4) บอร์ดนี้มีลูปการแปลที่สมบูรณ์ รวมถึง PFD ภายนอก (HMC3716) ตัวกรองที่ใช้งาน (LT6200) และมัลติเพล็กเซอร์ (ADG1609)

รูปที่ 4: บอร์ดประเมินผล EV-ADF4401ASD2Z สำหรับโมดูลลูปการแปล ADF4401A ประกอบด้วย PFD ภายนอก อินเทอร์เฟซ USB และตัวควบคุมแรงดันไฟฟ้า (แหล่งรูปภาพ: Analog Devices)

รูปที่ 4: บอร์ดประเมินผล EV-ADF4401ASD2Z สำหรับโมดูลลูปการแปล ADF4401A ประกอบด้วย PFD ภายนอก อินเทอร์เฟซ USB และตัวควบคุมแรงดันไฟฟ้า (แหล่งรูปภาพ: Analog Devices)

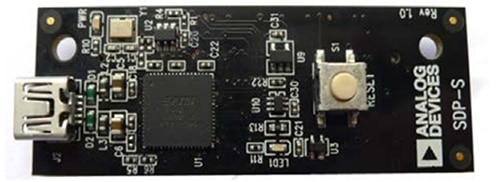

EV-ADF4401ASD2Z ประกอบด้วย ADF4401A TL SiP พร้อม VCO ในตัว, ตัวกรองลูป (5 MHz), PFD, อินเทอร์เฟซ USB และตัวควบคุมแรงดันไฟฟ้า นอกจากนี้ EV-ADF4401ASD2Z ยังต้องการ EVAL-SDP-CS1Z (SDP-S) บอร์ดควบคุมแพลตฟอร์มสาธิตระบบ (SDP) (ซีเรียล) (รูปที่ 5) บอร์ดนี้ให้การเชื่อมต่อ USB จากพีซีไปยัง EV-ADF4401ASD2Z เพื่อให้สามารถตั้งโปรแกรมได้ บอร์ดควบคุมไม่มีให้ในชุด EV-ADF4401ASD2Z

รูปที่ 5: บอร์ดควบคุม EVAL-SDP-CS1Z (หรือ SDP-S) จำเป็นสำหรับการเชื่อมต่อ USB จาก EV-ADF4401ASD2Z ไปยังพีซีสำหรับการเขียนโปรแกรม (แหล่งรูปภาพ: Analog Devices)

รูปที่ 5: บอร์ดควบคุม EVAL-SDP-CS1Z (หรือ SDP-S) จำเป็นสำหรับการเชื่อมต่อ USB จาก EV-ADF4401ASD2Z ไปยังพีซีสำหรับการเขียนโปรแกรม (แหล่งรูปภาพ: Analog Devices)

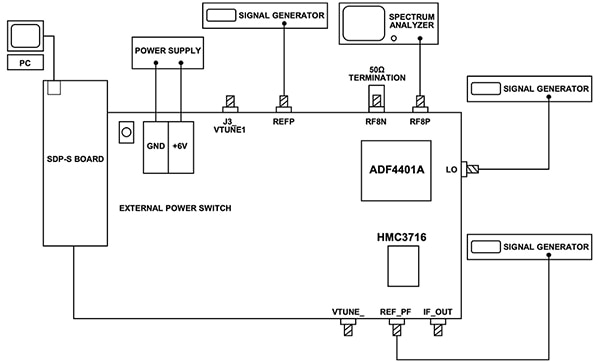

รูปที่ 6 แสดงการเชื่อมต่อทางกายภาพของระบบ EV-ADF4401ASD2Z ซอฟต์แวร์สำหรับวิเคราะห์ | ควบคุม | ประเมินผล (ACE) ที่เกี่ยวข้องกับการควบคุมฟังก์ชัน TL SiP พลังงานมาจากแหล่งจ่ายไฟ 6 โวลต์ภายนอก

รูปที่ 6: แผนภาพการตั้งค่า EV-ADF4401ASD2Z แสดงอุปกรณ์และการเชื่อมต่อที่จำเป็นในการประเมิน ADF4401A รวมถึงแผงควบคุม SDP-S, PC, แหล่งจ่ายไฟ, เครื่องกำเนิดสัญญาณ และเครื่องวิเคราะห์สเปกตรัม (แหล่งรูปภาพ: Analog Devices)

รูปที่ 6: แผนภาพการตั้งค่า EV-ADF4401ASD2Z แสดงอุปกรณ์และการเชื่อมต่อที่จำเป็นในการประเมิน ADF4401A รวมถึงแผงควบคุม SDP-S, PC, แหล่งจ่ายไฟ, เครื่องกำเนิดสัญญาณ และเครื่องวิเคราะห์สเปกตรัม (แหล่งรูปภาพ: Analog Devices)

อุปกรณ์ที่แนะนำให้ใช้กับบอร์ดประเมินผลนี้ ได้แก่ พีซีที่ใช้ Windows เครื่องวิเคราะห์สเปกตรัมหรือเครื่องวิเคราะห์แหล่งสัญญาณ และเครื่องกำเนิดสัญญาณสามเครื่อง

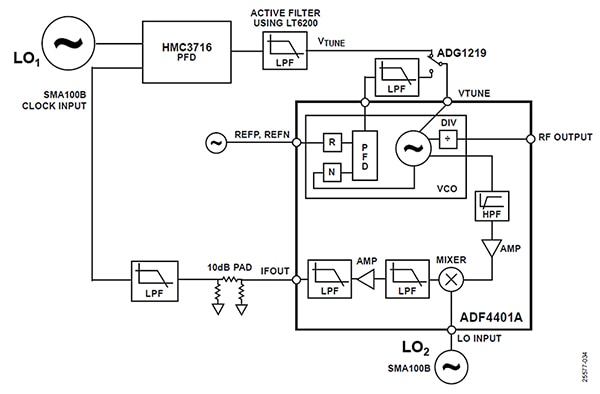

แผนภาพบล็อกของ EV-ADF4401ASD2Z แสดงโมดูล ADF4401A พร้อมกับผลิตภัณฑ์จาก Analog Device HMC3716 PFDLT6200 op-amp และ ADG1219 สวิตช์ SPDT (รูปที่ 7)

รูปที่ 7: แผนภาพบล็อกของบอร์ดประเมินผล EV-ADF4401ASD2Z แสดงส่วนประกอบหลักที่สนับสนุนลูปการแปล AD4401A (แหล่งรูปภาพ: Analog Devices)

รูปที่ 7: แผนภาพบล็อกของบอร์ดประเมินผล EV-ADF4401ASD2Z แสดงส่วนประกอบหลักที่สนับสนุนลูปการแปล AD4401A (แหล่งรูปภาพ: Analog Devices)

การใช้ PFD ที่สามารถทำงานได้ที่ความถี่สูงเป็นสิ่งสำคัญ เนื่องจากช่วยลดความจำเป็นในการแบ่งตัว ซึ่งสามารถลดการตอบสนองของสัญญาณรบกวนในแถบความถี่ได้ ความสามารถในการเปรียบเทียบความถี่เฟส 1.3 GHz ของ HMC3716 ของ Analog Devices ทำให้เหมาะสำหรับใช้ในช่วง IF ของ ADF4401A ความสามารถของวงจรดังกล่าวในการเปรียบเทียบทั้งความถี่และเฟสทำให้ไม่จำเป็นต้องใช้วงจรเพิ่มเติมเพื่อควบคุมความถี่ไปยังความถี่เอาต์พุตที่ต้องการ HMC3716 จะกลายเป็น PFD ภายนอกเพื่อให้ลูปออฟเซ็ตสมบูรณ์ ช่วงการทำงานความถี่สูงและพื้นสัญญาณรบกวนที่มีเฟสต่ำมากของ HMC3716 ทำให้สามารถออกแบบตัวกรองลูปแบนด์วิดท์กว้างได้

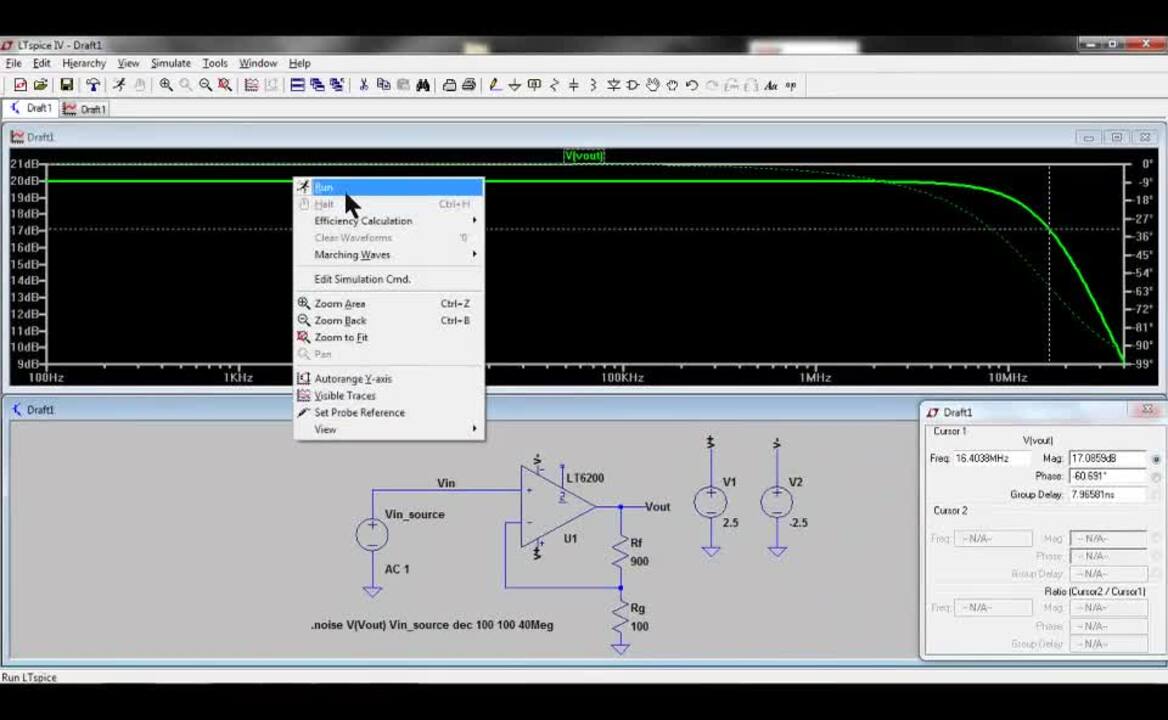

ในรูปที่ 7 ออปแอมป์ LT6200 ที่มีการกำหนดค่า LPF จะลดทอนสัญญาณกระตุ้นความถี่สูง ในขณะที่สวิตช์ ADG1219 จะทำให้ลูปการแปลของระบบเสร็จสมบูรณ์

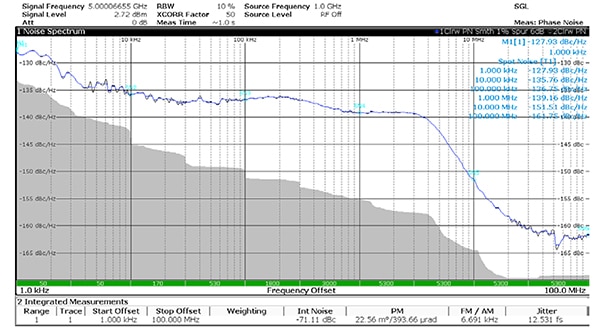

ฟิกซ์เจอร์สำหรับการประเมิน EV-ADF4401ASD2Z สร้างแผนภาพสัญญาณรบกวนในแถบความถี่และการวัดความแปรปรวนดังแสดงในรูปที่ 8

รูปที่ 8: สัญญาณรบกวนเฟสไซด์แบนด์เดี่ยวที่เอาต์พุต 5 GHz โดยมีการอ้างอิง HMC3716 ภายนอกที่ 500 MHz และ LO ภายนอกที่ 4.5 GHz (แหล่งรูปภาพ: Analog Devices)

รูปที่ 8: สัญญาณรบกวนเฟสไซด์แบนด์เดี่ยวที่เอาต์พุต 5 GHz โดยมีการอ้างอิง HMC3716 ภายนอกที่ 500 MHz และ LO ภายนอกที่ 4.5 GHz (แหล่งรูปภาพ: Analog Devices)

ในรูปที่ 8 LO2 และอินพุต HMC3716 เป็น SMA100B RF และเครื่องกำเนิดสัญญาณไมโครเวฟ บอร์ดประเมินผลของ LO2 สัญญาณรบกวนในแถบความถี่อยู่ที่ประมาณ -135 dBc/Hz ซึ่งเห็นได้ชัดที่ออฟเซ็ตต่ำถึง 300 kHz โมดูล ADF4401A, HMC3716 PFD และตัวกรองลูปของ LO2ทำให้เกิดสัญญาณรบกวนในแถบความถี่ประมาณ -140 dBc/Hz สัญญาณรบกวนของเฟสภายในจะปรากฏขึ้นระหว่าง 5 MHz ถึง 50 MHz และพื้นสัญญาณรบกวนของเฟสของฟิกซ์เจอร์จะอยู่ที่ประมาณ -160 dBc/Hz สิ่งเหล่านี้ร่วมกันทำให้ rms กระวนกระวายใจ 12.53 fs ทั้งหมด

สรุป

ระบบเครื่องมือวัดความเร็วสูงต้องการนาฬิกาที่กระวนกระวายใจต่ำมาก เพื่อให้แน่ใจว่าข้อมูลเอาต์พุตยังคงไม่ถูกประนีประนอม ความท้าทายสำหรับวิศวกรคือการหาอุปกรณ์ที่เหมาะสมซึ่งสามารถสร้างระบบนาฬิกากิกะเฮิรตซ์ความเร็วสูงได้ ลูปการแปล ADF4401A ช่วยลดความยุ่งยากในการเลือกอุปกรณ์เพื่อสร้างระบบนาฬิกา ให้โมดูลขนาดกะทัดรัดที่รับประกันการแปรปรวนต่ำที่ความถี่สูง ในขณะที่ยังช่วยลดพื้นที่บอร์ด ค่าใช้จ่าย และเวลาออกสู่ตลาด

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.