สถาปัตยกรรมตัวประมวลผลร่วม: สถาปัตยกรรมระบบฝังตัวสำหรับการสร้างต้นแบบอย่างรวดเร็ว

2021-07-06

หมายเหตุบรรณาธิการ — แม้ว่าประสิทธิภาพและปริมาณการประมวลผลดิจิทัลจะเป็นที่ทราบกันดี แต่สถาปัตยกรรมตัวประมวลผลร่วมมอบโอกาสให้ผู้ออกแบบระบบฝังตัวได้นำกลยุทธ์การจัดการโครงการไปใช้งาน ซึ่งช่วยพัฒนาในด้านของต้นทุนการพัฒนาและเวลาออกสู่ตลาด บทความนี้เน้นในเรื่องการผสมผสานระหว่างไมโครคอนโทรลเลอร์แบบแยกส่วน (MCU) และอุปกรณ์ลอจิกแบบโปรแกรมได้แบบแยกส่วน (Field Programmable Gate Array, FPGA) โดยแสดงให้เห็นว่าสถาปัตยกรรมนี้ช่วยให้กระบวนการออกแบบสามารถวนซ้ำและมีประสิทธิภาพได้อย่างไร นอกจากยังมีการสำรวจการใช้ประโยชน์จากแหล่งข้อมูลงานวิจัย ผลการวิจัยเชิงประจักษ์ และกรณีศึกษา ประโยชน์ของสถาปัตยกรรมนี้ และนำเสนอตัวอย่างการใช้งาน จากบทสรุปของบทความนี้ ผู้ออกแบบระบบฝังตัวจะมีความเข้าใจที่ดีขึ้นว่าเมื่อใดที่ควรจะใช้สถาปัตยกรรมฮาร์ดแวร์อเนกประสงค์นี้และจะใช้งานอย่างไร

บทนำ

ผู้ออกแบบระบบฝังตัวพบว่าตัวเองต้องจัดการกับข้อจำกัดในการออกแบบ ความคาดหวังด้านประสิทธิภาพ และข้อกังวลด้านระยะเวลาดำเนินงานและงบประมาณ แท้จริงแล้วแม้แต่ความสับสนในศัพท์แสลงและวลีที่เกี่ยวกับการจัดการโครงการสมัยใหม่ก็ยังเน้นย้ำถึงลักษณะที่ไม่มั่นคงของบทบาทนี้: “ล้มเหลวอย่างรวดเร็ว”, “คล่องแคล่ว”, “ใช้งานได้ในอนาคต” และ “ปฏิรูปให้เกิดสิ่งใหม่!” แม้กระทั่งการกระทำที่เสี่ยงและเกี่ยวข้องพยายามตอบสนองความคาดหวังเหล่านี้ก็อาจทำให้เจ็บปวดใจ แต่ถึงกระนั้นพวกเขาก็เป็นที่พูดถึงและยังคงได้รับการสนับสนุนต่อไป สิ่งที่จำเป็นคือแนวทางการออกแบบ ซึ่งช่วยให้สามารถใช้กระบวนการพัฒนาแบบวนซ้ำได้ และมักเริ่มต้นด้วยสถาปัตยกรรมฮาร์ดแวร์เช่นเดียวกับระบบฝังตัวส่วนใหญ่

สถาปัตยกรรมตัวประมวลผลร่วมเป็นสถาปัตยกรรมฮาร์ดแวร์ที่รู้จักกันในการรวมจุดแข็งของทั้งหน่วยไมโครคอนโทรลเลอร์ (MCU) และเทคโนโลยีอุปกรณ์ลอจิกแบบโปรแกรมได้ (Field Programmable Gate Array, FPGA) ซึ่งนำเสนอกระบวนการที่สามารถตอบสนองความต้องการของนักออกแบบระบบฝังตัวได้ โดยช่วยให้มีความยืดหยุ่น ซึ่งจำเป็นต่อการจัดการกับความท้าทายทุกรูปแบบ ผู้ออกแบบสามารถแสดงให้เห็นถึงความคืบหน้า บรรลุเป้าหมายสำคัญ และใช้ประโยชน์จากกระบวนการสร้างต้นแบบที่รวดเร็วได้อย่างเต็มที่ จากการจัดหาฮาร์ดแวร์ที่สามารถปรับซ้ำได้

กระบวนการนี้เป็นส่วนสำคัญของโครงการ โดยแต่ละโครงการมีจุดเด่นของตนเองที่จะเพิ่มเข้าไปในการพัฒนา จะมีการอ้างถึงคำศัพท์ต่อไปนี้ตลอดทั้งบทความ: ขั้นตอนการประมวลผลสัญญาณดิจิตอลด้วยไมโครคอนโทรลเลอร์, ขั้นตอนการจัดการระบบด้วยไมโครคอนโทรลเลอร์ และขั้นตอนการใช้งานผลิตภัณฑ์

บทสรุปของบทความนี้จะแสดงให้เห็นว่าสถาปัตยกรรมฮาร์ดแวร์ที่ยืดหยุ่นได้นั้นเหมาะกับการออกแบบระบบฝังตัวที่ทันสมัยมากกว่าแนวทางการออกแบบตายตัว นอกจากนี้แนวทางนี้ก็สามารถส่งผลเชิงบวกต่อต้นทุนโครงการและเวลาออกสู่ตลาด โดยมีการใช้ข้อโต้แย้ง ตัวอย่าง และกรณีศึกษา เพื่อส่งเสริมแนวทางนี้ จากการสังเกตคุณค่าของขั้นตอนแต่ละขั้นตอนจากความยืดหยุ่นในการออกแบบที่สถาปัตยกรรมนี้มีให้ เป็นที่ชัดเจนว่าสถาปัตยกรรมฮาร์ดแวร์ที่ปรับเปลี่ยนได้นั้นเป็นตัวขับเคลื่อนที่ทรงพลังในการผลักดันการออกแบบระบบฝังตัว

สำรวจจุดแข็งของสถาปัตยกรรมตัวประมวลผลร่วม: การออกแบบที่ยืดหยุ่นและการประมวลผลประสิทธิภาพสูง

การใช้งานทั่วไปสำหรับการออกแบบ FPGA คือการเชื่อมต่อโดยตรงกับตัวแปลงอนาล็อกเป็นดิจิตอลความเร็วสูง (ADC) โดยสัญญาณจะถูกแปลงเป็นดิจิทัลเข้าไปใน FPGA จากนั้นจะใช้บางอัลกอริธึมของตัวประมวลผลสัญญาณดิจิทัล (DSP) กับสัญญาณนี้ สุดท้าย FPGA จะทำการตัดสินใจตามผลลัพธ์

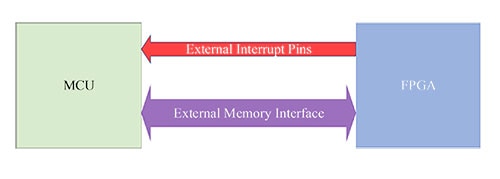

การใช้งานดังกล่าวจะใช้เป็นตัวอย่างในบทความนี้ นอกจากนี้รูปที่ 1 ยังแสดงสถาปัตยกรรมตัวประมวลผลร่วมทั่วไป โดยที่ MCU และ FPGA เชื่อมต่อกันผ่านอินเทอร์เฟซหน่วยความจำภายนอกของ MCU ซึ่งจะถือว่า FPGA เป็นส่วนหนึ่งของหน่วยความจำเข้าถึงโดยสุ่ม (SRAM) ภายนอก สัญญาณจาก FPGA กลับมาที่ MCU และทำหน้าที่เป็นอินเตอร์รัพต์ไลน์และตัวบ่งชี้สถานะของฮาร์ดแวร์ ซึ่งช่วยให้ FPGA สามารถระบุสถานะที่สำคัญของ MCU เช่น การสื่อสารว่าการแปลงอนาล็อกเป็นดิจิตอลพร้อมแล้วหรือเกิดข้อผิดพลาด หรือเกิดเหตุการณ์สำคัญอื่น ๆ

รูปที่ 1: แผนภาพของตัวประมวลผลร่วมทั่วไป (MCU + FPGA) (ที่มาของภาพ:CEPD )

รูปที่ 1: แผนภาพของตัวประมวลผลร่วมทั่วไป (MCU + FPGA) (ที่มาของภาพ:CEPD )

จุดแข็งของแนวทางตัวประมวลผลร่วมน่าจะมองเห็นได้ดีที่สุดจากผลลัพธ์ของแต่ละขั้นตอนที่กล่าวถึงข้างต้น ซึ่งไม่ได้ประเมินคุณค่าจากรายการความสำเร็จของงานหรือขั้นตอนเพียงอย่างเดียวเท่านั้น แต่ยังประเมินความพร้อมใช้งานจากความสำเร็จเหล่านี้ คำตอบของคำถามต่อไปนี้จะช่วยในการประเมินคุณค่าโดยรวมของผลลัพธ์ที่ได้จากขั้นตอนต่าง ๆ:

- ความคืบหน้าของสมาชิกในทีมคนอื่น ๆ สามารถดำเนินต่อไปอย่างรวดเร็วยิ่งขึ้น เนื่องจากมีการจัดการการพึ่งพากันในโครงการและปัญหาคอขวดใช่หรือไม่

- ความสำเร็จของขั้นตอนต่าง ๆ ทำให้เกิดการใช้งานโปรแกรมแบบขนานเพิ่มเติมได้อย่างไร

ขั้นตอนการประมวลผลสัญญาณดิจิตอลด้วยไมโครคอนโทรลเลอร์

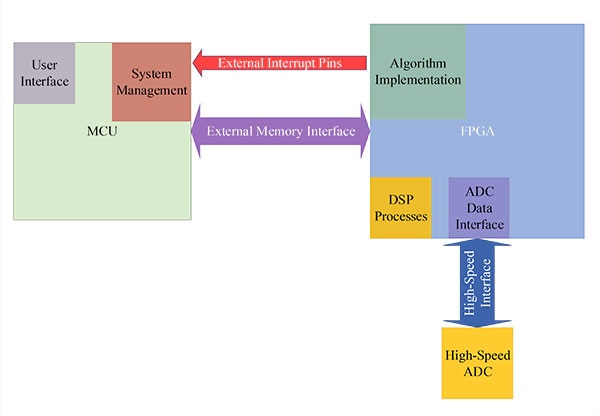

รูปที่ 2: สถาปัตยกรรม - การประมวลผลสัญญาณดิจิทัลด้วยไมโครคอนโทรลเลอร์ (ที่มาของภาพ: CEPD)

รูปที่ 2: สถาปัตยกรรม - การประมวลผลสัญญาณดิจิทัลด้วยไมโครคอนโทรลเลอร์ (ที่มาของภาพ: CEPD)

ขั้นตอนการพัฒนาแรกที่สถาปัตยกรรมฮาร์ดแวร์นี้อนุญาตให้วาง MCU ไว้ด้านหน้าและตรงกลาง เมื่อปัจจัยอื่น ๆ คงที่ MCU และการพัฒนาซอฟต์แวร์ที่ใช้งานได้นั้นจะใช้ทรัพยากรและใช้เวลาน้อยกว่า FPGA และการพัฒนารูปแบบภาษาฮาร์ดแวร์ (HDL) ดังนั้นการเริ่มต้นพัฒนาผลิตภัณฑ์โดยใช้ MCU เป็นโปรเซสเซอร์หลักจะสามารถใช้ ทดสอบ และตรวจสอบอัลกอริทึมได้รวดเร็วยิ่งขึ้น วิธีนี้ช่วยให้พบจุดบกพร่องของลอจิกและอัลกอริทึมได้ในช่วงต้นของกระบวนการออกแบบ และยังช่วยให้สามารถทดสอบและตรวจสอบสายโซ่สัญญาณจำนวนมากได้

บทบาทของ FPGA ในขั้นตอนเริ่มต้นนี้คือทำหน้าที่เป็นอินเทอร์เฟซการรวบรวมข้อมูลความเร็วสูง ซึ่งมีหน้าที่ในการถ่ายโอนข้อมูลจาก ADC ความเร็วสูงอย่างน่าเชื่อถือ แจ้งเตือน MCU ว่ามีข้อมูล และให้ข้อมูลนี้แก่อินเทอร์เฟซหน่วยความจำภายนอกของ MCU แม้ว่าบทบาทนี้จะไม่รวมถึงการนำกระบวนการ DSP ที่ใช้ HDL หรืออัลกอริธึม แต่ก็มีความสำคัญเป็นอย่างยิ่ง

การพัฒนา FPGA ที่ดำเนินการในขั้นตอนนี้เป็นการวางรากฐานสำหรับความสำเร็จสูงสุดของผลิตภัณฑ์ทั้งในการพัฒนาผลิตภัณฑ์และเมื่อออกสู่ตลาด การให้ความสำคัญอินเทอร์เฟซระดับต่ำเพียงอย่างเดียว จะช่วยให้คุณมีเวลาเพียงพอในการทดสอบการดำเนินการที่จำเป็นเหล่านี้ เมื่อ FPGA ทำหน้าที่ในการเชื่อมต่อนี้ได้อย่างน่าเชื่อถือ สามารถสรุปผลของขั้นตอนได้อย่างมั่นใจ

ผลลัพธ์ที่สำคัญจากขั้นตอนเริ่มต้นมีดังต่อไปนี้:

- เส้นทางสัญญาณแบบเต็ม - ทั้งการขยายสัญญาณ การลดทอนสัญญาณ และการแปลงสัญญาณจะได้รับการทดสอบและตรวจสอบ

- เวลาและความพยายามในการพัฒนาโครงการจะลดลงโดยการเริ่มใช้อัลกอริทึมในซอฟต์แวร์ (C/C++) ซึ่งมีค่ามากสำหรับผู้บริหารและหุ้นส่วนคนอื่น ๆ ที่จำเป็นต้องทราบความเป็นไปได้ของโครงการนี้ก่อนที่จะอนุมัติขั้นตอนการออกแบบในอนาคต

- บทเรียนที่ได้จากการใช้อัลกอริทึมใน C/C++ จะสามารถถ่ายโอนไปยังการใช้งาน HDL ได้โดยตรง ผ่านการใช้เครื่องมือซอฟต์แวร์กับ HDL เช่น Xilinx HLS

ขั้นตอนการจัดการระบบด้วยไมโครคอนโทรลเลอร์

รูปที่ 3: สถาปัตยกรรม - การจัดการระบบด้วยไมโครคอนโทรลเลอร์ (ที่มาของภาพ: CEPD)

รูปที่ 3: สถาปัตยกรรม - การจัดการระบบด้วยไมโครคอนโทรลเลอร์ (ที่มาของภาพ: CEPD)

ขั้นตอนการพัฒนาขั้นตอนที่สองเป็นแนวทางตัวประมวลผลร่วมนี้นำเสนอมาจากการย้ายกระบวนการ DSP และการนำอัลกอริทึมจาก MCU ไปยัง FPGA โดยที่ FPGA ยังคงเป็นส่วนที่มีหน้าที่ในอินเทอร์เฟซ ADC ความเร็วสูง อย่างไรก็ตาม หาก FPGA มีบทบาทอื่น ๆ เหล่านี้ ความเร็วและการประมวลผลแบบขนานใน FPGA จะถูกนำมาใช้อย่างเต็มที่ นอกจากนี้ อินสแตนซ์หลายอินสแตนซ์ของกระบวนการ DSP และช่องอัลกอริธึมาสามารถเรียกใช้พร้อมกันได้ต่างจาก MCU

จากบทเรียนที่เรียนรู้จากการปรับใช้ของ MCU นักออกแบบได้นำความมั่นใจนี้ไปสู่ความสำเร็จครั้งถัดไป เครื่องมือต่าง ๆ ที่กล่าวมาข้างต้น Vivado HLS จาก Xilinx แปลการทำงานจากโค้ด C/C++ ที่สามารถเรียกทำงานได้เป็น HDL ที่สังเคราะห์ได้ ขณะนี้ข้อจำกัดด้านเวลา พารามิเตอร์กระบวนการ และการตั้งค่าของผู้ใช้อื่น ๆ ยังต้องมีการกำหนดและนำไปใช้ อย่างไรก็ตาม ฟังก์ชันการทำงานหลักจะยังคงดำเนินต่อไปรวมทั้งการแปลสัญญาณเพื่อใช้ใน FPGA

ในขั้นตอนนี้บทบาทของ MCU คือผู้จัดการระบบ รีจิสเตอร์แสดงสถานะและรีจิสเตอร์ควบคุมภายใน FPGA จะได้รับการตรวจสอบ อัปเดต และรายงานโดย MCU นอกจากนี้ MCU ยังจัดการอินเทอร์เฟซผู้ใช้ (UI) โดยอินเทอร์เฟซผู้ใช้นี้อาจอยู่ในรูปแบบของเว็บเซิร์ฟเวอร์ที่เข้าถึงผ่านการเชื่อมต่ออีเทอร์เน็ตหรือ Wi-Fi หรืออาจเป็นอินเทอร์เฟซหน้าจอสัมผัสอุตสาหกรรมที่ให้การเข้าถึงแก่ผู้ใช้ ณ จุดใช้งาน ประเด็นสำคัญจากบทบาทใหม่ที่ละเอียดยิ่งขึ้นของ MCU คือ ทั้ง MCU และ FPGA ถูกนำมาใช้ในงานที่เหมาะสมจากการปลดปล่อยจากการประมวลผลที่เน้นการคำนวณ

ผลลัพธ์ที่สำคัญจากขั้นตอนสำคัญนี้มีดังต่อไปนี้:

- FPGA ให้การใช้งานโปรแกรมแบบคู่ขนานที่รวดเร็วของกระบวนการ DSP รวมทั้งการใช้อัลกอริทึมMCU ให้ UI ที่ตอบสนองและรวดเร็ว พร้อมทั้งจัดการกระบวนการของผลิตภัณฑ์

- หลังจากการพัฒนาและตรวจสอบใน MCU เป็นครั้งแรก ความเสี่ยงของอัลกอริทึมก็ลดลง ซึ่งจะถูกแปลเป็น HDL ที่สังเคราะห์ได้ โดยเครื่องมือต่าง ๆ เช่น Vivado HLS ทำให้กระบวนการแปลนี้ง่ายขึ้น นอกจากนี้สามารถลดความเสี่ยงเฉพาะ FPGA ได้ด้วยเครื่องมือจำลองแบบบูรณาการ เช่น ชุดการออกแบบ Vivado

- ผู้มีส่วนร่วมจะได้ไม่ต้องเผชิญกับความเสี่ยงที่สำคัญจากการย้ายกระบวนการไปยัง FPGA ในทางกลับกันพวกเขาจะได้เห็นและเพลิดเพลินไปกับประโยชน์ที่ได้รับจากความเร็วและความขนานของ FPGA มีการสังเกตการปรับปรุงประสิทธิภาพที่วัดได้ และสามารถให้ความสำคัญกับการเตรียมการออกแบบนี้สำหรับการผลิต

ขั้นตอนการปรับใช้ผลิตภัณฑ์

ด้วยการประมวลผลที่เน้นการคำนวณภายใน FPGA และ MCU ที่จัดการระบบและบทบาทของอินเทอร์เฟซผู้ใช้ ผลิตภัณฑ์จึงพร้อมสำหรับการใช้งาน ในตอนนี้บทความนี้ไม่สนับสนุนให้ข้ามรุ่นอัลฟ่าและเบต้า อย่างไรก็ตามจุดมุ่งเน้นในขั้นตอนนี้คือความสามารถที่สถาปัตยกรรมตัวประมวลผลร่วมมีให้กับการปรับใช้ผลิตภัณฑ์

ทั้ง MCU และ FPGA เป็นอุปกรณ์ที่สามารถอัปเดตได้ มีความก้าวหน้าหลายอย่างได้ทำให้การอัปเดต FPGA สามารถเข้าถึงได้เหมือนกับการอัปเดตซอฟต์แวร์ นอกจากนี้เนื่องจาก FPGA อยู่ภายในพื้นที่หน่วยความจำที่กำหนดแอดเดรสได้ของ MCU ดังนั้น MCU จึงทำหน้าที่เป็นจุดขาเข้าของระบบ โดยรับทั้งการอัปเดตสำหรับตัวเองและสำหรับ FPGA การอัปเดตสามารถกำหนดเวลา แบ่งส่วน และปรับแต่งตามเงื่อนไขตามผู้ใช้ได้ ประการสุดท้ายบันทึกการใช้งานผู้ใช้สามารถแก้ไขปรับปรุงและเชื่อมโยงกับการใช้งานเฉพาะได้ จากชุดข้อมูลเหล่านี้สามารถปรับปรุงและพัฒนาประสิทธิภาพต่อไปได้ แม้หลังจากที่ผลิตภัณฑ์อยู่ในฟิล์ดแล้ว

บางทีจุดแข็งของความสามารถในการอัปเดตระบบทั้งหมดนี้ไม่ได้สำคัญมากนักในการใช้งานในอวกาศ เมื่อเปิดใช้งานผลิตภัณฑ์แล้วจะต้องดำเนินการบำรุงรักษาและอัปเดตจากระยะไกล ซึ่งอาจทำได้ง่ายเพียงแค่เปลี่ยนเงื่อนไขลอจิก หรือซับซ้อนเท่าการอัปเดตรูปแบบการปรับการสื่อสาร ความสามารถในการตั้งโปรแกรมของเทคโนโลยี FPGA และสถาปัตยกรรมตัวประมวลผลร่วมสามารถรองรับความสามารถทั้งหมดนี้ได้ในขณะที่เสนอทางเลือกส่วนประกอบที่ชุบแข็งด้วยรังสี

ประเด็นสำคัญขั้นสุดท้ายจากขั้นตอนนี้คือการลดต้นทุนแบบก้าวหน้า การลดต้นทุน การเปลี่ยนแปลงรายการวัสดุ (BOM) และการเพิ่มประสิทธิภาพอื่น ๆ สามารถเกิดขึ้นได้ในขั้นตอนนี้ ในระหว่างการปรับใช้จริง อาจมีการค้นพบว่าผลิตภัณฑ์สามารถทำงานได้ดีกับ MCU ที่มีราคาไม่แพง หรือ FPGA ที่มีความสามารถน้อยกว่า เนื่องจากตัวประมวลผลร่วม นักออกแบบสถาปัตยกรรมจึงไม่ติดขัดในการใช้ส่วนประกอบที่มีความสามารถเกินความต้องการสำหรับการใช้งาน นอกจากนี้หากส่วนประกอบไม่พร้อมใช้งาน สถาปัตยกรรมช่วยให้สามารถรวมส่วนประกอบใหม่เข้ากับการออกแบบได้ ซึ่งไม่ใช่กรณีที่มีสถาปัตยกรรมระบบบนชิป (SoC) ชิปเดียว หรือกับ DSP หรือ MCU ประสิทธิภาพสูงที่พยายามจัดการการประมวลผลของผลิตภัณฑ์ทั้งหมด สถาปัตยกรรมตัวประมวลผลร่วมเป็นการผสมผสานที่ดีระหว่างความสามารถและความยืดหยุ่น ทำให้นักออกแบบมีทางเลือกและเสรีภาพมากขึ้นทั้งในขั้นตอนการพัฒนาและเมื่อออกสู่ตลาด

สนับสนุนการวิจัยและกรณีศึกษาที่เกี่ยวข้อง

ตัวอย่างการสื่อสารผ่านดาวเทียม

โดยย่อแล้วคุณค่าของตัวประมวลผลร่วมคือการลดภาระของหน่วยประมวลผลหลักเพื่อให้งานต่าง ๆ ใช้งานบนฮาร์ดแวร์ ซึ่งสามารถใช้ประโยชน์จากการเพิ่มความเร็วและการเพิ่มประสิทธิภาพได้ ข้อดีของตัวเลือกการออกแบบดังกล่าวคือการเพิ่มความเร็วและความสามารถในการคำนวณโดยรวม และการลดต้นทุนการพัฒนาและเวลาในการพัฒนาตามที่บทความนี้ระบุ บางทีขอบเขตที่น่าสนใจที่สุดประการหนึ่งสำหรับประโยชน์เหล่านี้คือในด้านระบบการสื่อสารในอวกาศ

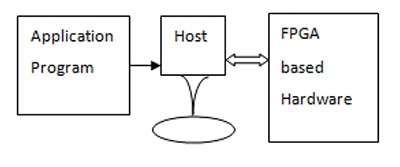

ในงานวิจัยของพวกเขาฮาร์ดแวร์ที่ใช้ FPGA เป็นตัวประมวลผลร่วม, G. Prasad และ N. Vasantha ให้ข้อมูลว่าการประมวลผลข้อมูลภายใน FPGA ผสมผสานความต้องการด้านการคำนวณของระบบสื่อสารผ่านดาวเทียมโดยไม่ต้องเสียค่าใช้จ่ายด้านวิศวกรรม (NRE) สูงสำหรับวงจรรวมแอพพลิเคชั่นเฉพาะ (ASIC) หรือข้อจำกัดเฉพาะแอปพลิเคชันของตัวประมวลผลฮาร์ดสถาปัตยกรรม ดังที่อธิบายไว้ในขั้นตอนการประมวลผลสัญญาณดิจิตอลด้วยไมโครคอนโทรลเลอร์ การออกแบบนั้นเริ่มต้นด้วยตัวประมวลผลแอปพลิเคชันที่ดำเนินการอัลกอริธึมที่เน้นการคำนวณเป็นส่วนใหญ่ จากจุดเริ่มต้นนี้พวกเขาระบุส่วนสำคัญของซอฟต์แวร์ที่ใช้วงจรนาฬิกาของหน่วยประมวลผลกลาง (CPU) ส่วนใหญ่ และย้ายส่วนเหล่านี้ไปยังการใช้งาน HDL การนำเสนอแบบกราฟิกมีความคล้ายคลึงกับสิ่งที่นำเสนอจนถึงขณะนี้ อย่างไรก็ตาม พวกเขาได้เลือกที่จะเป็นตัวแทนของโปรแกรมแอปพลิเคชัน เป็นบล็อกอิสระของตัวเอง เนื่องจากสามารถรับรู้ได้ในโฮสต์ (ตัวประมวลผล) หรือในฮาร์ดแวร์ที่ใช้ FPGA

รูปที่ 4: โปรแกรมแอปพลิเคชัน ตัวประมวลผลโฮสต์ และฮาร์ดแวร์ที่ใช้ FPGA ในตัวอย่างการสื่อสารผ่านดาวเทียม

รูปที่ 4: โปรแกรมแอปพลิเคชัน ตัวประมวลผลโฮสต์ และฮาร์ดแวร์ที่ใช้ FPGA ในตัวอย่างการสื่อสารผ่านดาวเทียม

ด้วยการใช้อินเทอร์เฟซการเชื่อมต่อระหว่างส่วนประกอบอุปกรณ์ต่อพ่วง (PCI) และการเข้าถึงหน่วยความจำโดยตรงของโปรเซสเซอร์โฮสต์ (DMA) ประสิทธิภาพของอุปกรณ์ต่อพ่วงจะเพิ่มขึ้นอย่างมาก ซึ่งส่วนใหญ่จะสังเกตเห็นในการพัฒนากระบวนการ Derandomization เมื่อดำเนินการตามกระบวนการนี้ในซอฟต์แวร์ของตัวประมวลผลโฮสต์ พบว่ามีคอขวดในการตอบสนองแบบเรียลไทม์ของระบบอย่างชัดเจน อย่างไรก็ตามเมื่อย้ายไปที่ FPGA จะสังเกตเห็นประโยชน์ดังต่อไปนี้:

- ดำเนินกระบวนการ Derandomization แบบเรียลไทม์โดยไม่ทำให้เกิดปัญหาคอขวด

- การทำงานในการคำนวณของโปรเซสเซอร์โฮสต์ลดลงอย่างมาก และขณะนี้สามารถทำหน้าที่บันทึกที่ต้องการได้ดีขึ้น

- ประสิทธิภาพโดยรวมของทั้งระบบเพิ่มมากขึ้น

ทั้งหมดนี้ทำได้โดยไม่มีค่าใช้จ่ายที่เกี่ยวข้องกับ ASIC และในขณะที่เพลิดเพลินกับความยืดหยุ่นของลอจิกที่ตั้งโปรแกรมได้ [5] การสื่อสารผ่านดาวเทียมทำให้เกิดความท้าทายอย่างมาก และวิธีการนี้สามารถพิสูจน์ได้ว่าแนวทางนี้ตรงตามข้อกำหนดเหล่านี้ และยังคงให้ความยืดหยุ่นในการออกแบบ

ตัวอย่างด้านระบบให้ข้อมูลและความบันเทิงในยานยนต์

ระบบความบันเทิงภายในรถยนต์เป็นคุณลักษณะที่แตกต่างสำหรับผู้บริโภคช่างเลือก อุปกรณ์เหล่านี้ต่างจากอุปกรณ์อิเล็กทรอนิกส์สำหรับยานยนต์ส่วนใหญ่ โดยอุปกรณ์เหล่านี้มองเห็นได้ชัดเจนและจะให้เวลาตอบสนองและประสิทธิภาพที่ยอดเยี่ยม อย่างไรก็ตามนักออกแบบมักถูกบีบคั้นให้เลือกระหว่างความต้องการในปัจจุบันของการออกแบบและความยืดหยุ่น ซึ่งเป็นคุณสมบัติในอนาคตต้องการ สำหรับตัวอย่างนี้จะใช้ความต้องการในการใช้งานของการประมวลผลสัญญาณและการสื่อสารไร้สาย เพื่อเน้นจุดแข็งของสถาปัตยกรรมฮาร์ดแวร์ตัวประมวลผลร่วม

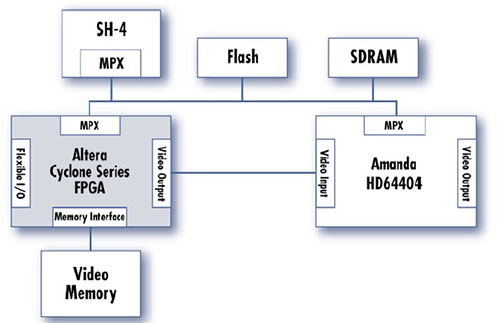

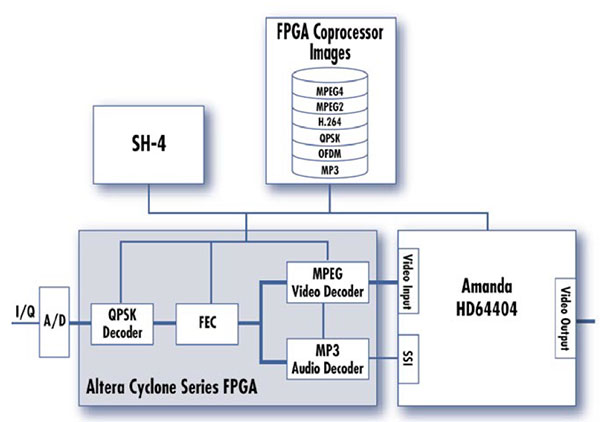

หนึ่งในสถาปัตยกรรมระบบความบันเทิงในยานยนต์ที่โดดเด่นของบริษัท Delphi Delco Electronics Systems สถาปัตยกรรมนี้ใช้ SH-4 MCU ร่วมกับอุปกรณ์ต่อพ่วง ASIC, HD64404 Amanda ของ Hitachi สถาปัตยกรรมนี้ได้รับความพึงพอใจมากกว่า 75% ของฟังก์ชันความบันเทิงพื้นฐานของตลาดยานยนต์ อย่างไรก็ตามก็ขาดความสามารถในการจัดการกับแอปพลิเคชั่นประมวลผลวิดีโอและการสื่อสารไร้สาย การรวม FPGA ไว้ในสถาปัตยกรรมที่มีอยู่นี้สามารถเพิ่มความยืดหยุ่นและความสามารถเพิ่มเติมให้กับแนวทางการออกแบบที่มีอยู่แล้วนี้ได้

รูปที่ 5: สถาปัตยกรรมตัวประมวลผลร่วม FPGA ในระบบให้ข้อมูลและความบันเทิง 1

รูปที่ 5: สถาปัตยกรรมตัวประมวลผลร่วม FPGA ในระบบให้ข้อมูลและความบันเทิง 1

สถาปัตยกรรมรูปที่ 5 เหมาะสำหรับทั้งการประมวลผลวิดีโอและการจัดการการสื่อสารไร้สาย โดยการผลักดันฟังก์ชัน DSP ไปยัง FPGA ซึ่งตัวประมวลผล Amanda สามารถทำหน้าที่จัดการระบบและมีอิสระในการใช้สแต็กการสื่อสารไร้สาย โดยทั้ง Amanda และ FPGA สามารถเข้าถึงหน่วยความจำภายนอก สามารถแลกเปลี่ยนข้อมูลระหว่างตัวประมวลผลและส่วนประกอบของระบบได้อย่างรวดเร็ว

รูปที่ 6: สถาปัตยกรรมตัวประมวลผลร่วม FPGA ในระบบให้ข้อมูลและความบันเทิง 2

รูปที่ 6: สถาปัตยกรรมตัวประมวลผลร่วม FPGA ในระบบให้ข้อมูลและความบันเทิง 2

ตัวอย่างที่สองของระบบให้ข้อมูลและความบันเทิงในรูปที่ 6 เน้นย้ำถึงความสามารถของ FPGA ในการระบุทั้งข้อมูลแอนะล็อกความเร็วสูงที่เข้ามา และการจัดการการบีบอัดและการเข้ารหัสที่จำเป็นสำหรับแอปพลิเคชันวิดีโอ แท้จริงแล้วฟังก์ชันทั้งหมดนี้สามารถใส่ลงใน FPGA และผ่านการใช้การประมวลผลแบบขนาน โดยทั้งหมดนี้สามารถแก้ไขได้แบบเรียลไทม์

การรวม FPGA ไว้ในสถาปัตยกรรมฮาร์ดแวร์ที่มีอยู่ ทำให้ฮาร์ดแวร์ที่มีอยู่มีประสิทธิภาพที่ผ่านการพิสูจน์ พร้อมกับมีความยืดหยุ่นและการใช้งานได้ในอนาคต แม้แต่ภายในระบบที่มีอยู่สถาปัตยกรรมตัวประมวลผลร่วมยังให้ตัวเลือกแก่นักออกแบบที่ไม่อาจหาได้[6]

ข้อดีของการสร้างต้นแบบอย่างรวดเร็ว

หัวใจของกระบวนการสร้างต้นแบบที่รวดเร็วนั้นมุ่งมั่นที่จะครอบคลุมพื้นที่การพัฒนาผลิตภัณฑ์จำนวนมากโดยดำเนินงานควบคู่กัน ระบุ "ข้อบกพร่อง" และปัญหาการออกแบบอย่างรวดเร็ว ตลอดจนตรวจสอบความถูกต้องของข้อมูลและเส้นทางสัญญาณ โดยเฉพาะอย่างยิ่งภายในเส้นทางที่สำคัญของโครงการ อย่างไรก็ตามจะต้องอาศัยความเชี่ยวชาญเพียงพอในในด้านที่จำเป็น เพื่อให้กระบวนการนี้สร้างผลลัพธ์ที่คล่องตัวและมีประสิทธิภาพอย่างแท้จริง

แต่เดิมแล้วนี่หมายความว่าจะต้องมีวิศวกรฮาร์ดแวร์ ซอฟต์แวร์ระบบฝังตัว หรือวิศวกร DSP และวิศวกร HDL ขณะนี้มีผู้เชี่ยวชาญหลากหลายสาขาที่อาจเชี่ยวชาญในหลายบทบาท อย่างไรก็ตามก็ยังมีค่าใช้จ่ายโครงการจำนวนมากที่เกี่ยวข้องกับการประสานงานเหล่านี้

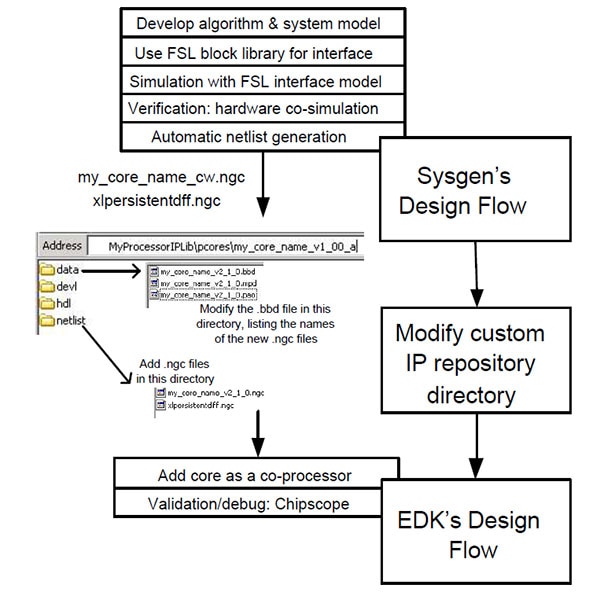

ในบทความของพวกเขา แพลตฟอร์มการสร้างต้นแบบอย่างรวดเร็วบน FPGA สำหรับตัวประมวลผลร่วมเวฟเล็ต ผู้เขียนสนับสนุนแนวคิดการใช้สถาปัตยกรรมตัวประมวลผลร่วมช่วยให้วิศวกร DSP คนเดียวสามารถตอบสนองบทบาทเหล่านี้ทั้งหมดได้อย่างมีประสิทธิภาพและประสิทธิผล สำหรับงานวิจัยนี้ ทีมงานได้เริ่มออกแบบและจำลองฟังก์ชัน DSP ที่ต้องการโดยใช้เครื่องมือ Simulink ของ MATLAB ซึ่งทำหน้าที่หลักสองอย่าง 1) ตรวจสอบประสิทธิภาพที่ต้องการผ่านการจำลอง และ 2) ทำหน้าที่เป็นข้อมูลฐานสำหรับเปรียบเทียบและอ้างอิงตัวเลือกการออกแบบในอนาคตได้

หลังจากการจำลองฟังก์ชันการทำงานที่สำคัญจะถูกระบุและแบ่งออกเป็นคอร์ต่าง ๆ ซึ่งเป็นส่วนประกอบและตัวประมวลผลแบบซอฟต์คอร์ที่สามารถสังเคราะห์ได้ภายใน FPGA ขั้นตอนที่สำคัญที่สุดคือการกำหนดอินเทอร์เฟซระหว่างคอร์และส่วนประกอบเหล่านี้ และการเปรียบเทียบประสิทธิภาพการแลกเปลี่ยนข้อมูลกับประสิทธิภาพจำลองที่ต้องการ ขั้นตอนการออกแบบนี้สอดคล้องอย่างใกล้ชิดกับขั้นตอนการออกแบบของ Xilinx สำหรับระบบฝังตัว และสรุปไว้ในรูปที่ 7 ด้านล่าง

รูปที่ 7: ขั้นตอนการออกแบบการดำเนินการ

รูปที่ 7: ขั้นตอนการออกแบบการดำเนินการ

วิศวกร DSP สามารถมุ่งเน้นไปที่แง่มุมที่สำคัญที่สุดของห่วงโซ่การประมวลผลสัญญาณ โดยการแบ่งระบบออกเป็นแกนที่สังเคราะห์ได้ เธอหรือเขาไม่จำเป็นต้องเป็นผู้เชี่ยวชาญด้านฮาร์ดแวร์หรือ HDL เพื่อแก้ไข กำหนดเส้นทาง หรือใช้ตัวประมวลผลหรือส่วนประกอบซอฟต์คอร์ที่แตกต่างกันภายใน FPGA ตราบใดที่ผู้ออกแบบตระหนักถึงอินเทอร์เฟซและรูปแบบของข้อมูล พวกเขาจะสามารถควบคุมเส้นทางสัญญาณได้อย่างสมบูรณ์และสามารถปรับแต่งประสิทธิภาพของระบบได้

ผลการวิจัยเชิงประจักษ์ – กรณีศึกษาการแปลงโคไซน์แบบไม่ต่อเนื่อง

ผลการวิจัยเชิงประจักษ์ไม่เพียงแต่ยืนยันความยืดหยุ่นของสถาปัตยกรรมตัวประมวลผลร่วมให้กับผู้ออกแบบระบบฝังตัวเท่านั้น แต่ยังแสดงตัวเลือกการเพิ่มประสิทธิภาพที่มีให้พร้อมกับเครื่องมือ FPGA ที่ทันสมัยอีกด้วย การเพิ่มประสิทธิภาพ เช่นเดียวกับที่กล่าวถึงด้านล่าง อาจไม่พร้อมใช้งานหรืออาจส่งผลกระทบน้อยกว่าสำหรับสถาปัตยกรรมฮาร์ดแวร์อื่น ๆ การแปลงโคไซน์แบบไม่ต่อเนื่อง (DCT) ได้รับเลือกให้เป็นอัลกอริธึมที่เน้นการคำนวณ และความก้าวหน้าจากการนำไปใช้งานโดยใช้ภาษา C ไปจนถึงการใช้งานโดยใช้ HDL เป็นหัวใจสำคัญของผลการวิจัยนี้ DCT ได้รับเลือกเนื่องจากอัลกอริธึมนี้ใช้ในการประมวลผลสัญญาณดิจิตอลสำหรับการจดจำรูปแบบและการกรอง[8] ผลการวิจัยเชิงประจักษ์มาจากการใช้งานในห้องปฏิบัติการโดยผู้เขียนและเพื่อนร่วมงาน เพื่อขอรับใบรับรอง Xilinx Alliance Partner สำหรับปี 2020 - 2021

เครื่องมือและอุปกรณ์ต่อไปนี้ถูกใช้ในงานวิจัยนี้:

- Vivado HLS v2019

- อุปกรณ์สำหรับการประเมินและการจำลองคือ xczu7ev-ffvc1156-2-e

เริ่มด้วยการใช้งานโดยใช้ภาษา C ซึ่งอัลกอริธึม DCT ยอมรับอาร์เรย์สองอาร์เรย์ที่มีตัวเลข 16 บิต โดยที่อาร์เรย์ "a" คืออาร์เรย์อินพุตของ DCT และอาร์เรย์ "b" คืออาร์เรย์เอาต์พุตจาก DCT ความกว้างของข้อมูล (DW) จึงถูกกำหนดเป็น 16 และจำนวนขององค์ประกอบภายในอาร์เรย์ (N) คือ 1024/DW หรือ 64 สุดท้ายนี้ ขนาดของเมทริกซ์ DCT (DCT_SIZE) ถูกตั้งค่าเป็น 8 ซึ่งหมายความว่าใช้เมทริกซ์ขนาด 8 x 8

ตามสมมติฐานของบทความนี้ การใช้อัลกอริทึมภาษา C ช่วยให้ผู้ออกแบบสามารถพัฒนาและตรวจสอบการทำงานของอัลกอริทึมได้อย่างรวดเร็ว แม้ว่าจะเป็นข้อพิจารณาที่สำคัญ แต่การตรวจสอบนี้ทำให้ฟังก์ชันการทำงานมีน้ำหนักที่สูงกว่าเวลาดำเนินการ โดยอนุญาตให้ใช้การถ่วงน้ำหนักนี้ เนื่องจากการใช้งานอัลกอริธึมขั้นสุดท้ายจะอยู่ใน FPGA ซึ่งการเร่งฮาร์ดแวร์ การคลายลูป และเทคนิคอื่น ๆ จะพร้อมใช้งาน

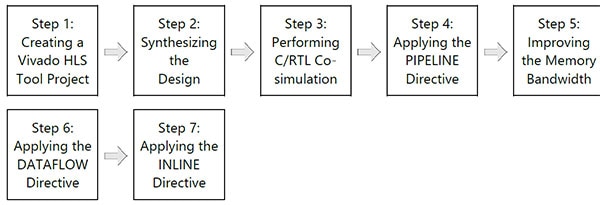

รูปที่ 8: ขั้นตอนการออกแบบ Xilinx Vivado HLS

รูปที่ 8: ขั้นตอนการออกแบบ Xilinx Vivado HLS

เมื่อสร้างรหัส DCT ภายในเครื่องมือ Vivado HLS เป็นโครงการ ขั้นตอนต่อไปคือการเริ่มสังเคราะห์การออกแบบสำหรับการใช้งาน FPGA ในขั้นตอนต่อไปนี้จะมีประโยชน์ที่ส่งผลกระทบมากที่สุดจากการย้ายการใช้งานอัลกอริทึมจาก MCU ไปยัง FPGA ที่ชัดเจนยิ่งขึ้น เนื่องจากขั้นตอนอ้างอิงนี้เทียบเท่ากับขั้นตอนการจัดการระบบด้วยของไมโครคอนโทรลเลอร์ที่กล่าวถึงข้างต้น

เครื่องมือ FPGA แบบใหม่ช่วยให้มีชุดการเพิ่มประสิทธิภาพและการปรับปรุงที่ช่วยเพิ่มประสิทธิภาพการทำงานของอัลกอริธึมที่ซับซ้อนได้อย่างมาก ก่อนวิเคราะห์ผลลัพธ์ มีข้อกำหนดสำคัญบางประการที่ควรทราบ:

- เวลาแฝง – จำนวนรอบของสัญญาณนาฬิกาที่จำเป็นในการดำเนินการใช้งานการวนซ้ำทั้งหมดของลูป [10]

- ช่วงเวลา – จำนวนรอบสัญญาณนาฬิกาก่อนการวนซ้ำรอบถัดไปจะเริ่มประมวลผลข้อมูล [11]

- BRAM - บล็อกหน่วยความจำเข้าถึงโดยสุ่ม

- DSP48E – ชิ้นส่วนประมวลผลสัญญาณดิจิตอลสำหรับสถาปัตยกรรม UltraScale

- FF – ฟลิปฟล็อป

- LUT – ตารางค้นหา

- URAM – Unified Random-Access Memory (อาจมีเพียงทรานซิสเตอร์ตัวเดียว)

|

||||||||||||||||||||||||||||||||||||||||

ตารางที่ 1: ผลการวิจัยของการเพิ่มประสิทธิภาพการดำเนินการอัลกอริทึม FPGA (เวลาแฝงและช่วงเวลา)

|

ตารางที่ 2: การค้นหาการเพิ่มประสิทธิภาพการดำเนินการอัลกอริทึม FPGA (การใช้ทรัพยากร)

ค่าเริ่มต้น

การตั้งค่าการปรับให้เหมาะสมเบื้องต้นมาจากผลลัพธ์ที่ไม่เปลี่ยนแปลงของการแปลอัลกอริทึมภาษา C เป็น HDL ที่สังเคราะห์ได้ โดยไม่มีการเปิดใช้การปรับให้เหมาะสม และสามารถใช้เป็นข้อมูลอ้างอิงประสิทธิภาพเพื่อให้เข้าใจถึงการเพิ่มประสิทธิภาพอื่น ๆ ได้ดีขึ้น

ไปป์ไลน์อินเนอร์ลูป

คำสั่ง ไปป์ไลน์ สั่งให้ Vivado HLS คลายลูปภายใน เพื่อให้ข้อมูลใหม่สามารถเริ่มประมวลผลได้ในขณะที่ข้อมูลที่มีอยู่ยังอยู่ในไปป์ไลน์ ดังนั้นข้อมูลใหม่จึงไม่ต้องรอให้ข้อมูลที่มีอยู่แล้วประมวลผลเสร็จก่อนจึงจะเริ่มต้นการประมวลผลได้

ไปป์ไลน์เอาท์เตอร์ลูป

ใช้คำสั่ง ไปป์ไลน์ กับเอาท์เตอร์ลูป ทำให้มีการดำเนินการที่เอาท์เตอร์ลูป อย่างไรก็ตามการดำเนินการของอินเนอร์ลูปก็เกิดขึ้นพร้อม ๆ กัน ซึ่งเวลาแฝงและช่วงเวลาจะลดลงครึ่งหนึ่ง โดยใช้คำสั่งนี้กับเอาท์เตอร์ลูปโดยตรง

การแบ่งพื้นที่อาร์เรย์

คำสั่งนี้จับคู่ข้อมูลของลูปกับอาร์เรย์และทำให้การเข้าถึงหน่วยความจำทั้งหมดเป็นองค์ประกอบเดียวภายในอาร์เรย์เหล่านี้ ซึ่งทำให้มีการใช้ RAM มากขึ้น แต่เวลาของการเรียกใช้อัลกอริธึมนี้จะลดลงครึ่งหนึ่ง

กระแสข้อมูล

คำสั่งนี้ช่วยให้ผู้ออกแบบสามารถระบุจำนวนรอบสัญญาณนาฬิกาเป้าหมายระหว่างข้อมูลแต่ละข้อมูลที่อ่านได้ คำสั่งนี้รองรับเฉพาะฟังก์ชันระดับบนเท่านั้น เฉพาะลูปและฟังก์ชันในระดับนี้จะได้รับประโยชน์จากคำสั่งนี้

อินไลน์

คำสั่ง อินไลน์ จัดการลูปทั้งหมดทั้งด้านในและด้านนอก โดยที่กระบวนการทั้งแถวและคอลัมน์สามารถดำเนินการพร้อมกัน จำนวนรอบสัญญาณนาฬิกาที่ต้องการจะถูกทำให้น้อยที่สุด แม้ว่าสิ่งนี้จะใช้ทรัพยากร FPGA มากกว่าก็ตาม

สรุป

สถาปัตยกรรมฮาร์ดแวร์ตัวประมวลผลร่วมนำเสนอแพลตฟอร์มประสิทธิภาพสูงให้แก่นักออกแบบแบบฝังตัวมีความยืดหยุ่นในการออกแบบตลอดการพัฒนาและการเปิดตัวผลิตภัณฑ์ที่ผ่านมา ด้วยการตรวจสอบความถูกต้องเบื้องต้นของอัลกอริธึมในภาษา C หรือ C++ ทำให้สามารถตรวจสอบกระบวนการ เส้นทางข้อมูลและสัญญาณ และฟังก์ชันการทำงานที่สำคัญได้ในระยะเวลาอันสั้น จากนั้นด้วยการแปลอัลกอริธึมที่ใช้ตัวประมวลผลเข้าไปในโปรเซสเซอร์ร่วม FPGA ผู้ออกแบบสามารถเพลิดเพลินกับประโยชน์ของการเพิ่มความเร็วของฮาร์ดแวร์และการออกแบบโมดูลาร์

หากชิ้นส่วนนั้นเลิกผลิตหรือจำเป็นต้องมีการปรับให้เหมาะสม สถาปัตยกรรมเดียวกันก็สามารถเปลี่ยนแปลงได้ MCU และ FPGA ใหม่สามารถติดตั้งให้เข้ากับการออกแบบได้ ในขณะที่อินเทอร์เฟซยังคงไม่เปลี่ยนแปลง นอกจากนี้เนื่องจากทั้ง MCU และ FPGA สามารถอัปเดตได้เมื่อติดตั้งแล้ว การเปลี่ยนแปลงตามความต้องการของผู้ใช้ และสามารถเพิ่มประสิทธิภาพเมื่อติดตั้งในอุปกรณ์และจากระยะไกลได้

สุดท้ายแล้วสถาปัตยกรรมนี้ผสมผสานความเร็วในการพัฒนาและความพร้อมใช้งานของ MCU กับประสิทธิภาพและความสามารถในการเพิ่มขยายของ FPGA ด้วยการปรับปรุงประสิทธิภาพและการพัฒนาการทำงานที่มีอยู่ในทุกขั้นตอนของการพัฒนา สถาปัตยกรรมตัวประมวลผลร่วมจึงสามารถตอบสนองความต้องการ แม้ว่าจะเป็นความต้องการที่ท้าทายที่สุดสำหรับการออกแบบในปัจจุบันและอื่น ๆ

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.