การเลือกและการใช้ FPGA สำหรับการเชื่อมต่อยานยนต์ ความปลอดภัย และโหลดที่เน้นการประมวลผล

Contributed By DigiKey's North American Editors

2022-01-12

ในวิธีการแบบเดิม งานคำนวณในรถยนต์ดำเนินการโดยไมโครคอนโทรลเลอร์ (MCU) และตัวประมวลผลแอปพลิเคชัน (AP) รถระดับกลางทั่วไปสามารถมี MCU/AP ได้ 25 ถึง 35 ตัว ในขณะที่รถยนต์หรูหราอาจใช้ 70 ตัวขึ้นไป รถยนต์ต้องการความสามารถที่ซับซ้อนและต้องใช้การคำนวณมากสำหรับงานต่าง ๆ เช่น ระบบช่วยเหลือผู้ขับขี่ขั้นสูง (ADAS) ระบบสาระบันเทิง การควบคุม เครือข่าย และการรักษาความปลอดภัย แอปพลิเคชันเหล่านี้จำนวนมากเกี่ยวข้องกับแมชชีนวิชันในรูปแบบของการประมวลผลภาพและวิดีโอร่วมกับปัญญาประดิษฐ์ (AI)

สถาปัตยกรรมโปรเซสเซอร์เพียงลำพังเท่านั้นที่จะจัดการกับอินเทอร์เฟซไฟฟ้าและโปรโตคอลทั้งหมดที่เป็นที่ต้องการของอุปกรณ์ต่อพ่วง เช่น เซ็นเซอร์ กล้อง และจอแสดงผล นอกจากนี้ ในหลายกรณี โปรเซสเซอร์เหล่านี้ไม่สามารถตอบสนองความต้องการด้านการคำนวณขั้นสูงของงาน เช่น แมชชีนวิชันและ AI

เพื่อจัดการกับความซับซ้อนนี้ นักออกแบบระบบยานยนต์จึงหันไปใช้ field-programmable gate arrays (FPGA) ไม่ใช่เพื่อแทนที่ MCU/AP ที่มีอยู่ แต่จะทำหน้าที่เป็นสะพานเชื่อมระหว่างพวกมันกับอุปกรณ์อื่น ๆ และเสริมด้วยการลดภาระการสื่อสารและ งานอื่น ๆ ที่ต้องใช้การคำนวณอย่างหนัก

เนื่องจากสามารถตั้งโปรแกรม FPGA ให้สนับสนุนอินเทอร์เฟซและโปรโตคอลทางไฟฟ้าได้หลากหลาย จึงทำหน้าที่เป็นสะพานเชื่อมระหว่าง MCU/AP และเซ็นเซอร์ กล้อง และจอแสดงผล นอกจากนี้ เนื่องจากสามารถคำนวณและดำเนินการในลักษณะคู่ขนานกันอย่างหนาแน่น FPGA จึงสามารถใช้เพื่อดำเนินการประมวลผลด้วยภาพและ AI ที่เน้นการประมวลผลด้วยคอมพิวเตอร์ ซึ่งจะทำให้โปรเซสเซอร์โฮสต์ว่างสำหรับกิจกรรมอื่น ๆ

บทความนี้กล่าวถึงข้อกำหนดในการประมวลผลของยานยนต์สมัยใหม่และอธิบายการใช้งานยานยนต์บางอย่างที่ FPGA สามารถแก้ไขได้ จากนั้นจะแนะนำตัวอย่าง FPGA จาก Lattice Semiconductor และแสดงให้เห็นว่าสามารถใช้แก้ปัญหาการเชื่อมต่อ การประมวลผล และความปลอดภัยได้อย่างไร นอกจากนี้ยังนำเสนอกระดานการพัฒนาที่เกี่ยวข้องเพื่อช่วยนักออกแบบในการเริ่มต้น

กำหนดเป้าหมายการใช้งานยานยนต์สำหรับ FPGAs

เพื่อรองรับความสามารถของ ADAS รถยนต์ในปัจจุบันจึงใช้เซ็นเซอร์จำนวนมากภายนอกรถ รวมถึงกล้อง เรดาร์ LiDAR และเครื่องตรวจจับอัลตราโซนิก ในหลายกรณี มีความจำเป็นต้องนำข้อมูลจากเซ็นเซอร์ที่แตกต่างกัน ประมวลผลข้อมูลนี้ล่วงหน้า (นำสัญญาณรบกวนออกและจัดรูปแบบตามต้องการ) และใช้การรวมเซ็นเซอร์เพื่อรวมข้อมูลเพื่อให้ข้อมูลที่ได้มีความไม่แน่นอนน้อยกว่าที่จะเป็นไปได้ ข้อมูลจากเซ็นเซอร์ต่างๆ จะถูกนำมาใช้เป็นรายบุคคล ในหลายกรณี มีการใช้แอปพลิเคชัน AI เพื่อวิเคราะห์ข้อมูล ตัดสินใจ และดำเนินการตามความเหมาะสม

แนวโน้มล่าสุดคือการใช้กระจกมองหลังแบบอิเล็กทรอนิกส์ (หรือที่เรียกว่า “ดิจิตอล”) ในกรณีนี้ กล้องมุมกว้างและความละเอียดสูงจะติดตั้งไว้ที่กระจกหลัง วิดีโอสตรีมจากกล้องนี้แสดงบนจอแสดงผลดิจิทัลที่มาแทนที่กระจกแบบเดิม ส่งผลให้มีมุมมองด้านหลังที่ชัดเจนซึ่งไม่มีสิ่งกีดขวางจากผู้โดยสารในเบาะหลัง ในบางกรณี วิดีโอสตรีมจากกล้องที่ติดตั้งบนกระจกมองข้างอาจรวมกับสตรีมวิดีโอจากกล้องที่กระจกด้านหลัง ฟีดทั้งสามนี้ "เย็บเข้าด้วยกัน" เพื่อให้เป็นภาพเดียวที่แสดงบนกระจกไฟฟ้าแบบกว้างพิเศษ ซึ่งจะทำให้ผู้ขับขี่มีระดับการตระหนักรู้ในสถานการณ์ที่สูงขึ้นมากเกี่ยวกับสิ่งที่เกิดขึ้นรอบรถ

แนวโน้มล่าสุดอีกประการหนึ่งคือการปรับใช้กล้องในห้องโดยสารที่ติดตั้งบนแผงหน้าปัด บนคอพวงมาลัย หรือรวมเข้ากับกระจกมองหลัง (แบบปกติหรือแบบอิเล็กทรอนิกส์) เมื่อใช้ร่วมกับ AI กระจกในห้องโดยสารเหล่านี้สามารถใช้งานได้หลากหลาย เช่น การจำแนกว่าใครนั่งอยู่บนเบาะคนขับและปรับกระจกและปรับกระจกตามนั้น นอกจากการเฝ้าติดตามผู้ขับเพื่อให้แน่ใจว่าพวกเขาใส่ใจกับท้องถนนและไม่งีบหลับ ระบบดังกล่าวยังสามารถค้นหาสัญญาณของอาการง่วงนอน ตลอดจนปัญหาทางการแพทย์หรือความทุกข์ เช่น อาการป่วยเป็นโรคลมบ้าหมูหรือหัวใจวาย และดำเนินการตามความเหมาะสม การกระทำเหล่านี้อาจรวมถึงการเปิดไฟเตือนอันตราย การเบรก และการนำรถไปด้านข้างถนน การใช้งานเพิ่มเติม ได้แก่ การดูแลเด็กและสัตว์เลี้ยงจะไม่ถูกทิ้งไว้โดยไม่มีใครดูแลโดยไม่ได้ตั้งใจในเบาะหลังโดยป้องกันไม่ให้รถถูกล็อคและกระพริบไฟ และแจ้งเตือนคนขับหากผู้โดยสารทิ้งโทรศัพท์ กระเป๋า หรือพัสดุไว้ที่เบาะหลัง

สำหรับแอปพลิเคชันที่ใช้วิดีโอ ในบางกรณี จำเป็นต้องแยกอินพุตวิดีโอเดียวออกเป็นหลายสตรีม ในส่วนอื่น ๆ ข้อกำหนดด้านการออกแบบอาจเป็นการรวมวิดีโอสตรีมหลายรายการเข้าเป็นไฟล์เดียว

ด้วยการใช้ยานพาหนะไฟฟ้า (EV) ที่เพิ่มขึ้น ความจำเป็นในการตรวจสอบและควบคุมมอเตอร์ ตลอดจนการตรวจสอบและจัดการกระบวนการชาร์จเพื่อให้มีอายุการใช้งานแบตเตอรี่สูงสุด

เหนือสิ่งอื่นใด รถยนต์จำนวนมากในปัจจุบันเริ่มที่จะเปิดใช้งาน 5G หรือ V2X โดยที่ V2X (“ยานพาหนะไปยังสิ่งใด”) หมายถึงการสื่อสารระหว่างยานพาหนะกับหน่วยงานอื่นใดที่อาจส่งผลกระทบ (หรือได้รับผลกระทบจาก) รถ จากโครงสร้างพื้นฐานริมถนนไปจนถึงยานพาหนะอื่นๆ นอกเหนือจากการเชื่อมต่อนี้ จำเป็นต้องมีการรักษาความปลอดภัยเพื่อป้องกันไม่ให้รถถูกแฮ็ก

อุปกรณ์เกรดยานยนต์

สิ่งสำคัญคือต้องจำไว้ว่า FPGA บางตัวอาจไม่เหมาะสำหรับการใช้งานในยานยนต์ สภาอิเล็กทรอนิกส์ยานยนต์ (AEC) เป็นองค์กรที่ก่อตั้งขึ้นในทศวรรษ 1990 โดยไครสเลอร์ ฟอร์ด และจีเอ็ม โดยมีวัตถุประสงค์เพื่อสร้างคุณสมบัติทั่วไปของชิ้นส่วนและมาตรฐานระบบคุณภาพ หนึ่งในเอกสาร AEC ที่อ้างอิงกันมากที่สุดคือ AEC-Q100 "คุณสมบัติการทดสอบความเครียดตามกลไกความล้มเหลวสำหรับวงจรรวม"

IATF 16949:2016 เป็นข้อกำหนดทางเทคนิคที่มุ่งพัฒนาระบบการจัดการคุณภาพซึ่งมีการปรับปรุงอย่างต่อเนื่อง โดยเน้นที่การป้องกันข้อบกพร่อง และลดการเปลี่ยนแปลงและของเสียในห่วงโซ่อุปทานของอุตสาหกรรมยานยนต์และกระบวนการประกอบ ตามมาตรฐาน ISO 9001 IATF 16949:2016 ถูกสร้างขึ้นโดย International Automotive Task Force (IATF) และคณะกรรมการด้านเทคนิคของ ISO

ซัพพลายเออร์ระบบอิเล็กทรอนิกส์สู่ตลาดยานยนต์ต้องการให้ซัพพลายเออร์เซมิคอนดักเตอร์จัดหาผลิตภัณฑ์ที่สอดคล้องกับมาตรฐาน AEC-Q100 และสามารถแสดงการรับรองระบบคุณภาพ ISO/TS-16949 ได้

การเลือก FPGA ให้เหมาะสมกับงาน

FPGA มีความยืดหยุ่นสูง แต่ตระกูลอุปกรณ์ต่างๆ มีความสามารถและฟังก์ชันต่าง ๆ ที่ผสมผสานกันเพื่อให้เหมาะกับงานที่เฉพาะเจาะจงมากขึ้น ในกรณีของแอปพลิเคชั่นวิชันซิสเต็ม ตัวอย่างเช่น กล้องและจอแสดงผลสมัยใหม่มักใช้อินเทอร์เฟซ MIPI โปรโตคอล MIPI CSI-2 (กล้อง/เซ็นเซอร์) และ DSI (จอแสดงผล) ใช้เลเยอร์การสื่อสารทางกายภาพ (PHY) ที่เรียกว่า D-PHY MCU/AP รุ่นเก่าอาจไม่รองรับอินเทอร์เฟซนี้ แต่ FPGA บางตัวรองรับ เช่น การมองเห็นแบบฝังของ CrossLink-NX และการประมวลผล FPGA จาก Lattice Semiconductor

นอกจากตัวรับส่งสัญญาณ MIPI D-PHY สี่เลนที่ชุบแข็งสองตัวที่รองรับ 10 กิกะบิตต่อวินาที (Gbits/s) ต่อ PHY แล้ว อุปกรณ์ CrossLink-NX ยังรองรับ 5 Gbits/s PCIe, 1.5 Gbits/s อินพุต/เอาต์พุตที่ตั้งโปรแกรมได้ (I/O ) และ 1066 เมกะบิตต่อวินาที (Mbits/s) DDR3 อุปกรณ์เหล่านี้ยังสนับสนุนอินเทอร์เฟซและโปรโตคอลทางไฟฟ้าแบบเดิม เช่น การส่งสัญญาณความแตกต่างของแรงดันต่ำ (LVDS), Sub-LVDS (LVDS เวอร์ชันลดแรงดันไฟฟ้า), Open LVDS Display Interface (OLDI) และอินเทอร์เฟซที่ไม่ขึ้นกับสื่อแบบกิกะบิตแบบอนุกรม (SGMII) ด้วยเหตุนี้ อุปกรณ์เหล่านี้จึงสามารถใช้สำหรับการรวมสตรีมวิดีโอ แยกสตรีมวิดีโอ เรียกใช้แอปพลิเคชัน AI และในขณะที่ทำทั้งหมดนี้ ยังทำหน้าที่เป็นสะพานเชื่อมระหว่าง MCU/AP แบบเดิมกับเซ็นเซอร์และจอแสดงผลสมัยใหม่

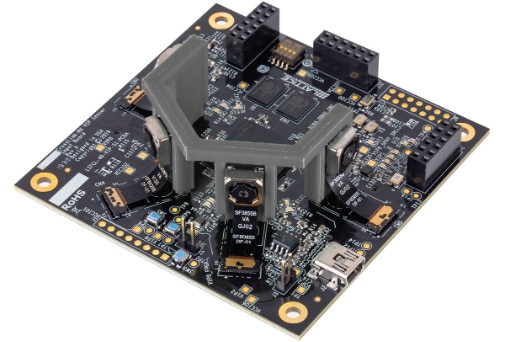

นักพัฒนาระบบยานยนต์ที่ต้องการประเมิน CrossLink-NX FPGA จะพบการรวมกันของLIFCL-VIP-SI-EVN บอร์ดอินพุตเซนเซอร์ CrossLink-NX VIP (รูปที่ 1) และLF-EVDK1-EVN Modular Embedded Vision Kit ที่น่าสนใจ (รุ่นก่อนสามารถทำหน้าที่เป็นบอร์ดอินพุตสำหรับรุ่นหลังได้) นอกจาก CrossLink-NX FPGA แล้ว บอร์ดอินพุตของเซนเซอร์ยังมีเซ็นเซอร์ภาพ Sony IMX258 CMOS MIPI ความละเอียด 13 ล้านพิกเซล จำนวน 13 ล้านพิกเซล รองรับ 4K2K @ 30 เฟรมต่อวินาที (fps) หรือ 1080p @ 60 fps นอกจากนี้ยังรองรับการเชื่อมต่อเซ็นเซอร์ที่ง่ายดายผ่านอินเทอร์เฟซ PMOD อิสระสามอินเทอร์เฟซ

รูปที่ 1: บอร์ดอินพุตเซ็นเซอร์ VIP ของ CrossLink-NX ซึ่งสามารถทำหน้าที่เป็นอินพุตไปยังชุดพัฒนาวิสัยทัศน์ที่ฝังตัว มี CrossLink-NX FPGA และรองรับการรวมเซ็นเซอร์ภาพ MIPI Sony IMX258 สี่ตัว (แหล่งรูปภาพ: Lattice Semiconductor)

รูปที่ 1: บอร์ดอินพุตเซ็นเซอร์ VIP ของ CrossLink-NX ซึ่งสามารถทำหน้าที่เป็นอินพุตไปยังชุดพัฒนาวิสัยทัศน์ที่ฝังตัว มี CrossLink-NX FPGA และรองรับการรวมเซ็นเซอร์ภาพ MIPI Sony IMX258 สี่ตัว (แหล่งรูปภาพ: Lattice Semiconductor)

สำหรับแอปพลิเคชันที่เน้นการประมวลผลซึ่งต้องการแบนด์วิดท์ I/O สูงเช่นกัน เช่น AI สำหรับงานต่างๆ เช่น การจดจำท่าทางและการควบคุม การจดจำเสียงและการควบคุม การตรวจจับการมีอยู่ของมนุษย์ การระบุผู้ครอบครอง และการตรวจสอบไดรเวอร์ — คุณสมบัติ ECP5 FPGA ของ Lattice สูงถึง 3.2 Gbit/ ซีเรียลไลเซอร์/ดีซีเรียลไลเซอร์ (SERDES) สูงสุดสี่ช่องต่ออุปกรณ์ในบล็อกแบบสองช่องสัญญาณสำหรับความละเอียดที่มากขึ้น ตารางค้นหา (LUT) สูงสุด 85K บล็อกการประมวลผลสัญญาณดิจิทัล (DSP) ที่ได้รับการปรับปรุงซึ่งให้การปรับปรุงทรัพยากร 2 เท่าสำหรับตัวกรองแบบสมมาตร และการสนับสนุนการบรรเทาปัญหาเหตุการณ์เดียว (SEU) FPGA เหล่านี้ยังให้การสนับสนุน I/O ที่ตั้งโปรแกรมได้สำหรับอินเทอร์เฟซ LVCMOS 33/25/18/15/12, XGMII, LVTTL, LVDS, Bus-LVDS, 7:1 LVDS, LVPECL และ MIPI D-PHY I/O

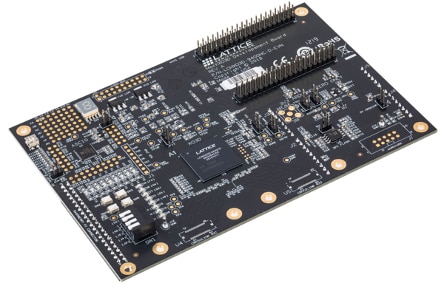

ตัวอย่างอุปกรณ์ ECP5 คือLFE5U-85F-6BG554C ด้วยองค์ประกอบลอจิก 84,000, 3.75 เมกะบิต (Mbits) ของ RAM และ 259 I/O ที่น่าสนใจก็คือ LFE5UM-45F-VERSA-EVNG ECP5 Versa Development Kit (รูปที่ 2) บอร์ดนี้ใช้ฟอร์มแฟคเตอร์ PCI Express (PCIe) ครึ่งความยาว และช่วยให้นักออกแบบสามารถประเมินคุณลักษณะการเชื่อมต่อที่สำคัญของ ECP5 FPGA ซึ่งรวมถึง PCIe, Gigabit Ethernet (GbE), DDR3 และประสิทธิภาพ SERDES ทั่วไป

รูปที่ 2: นำเสนอในรูปแบบ PCI Express ครึ่งความยาว ชุดพัฒนา ECPe Versa ช่วยให้นักออกแบบประเมินคุณสมบัติการเชื่อมต่อที่สำคัญของ ECP5 FPGA รวมถึง PCIe, GbE, DDR3 และประสิทธิภาพ SERDES ทั่วไป (แหล่งรูปภาพ: Lattice Semiconductor)

รูปที่ 2: นำเสนอในรูปแบบ PCI Express ครึ่งความยาว ชุดพัฒนา ECPe Versa ช่วยให้นักออกแบบประเมินคุณสมบัติการเชื่อมต่อที่สำคัญของ ECP5 FPGA รวมถึง PCIe, GbE, DDR3 และประสิทธิภาพ SERDES ทั่วไป (แหล่งรูปภาพ: Lattice Semiconductor)

การรักษาความปลอดภัยรถยนต์โดยใช้ FPGAs

ภัยคุกคามด้านความปลอดภัยจากการแฮ็กเพิ่มขึ้น โดยมีการละเมิดใหม่ๆ เกิดขึ้นอย่างต่อเนื่อง ในกรณีของรถยนต์ การโจมตีทางไซเบอร์อาจทำให้สูญเสียการควบคุม ส่งผลให้ผู้โดยสารและคนเดินเท้าได้รับบาดเจ็บหรือเสียชีวิต และความเสียหายต่อรถยนต์ ยานพาหนะอื่นๆ และทรัพย์สิน

โซลูชันด้านความปลอดภัยของรถยนต์ส่วนใหญ่คือการสร้างรากฐานของความไว้วางใจ (RoT) นั่นคือทรัพยากรฮาร์ดแวร์ภายในระบบที่สามารถเชื่อถือได้เสมอ โซลูชันหนึ่งคือฮาร์ดแวร์ RoT (HRoT) ที่ใช้ FPGA เช่นที่จัดหาโดยตระกูล MachXO3D ของ Lattice นอกจากทรัพยากร LUT จำนวนมากและ I/O จำนวนมากแล้ว อุปกรณ์ที่ใช้แฟลชเหล่านี้ยังมีความสามารถแบบ Instant-on และ Hot-socket การใช้งานเอนกประสงค์ ได้แก่ ลอจิกของกาว บัสบริดจ์ การเชื่อมต่อบัส การควบคุมมอเตอร์ การควบคุมการเปิดเครื่อง และการใช้งานลอจิกควบคุมอื่น ๆ

สิ่งที่น่าสนใจเป็นพิเศษคือข้อเท็จจริงที่ว่า MachXO3D เป็น FPGA เพียงตัวเดียวที่มีทั้งความสามารถในการบูตแบบดูอัลและน้อยกว่า 10K LUT ที่ติดตั้งกลไกการรักษาความปลอดภัยที่ไม่เปลี่ยนรูปซึ่งได้รับการรับรองจากสถาบันมาตรฐานและเทคโนโลยีแห่งชาติ (NIST) อย่างเข้มงวด สิ่งนี้ทำให้ MachXO3D ทำหน้าที่เป็น HRoT ของรถยนต์ในรูปแบบของอุปกรณ์ที่เปิดใช้งานครั้งแรกและครั้งสุดท้ายของระบบ เมื่อเปิดเครื่อง MachXO3D จะตรวจสอบก่อนเพื่อให้แน่ใจว่ากำลังเรียกใช้เฟิร์มแวร์ที่ตรวจสอบสิทธิ์ จากนั้นจะตรวจสอบเฟิร์มแวร์ของอุปกรณ์อื่น ๆ ในระบบ หากส่วนประกอบใด ๆ ในระบบถูกโจมตีหรือถูกบุกรุก รวมถึงตัวมันเอง MachXO3D จะปฏิเสธเฟิร์มแวร์ที่น่าสงสัยและโหลดส่วนประกอบนั้นใหม่ด้วยอิมเมจเฟิร์มแวร์ที่รู้จักและรับรองความถูกต้อง

สำหรับนักพัฒนาที่สนใจในการประเมินการออกแบบที่ใช้ MachXO3D, theLMXO3D-9400HC-D-EVN MachXO3D Development Board มีแพลตฟอร์มการสร้างต้นแบบที่ขยายได้ (รูปที่ 3) บอร์ดนี้มีอุปกรณ์จัดการฮาร์ดแวร์ L-ASC10 (ความรู้สึกและการควบคุมแบบแอนะล็อก) อินเทอร์เฟซ I/O อเนกประสงค์สำหรับใช้กับบอร์ด Arduino และ Raspberry Pi ตำแหน่งส่วนหัว Hirose FX12-40 (DNI) สองตำแหน่ง และส่วนหัว Aardvark (DNI) ) และแฟลชอินเทอร์เฟซอุปกรณ์ต่อพ่วงซีเรียล 128 Mbit (SPI) พร้อมคุณสมบัติการอ่านแบบสี่เหลี่ยม

รูปที่ 3: บอร์ดพัฒนา MachXO3D มี MachXO3D FPGA, อุปกรณ์จัดการฮาร์ดแวร์ L-ASC10 (ความรู้สึกและการควบคุมแบบอนาล็อก), รองรับบอร์ด Arduino และ Raspberry Pi, ตำแหน่งส่วนหัว Hirose FX12-40 (DNI) สองตำแหน่ง, ส่วนหัว Aardvark และ การเชื่อมต่อ USB-B สำหรับการเขียนโปรแกรมอุปกรณ์ (แหล่งรูปภาพ: Lattice Semiconductor)

รูปที่ 3: บอร์ดพัฒนา MachXO3D มี MachXO3D FPGA, อุปกรณ์จัดการฮาร์ดแวร์ L-ASC10 (ความรู้สึกและการควบคุมแบบอนาล็อก), รองรับบอร์ด Arduino และ Raspberry Pi, ตำแหน่งส่วนหัว Hirose FX12-40 (DNI) สองตำแหน่ง, ส่วนหัว Aardvark และ การเชื่อมต่อ USB-B สำหรับการเขียนโปรแกรมอุปกรณ์ (แหล่งรูปภาพ: Lattice Semiconductor)

บอร์ดมาในฟอร์มแฟคเตอร์ขนาด 4 x 6 นิ้ว และมีขั้วต่อ USB mini-B สำหรับจ่ายไฟและตั้งโปรแกรม และตำแหน่งส่วนหัวหลายตำแหน่งที่รองรับ Arduino, Aardvark, FX12, Hirose และ Raspberry Pi มีทั้งสาย USB และคู่มือเริ่มต้นใช้งานฉบับย่อ

บทสรุป

อุปกรณ์อิเล็กทรอนิกส์สำหรับยานยนต์สมัยใหม่ต้องการเซ็นเซอร์ อินเทอร์เฟซทางไฟฟ้า และโปรโตคอลที่เพิ่มมากขึ้นเรื่อย ๆ โดยมีความต้องการพลังงานและแบนด์วิธในการประมวลผลที่สอดคล้องกัน การเพิ่มการประมวลผล AI และแมชชีนวิชัน ตลอดจนข้อกำหนดด้านความปลอดภัย ทำให้การใช้งานโซลูชันยุ่งยากโดยใช้แนวทาง MCU หรือ AP แบบคลาสสิก

ดังที่แสดงไว้ โดยการใช้ FPGA อย่างเหมาะสม นักออกแบบสามารถเพิ่มระดับของความยืดหยุ่นและกำลังในการประมวลผลที่สามารถเชื่อมสภาพแวดล้อมการประมวลผลที่แตกต่างกัน ดำเนินการรวมเซ็นเซอร์และฟังก์ชันฟิวชั่น ระบุข้อกำหนดแบนด์วิดท์ I/O และดำเนินการคำนวณและดำเนินการในลักษณะขนานกันอย่างหนาแน่น ในขณะที่เพิ่มพื้นที่โปรเซสเซอร์โฮสต์สำหรับกิจกรรมอื่น ๆ

เพื่อความปลอดภัย FPGA แบบแฟลชพร้อมความสามารถในการบูตแบบดูอัลและ Immutable Security Engine ที่ได้รับการรับรองจาก NIST สามารถทำหน้าที่เป็น HRoT ของรถยนต์และช่วยให้มั่นใจได้ว่าอุปกรณ์ดังกล่าว—และอุปกรณ์อื่น ๆ— ใช้งานเฉพาะเฟิร์มแวร์ที่ตรวจสอบสิทธิ์แล้วเท่านั้น จึงป้องกันแฮกเกอร์จากการบุกรุกระบบของรถยนต์ด้วยการเข้ารหัสลับ

อ่านเพิ่มเติม:

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.