การใช้เครื่องรับส่งสัญญาณ RF แบบ Agile ในระบบการสื่อสาร SDR แบบปรับเปลี่ยนได้สำหรับอากาศยานและการป้องกันประเทศ

Contributed By DigiKey's North American Editors

2023-11-30

ผู้ออกแบบระบบอากาศยานและการป้องกันประเทศ (ADEF) เผชิญกับความต้องการในการใช้พลังงานน้อยลงและระบบการสื่อสารที่มีขนาดกะทัดรัดมากขึ้นซึ่งมีความสามารถในการตอบสนองต่อสภาพแวดล้อมของสัญญาณไดนามิกที่คล่องตัว ซึ่งเทคโนโลยีวิทยุที่กำหนดโดยซอฟต์แวร์ (SDR) ก้าวไปไกลกว่าสถาปัตยกรรมวิทยุแบบดั้งเดิม สามารถช่วยตอบสนองข้อกำหนดที่เปลี่ยนแปลงอย่างรวดเร็วสำหรับวิทยุ ADEF แต่การนำ SDR ไปใช้ทำให้เกิดความท้าทายหลายประการในการตอบสนองทั้งข้อกำหนดด้านการทำงานและความจำเป็นในการลดขนาด น้ำหนัก และกำลัง (SWaP)

บทความนี้จะอธิบายโซลูชัน SDR ที่มีประสิทธิภาพมากขึ้นจาก Analog Devices ที่สามารถลดความซับซ้อนในการออกแบบระบบการสื่อสารที่ใช้พลังงานต่ำ กะทัดรัด และคล่องตัว โดยไม่กระทบต่อประสิทธิภาพการทำงาน

ความท้าทายที่เกิดขึ้นใหม่ผลักดันให้เกิดความต้องการที่มากขึ้นเรื่อย ๆ

นักออกแบบเผชิญกับความต้องการการสื่อสารที่มีประสิทธิภาพมากขึ้นในการใช้งานทางอุตสาหกรรมและภารกิจที่สำคัญซึ่งมีจำนวนเพิ่มมากขึ้น รวมถึงการสื่อสารทางวิทยุที่ปลอดภัย, เรดาร์แบบปรับเปลี่ยนได้, สงครามอิเล็กทรอนิกส์ และการนำทาง GPS ที่ได้รับการปรับปรุง โดยความท้าทายใหม่เหล่านี้ผลักดันให้เกิดความจำเป็นในการดำเนินงานย่านความถี่กว้างที่ได้รับการปรับปรุง ช่วงไดนามิกที่สูงขึ้น ความคล่องตัวของความถี่ที่มากขึ้น และการกำหนดค่าใหม่ได้ อย่างไรก็ตาม ข้อกำหนดด้านการทำงานที่มากยิ่งขึ้นเหล่านี้อาจขัดแย้งกับความต้องการ SWaP ที่ต่ำลง เนื่องจากระบบการสื่อสารนั้นเปลี่ยนไปอยู่บนแพลตฟอร์มที่ใช้พลังงานแบตเตอรี่ขนาดเล็ก รวมถึงยานพาหนะทางอากาศไร้คนขับ (UAS) และอุปกรณ์พกพา

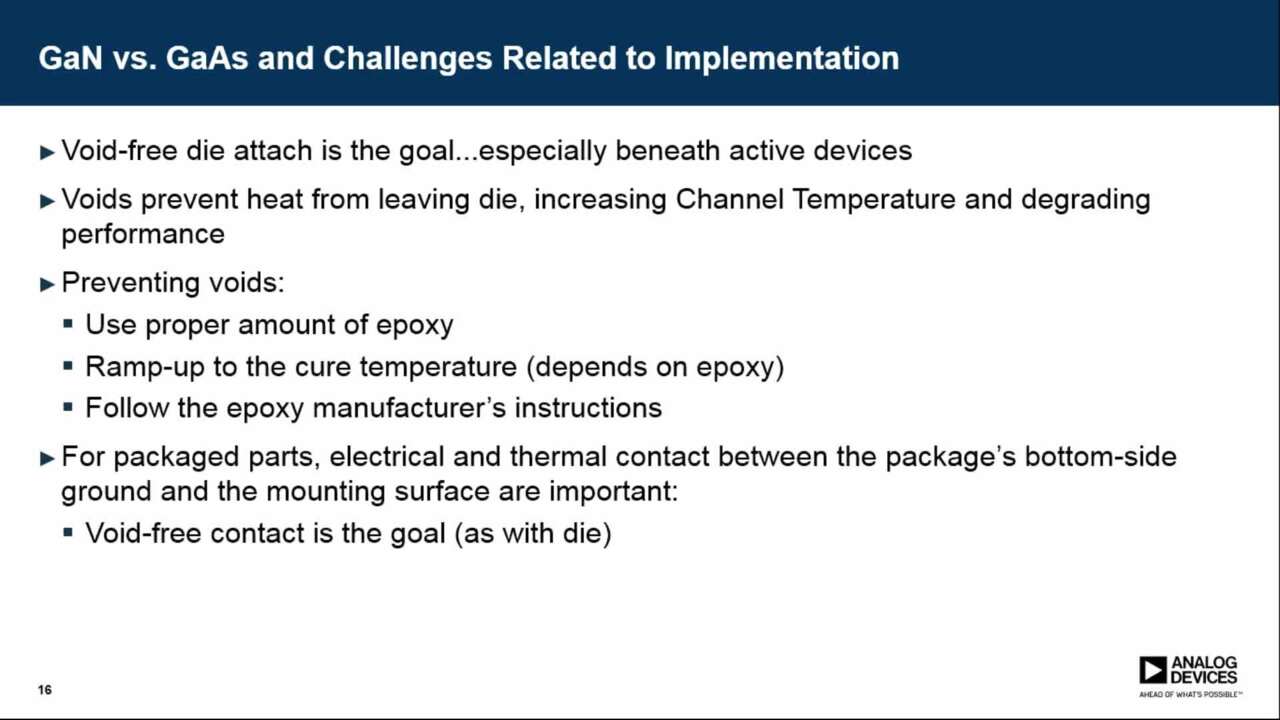

โซลูชันการออกแบบที่ใช้สถาปัตยกรรมวิทยุซุปเปอร์เฮเทอโรไดน์แบบแยกแบบดั้งเดิม ให้ประสิทธิภาพสูง ช่วงไดนามิกที่กว้าง และสัญญาณรบกวนแปลกปลอมน้อยที่สุด สำหรับนักออกแบบ ความท้าทายในการแยกสัญญาณที่ต้องการออกจากความถี่กลาง (IF) ที่เป็นหัวใจของแนวทางนี้ มักส่งผลให้เกิดการออกแบบที่ซับซ้อนโดยมีค่า SWaP สูง และมีการกำหนดค่าใหม่เพียงเล็กน้อยหรือไม่จำเป็นต้องการกำหนดค่าใหม่เลย (รูปที่ 1)

รูปที่ 1: สถาปัตยกรรมวิทยุซูเปอร์เฮเทอโรไดน์แบบดั้งเดิมสามารถบรรลุเป้าหมายด้านประสิทธิภาพได้ แต่ความซับซ้อนของสถาปัตยกรรมดังกล่าวทำให้ไม่สามารถบรรลุเป้าหมายที่เกิดขึ้นใหม่สำหรับ SWaP ที่น้อยที่สุด (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 1: สถาปัตยกรรมวิทยุซูเปอร์เฮเทอโรไดน์แบบดั้งเดิมสามารถบรรลุเป้าหมายด้านประสิทธิภาพได้ แต่ความซับซ้อนของสถาปัตยกรรมดังกล่าวทำให้ไม่สามารถบรรลุเป้าหมายที่เกิดขึ้นใหม่สำหรับ SWaP ที่น้อยที่สุด (แหล่งที่มาภาพ: Analog Devices)

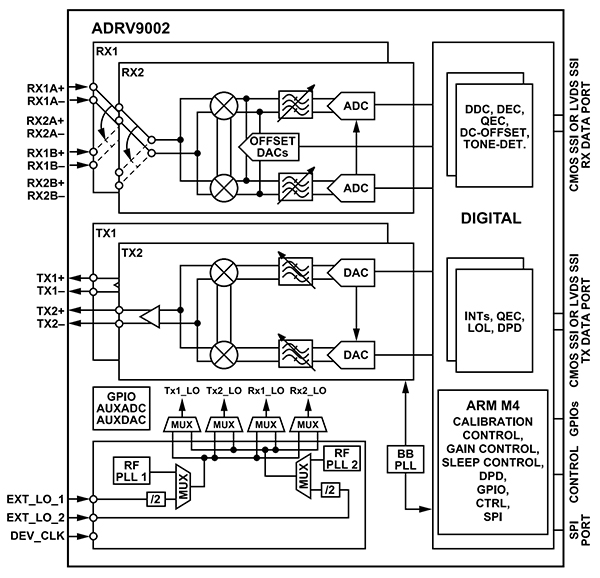

ในทางกลับกัน สถาปัตยกรรมการแปลงโดยตรง (zero-IF) ช่วยลดทั้งข้อกำหนดในการกรองและความต้องการตัวแปลงแอนะล็อกเป็นดิจิทัล (ADC) ที่มีแบนด์วิธสูงมาก ส่งผลให้มีการออกแบบที่เรียบง่ายกว่าซึ่งสามารถนำไปใช้กับชิปตัวเดียวได้ (รูปที่ 2)

รูปที่ 2: สถาปัตยกรรมวิทยุ Zero-IF สามารถตอบสนองความต้องการประสิทธิภาพที่สูงขึ้นและ SWaP ที่ต่ำกว่า แต่การแยกสัญญาณเป็นสิ่งที่ท้าทาย (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 2: สถาปัตยกรรมวิทยุ Zero-IF สามารถตอบสนองความต้องการประสิทธิภาพที่สูงขึ้นและ SWaP ที่ต่ำกว่า แต่การแยกสัญญาณเป็นสิ่งที่ท้าทาย (แหล่งที่มาภาพ: Analog Devices)

แม้จะมีข้อได้เปรียบที่ชัดเจน แต่สถาปัตยกรรมการแปลงโดยตรงก็นำเสนอความท้าทายในการดำเนินงานของตัวเองซึ่งจำกัดการยอมรับอย่างกว้างขวาง ในสถาปัตยกรรมนี้ สัญญาณจะถูกแปลงเป็นตัวพาความถี่วิทยุ (RF) ที่ความถี่ออสซิลเลเตอร์เฉพาะที่ (LO) แต่ข้อผิดพลาดออฟเซ็ตกระแสตรง (DC) และการรั่วไหลของ LO อาจส่งผลให้เกิดข้อผิดพลาดที่แพร่กระจายผ่านสายโซ่สัญญาณ นอกจากนี้ ความแตกต่างในเส้นทางสัญญาณ แม้จะอยู่ภายในชิปตัวเดียวกัน อาจทำให้เกิดเกนหรือเฟสที่ไม่ตรงกันของสัญญาณในเฟส (I) และการสร้างพื้นที่สี่เหลี่ยมจัตุรัส (Q) ส่งผลให้เกิดข้อผิดพลาดการสร้างพื้นที่สี่เหลี่ยมจัตุรัสที่อาจทำให้การแยกสัญญาณลดลง

เทคโนโลยี SDR มีศักยภาพในการพิชิตข้อจำกัดของสถาปัตยกรรมวิทยุแบบดั้งเดิม แต่มีโซลูชันเพียงเล็กน้อยเท่านั้นที่สามารถตอบสนองความต้องการที่กว้างขึ้นที่เกี่ยวข้องกับแอปพลิเคชัน ADEF การใช้ตัวรับส่งสัญญาณ RF รุ่น ADRV9002 ของ Analog Devices ทำให้นักพัฒนาสามารถตอบสนองความต้องการประสิทธิภาพและฟังก์ชันการทำงานที่มากขึ้นได้อย่างง่ายดายด้วย SWaP ที่ต่ำกว่าที่ต้องการในการใช้งานเหล่านี้

ฟังก์ชันการทำงานแบบผสานรวมมอบประสิทธิภาพสูงสุดด้วย SWaP ที่ลดลง

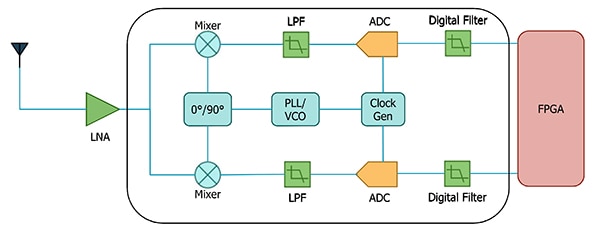

ADRV9002 รองรับช่วงความถี่ตั้งแต่ 30 เมกะเฮิรตซ์ (MHz) ถึง 6,000 MHz เป็นเครื่องรับส่งสัญญาณที่มีการผสานรวมในระดับสูง ซึ่งประกอบด้วยฟังก์ชัน RF สัญญาณผสม และดิจิทัลทั้งหมดที่จำเป็นในการรองรับข้อกำหนดการใช้งานที่หลากหลาย อุปกรณ์นี้สามารถใช้งานทั้งการทำงานของดูเพล็กซ์แบบแบ่งเวลา (TDD) และดูเพล็กซ์แบบแบ่งความถี่ (FDD) อุปกรณ์นี้มีตัวรับการแปลงโดยตรงแบบสองช่องสัญญาณและระบบย่อยตัวส่งสัญญาณแยกกัน ซึ่งรวมถึงตัวกรองดิจิทัลที่ตั้งโปรแกรมได้ การแก้ไขออฟเซ็ต DC และการแก้ไขข้อผิดพลาดการสร้างพื้นที่สี่เหลี่ยมจัตุรัส (QEC)

ภายในระบบย่อยซินธิไซเซอร์บนชิป ADRV9002 มีเส้นทาง Phase-Locked Loop (PLL) ที่แตกต่างกันสองเส้นทาง เส้นทางหนึ่งสำหรับเส้นทาง RF ความถี่สูง และอีกเส้นทางหนึ่งสำหรับนาฬิกาดิจิทัลและนาฬิกาสุ่มตัวอย่างตัวแปลง สุดท้ายนี้ บล็อกการประมวลผลสัญญาณดิจิทัลของอุปกรณ์จะประกอบด้วย Arm® โปรเซสเซอร์ M4 แบบฝังที่จัดการฟังก์ชันการสอบเทียบและควบคุมตัวเอง (รูปที่ 3)

รูปที่ 3: ตัวรับส่งสัญญาณ RF รุ่น ADRV9002 ผสานรวมระบบย่อยการรับ (RX) และส่ง (TX) แบบคู่ (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 3: ตัวรับส่งสัญญาณ RF รุ่น ADRV9002 ผสานรวมระบบย่อยการรับ (RX) และส่ง (TX) แบบคู่ (แหล่งที่มาภาพ: Analog Devices)

สามารถทำงานในโหมด Zero-IF หรือโหมด Low-IF สำหรับการใช้งานที่ไวต่อสัญญาณรบกวนเฟส ADRV9002 มีระบบย่อยเครื่องส่งและตัวรับที่ให้สายโซ่สัญญาณที่สมบูรณ์ ระบบย่อยเครื่องส่งสัญญาณแต่ละระบบจะมีตัวแปลงดิจิทัลเป็นแอนะล็อก (DAC) ตัวกรอง และมิกเซอร์คู่หนึ่งซึ่งจะรวมสัญญาณ I และ Q เข้าด้วยกัน และปรับสัญญาณเหล่านั้นไปยังความถี่พาหะสำหรับการส่งสัญญาณ

ระบบย่อยตัวรับแต่ละระบบจะรวมเครือข่ายอินพุตแบบต้านทานเพื่อการควบคุมเกนที่ป้อนตัวผสมแบบพาสซีฟในโหมดกระแส ในทางกลับกัน เครื่องขยายสัญญาณทรานส์อิมพีแดนซ์จะแปลงเอาต์พุตกระแสไฟฟ้าของมิกเซอร์ให้เป็นระดับแรงดันไฟฟ้าที่แปลงเป็นดิจิทัลด้วย ADC ที่มีช่วงไดนามิกสูง ระหว่างช่องตัวส่งสัญญาณที่มีอยู่ในการทำงาน TDD หรือในการใช้งาน FDD ที่ใช้ระบบตัวรับเพียงระบบเดียว อินพุตตัวรับที่ไม่ได้ใช้สามารถใช้เพื่อตรวจสอบช่องตัวส่งสัญญาณสำหรับการรั่วไหลของ LO และ QEC หรืออินพุตตัวรับที่ไม่ได้ใช้สามารถใช้เพื่อตรวจสอบเอาต์พุตเครื่องขยายสัญญาณเสียง (PA) ระดับสัญญาณ

ความสามารถอย่างหลังมีผลในคุณสมบัติ Digital Pre-Distortion (DPD) แบบบูรณาการของ ADRV9002 ซึ่งใช้ระดับสัญญาณ PA ที่ได้รับการตรวจสอบเพื่อใช้ Pre-Distortion ที่เหมาะสมซึ่งจำเป็นในการปรับเอาต์พุตให้เป็นเส้นตรง ความสามารถนี้ช่วยให้ ADRV9002 ขับเคลื่อน PA ให้เข้าใกล้ความอิ่มตัวมากขึ้น และเพิ่มประสิทธิภาพการทำงานให้สูงสุด

ปรับแต่งพลังและประสิทธิภาพ

อุปกรณ์ ADRV9002 มอบโซลูชันแบบครบวงจรใน Ball Grid Array (BGA) แพ็คเกจชิปมาตราส่วนชิป (CSP)196 ตลอดจนการลดขนาดและน้ำหนักสำหรับระบบสื่อสาร SDR ADEF ให้เหลือน้อยที่สุด เพื่อช่วยให้นักพัฒนาปรับการใช้พลังงานให้เหมาะสมยิ่งขึ้น ADRV9002 ได้รวมคุณสมบัติต่างๆ ที่ออกแบบมาโดยเฉพาะเพื่อช่วยให้นักพัฒนาค้นหาสมดุลที่เหมาะสมระหว่างประสิทธิภาพและพลังงาน

ในระดับบล็อก นักพัฒนาสามารถปรับใช้การปรับขนาดพลังงานบนบล็อกเส้นทางสัญญาณแต่ละรายการเพื่อแลกเปลี่ยนประสิทธิภาพที่ลดลงเพื่อการใช้พลังงานที่น้อยลง นอกจากนี้ บล็อกในเฟรมการรับ TDD (RX) และสามารถปิดใช้งานการส่ง (TX) ได้เพื่อลดเวลาตอบสนองของ RX/TX หรือ TX/RX เพื่อการใช้พลังงานที่น้อยลง ระบบย่อยตัวรับ ADRV9002 แต่ละระบบจึงมี ADC สองคู่ เพื่อช่วยให้นักพัฒนาสามารถเพิ่มประสิทธิภาพพลังงานเทียบกับประสิทธิภาพได้ โดยคู่หนึ่งประกอบด้วย ADC ซิกมาเดลต้าประสิทธิภาพสูง ในขณะที่คู่ที่สองสามารถทดแทนได้เมื่อการใช้พลังงานมีความสำคัญ

สำหรับการใช้งานที่มีการไม่มีการใช้งานเป็นระยะๆ สามารถใช้โหมดจอภาพ RX ของ ADRV9002 ได้ ในโหมดนี้ ADRV9002 จะสลับระหว่างสถานะสลีปพลังงานต่ำและสถานะการตรวจจับที่รอบการทำงานที่ตั้งโปรแกรมไว้ ในสถานะการตรวจจับ อุปกรณ์จะเปิดใช้งานเครื่องรับและพยายามรับสัญญาณผ่านแบนด์วิดท์และความถี่ RX LO ที่นักพัฒนาตั้งโปรแกรมไว้ หากอุปกรณ์วัดระดับกำลังของสัญญาณสูงกว่าเกณฑ์ที่ตั้งโปรแกรมไว้ อุปกรณ์จะออกจากโหมดมอนิเตอร์ และบล็อกของ ADRV9002 จะถูกจ่ายไฟเพื่อจัดการกับสัญญาณที่ต้องการ

การสร้างต้นแบบและการพัฒนาอย่างรวดเร็ว

เพื่อช่วยให้วิศวกรเข้าสู่การประเมิน การสร้างต้นแบบ และการพัฒนาอย่างรวดเร็ว Analog Devices ให้การสนับสนุนฮาร์ดแวร์และซอฟต์แวร์ที่ครอบคลุมของระบบที่ใช้ ADRV9002

สำหรับการรองรับฮาร์ดแวร์ Analog Devices มีการ์ดที่ใช้ ADRV9002 หนึ่งคู่:

- ADRV9002NP/W1/PCBZ สำหรับการใช้งานย่านความถี่ต่ำที่ทำงานในช่วง 30 MHz ถึง 3 กิกะเฮิรตซ์ (GHz)

- ADRV9002NP/W2/PCBZ สำหรับการใช้งานย่านความถี่สูงในช่วง 3 ถึง 6 GHz

การ์ดเหล่านี้มาพร้อมกับตัวเชื่อมต่อ FMC โดยรองรับ ADRV9002 ออนบอร์ดที่มีการควบคุมพลังงานและอินเทอร์เฟซฮาร์ดแวร์ รวมถึงการกระจายสัญญาณนาฬิกาและมัลติชิป (MCS) การ์ดเชื่อมต่อผ่านตัวเชื่อมต่อ FMC กับมาเธอร์บอร์ด FPGA เช่น บอร์ดประเมินผล AMD ZCU102 สำหรับการควบคุมพลังงานและการใช้งาน

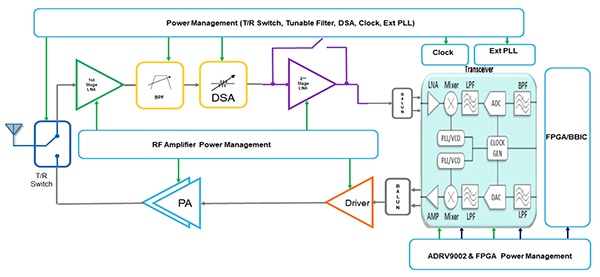

Analog Devices มีแผนผังและรายการวัสดุ (BOM) ที่สมบูรณ์สำหรับการ์ดวิทยุ ADRV9002NP ในแพ็คเกจสนับสนุน แผนผังและ BOM เป็นจุดเริ่มต้นที่มีประสิทธิภาพสำหรับการพัฒนาฮาร์ดแวร์แบบกำหนดเองสำหรับการใช้งานส่วนใหญ่ การใช้งานบางตัวจำเป็นต้องมีฟร้อนต์เอ็น RF เพิ่มเติมเพื่อให้เป็นไปตามข้อกำหนดการปรับสภาพสัญญาณเฉพาะ สำหรับการใช้งานเหล่านี้ นักพัฒนาต้องการส่วนประกอบเพิ่มเติมเพียงไม่กี่ชิ้นเพื่อทำให้การออกแบบเสร็จสมบูรณ์ (รูปที่ 4)

รูปที่ 4: ตัวรับส่งสัญญาณ ADRV9002 ที่มีการบูรณาการสูงช่วยให้นักพัฒนาสามารถนำการออกแบบเฉพาะทางไปใช้ได้อย่างรวดเร็ว (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 4: ตัวรับส่งสัญญาณ ADRV9002 ที่มีการบูรณาการสูงช่วยให้นักพัฒนาสามารถนำการออกแบบเฉพาะทางไปใช้ได้อย่างรวดเร็ว (แหล่งที่มาภาพ: Analog Devices)

ในตัวอย่างนี้ นักพัฒนาสามารถใช้ RF front-end ที่เหมาะสมได้อย่างรวดเร็วโดยใช้ส่วนประกอบการจัดการพลังงานต่อไปนี้จาก Analog Devices:

- ADRF5160 สวิตช์อาร์เอฟ

- HMC8411 เครื่องขยายสัญญาณรบกวนต่ำ (LNA)

- ADMV8526 ตัวกรอง bandpass ที่ปรับได้แบบดิจิทัล

- HMC1119 ตัวลดทอนสัญญาณแบบดิจิตอล RF (DSA)

- HMC8413 แอมพลิฟายเออร์ไดรเวอร์

- HMC8205B PA

Analog Devices ให้การสนับสนุนการพัฒนาซอฟต์แวร์อย่างครอบคลุมผ่านเอกสารประกอบและแพ็คเกจซอฟต์แวร์ที่ดาวน์โหลดได้ นักพัฒนาที่ใช้ฮาร์ดแวร์การพัฒนาที่กล่าวถึงข้างต้นสามารถดำเนินการสร้างต้นแบบและพัฒนาโดยใช้ซอฟต์แวร์กลุ่มผลิตภัณฑ์ของ Analog Devices หรือแพ็คเกจซอฟต์แวร์โอเพ่นซอร์สได้

บทความนี้จำกัดการสนทนาต่อไปนี้กับซอฟต์แวร์สายผลิตภัณฑ์ สำหรับข้อมูลเพิ่มเติมเกี่ยวกับวิธีการพัฒนาโอเพ่นซอร์ส โปรดดูคู่มือผู้ใช้แพลตฟอร์มการสร้างต้นแบบ ADRV9001/2 ของ Analog Devicesโดย Analog Devices ได้กำหนดว่าคำว่า “ADRV9001” ในเอกสารสนับสนุนของบริษัทนั้นหมายถึงชื่อตระกูลที่หมายรวมถึง ADRV9002 และสมาชิกอื่นๆ ของตระกูล ADRV9001 ดังนั้น การอ้างอิงถึง ADRV9001 ในข้อความหรือรูปภาพด้านล่างจึงสามารถนำไปใช้กับอุปกรณ์ ADRV9002 ได้

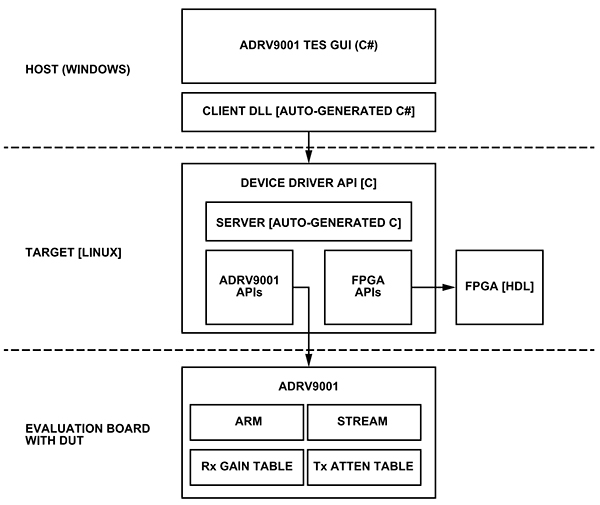

ในชุดพัฒนาซอฟต์แวร์ (SDK) ของกลุ่มผลิตภัณฑ์ของ Analog Devices มีเครื่องมือ Transceiver Evaluation Software (TES) ระบบ Windows ของบริษัทเป็นจุดเริ่มต้นที่สามารถเข้าถึงได้สำหรับการกำหนดค่าและประเมินประสิทธิภาพของตัวรับส่งสัญญาณอย่างรวดเร็ว

ในระหว่างการประเมินและสร้างต้นแบบด้วยการ์ดที่ใช้ ADRV9002 ของ Analog Devices และบอร์ดประเมินผล ZCU102 ของ AMD เครื่องมือ TES มอบอินเทอร์เฟซผู้ใช้แบบกราฟิก (GUI) สำหรับการกำหนดค่าฮาร์ดแวร์และการสังเกตข้อมูลที่บันทึกไว้ (รูปที่ 5)

รูปที่ 5: เครื่องมือ TES ในแพ็คเกจ SDK ช่วยให้นักพัฒนาเริ่มประเมินตัวรับส่งสัญญาณ ADRV9002 บนแพลตฟอร์มการประเมินที่รองรับได้อย่างรวดเร็ว (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 5: เครื่องมือ TES ในแพ็คเกจ SDK ช่วยให้นักพัฒนาเริ่มประเมินตัวรับส่งสัญญาณ ADRV9002 บนแพลตฟอร์มการประเมินที่รองรับได้อย่างรวดเร็ว (แหล่งที่มาภาพ: Analog Devices)

ในทางกลับกัน เครื่องมือ TES จะสร้างโค้ด C# โดยอัตโนมัติซึ่งสามารถคอมไพล์กับสภาพแวดล้อม Linux, สภาพแวดล้อม MATLAB หรือ Python SDK มอบชุดไลบรารีซอฟต์แวร์และ Application Programming Interfaces (API) ที่สมบูรณ์ รวมถึงแพ็คเกจ ADRV9001 API ที่พัฒนาขึ้นสำหรับแพลตฟอร์ม AMD ZCU102

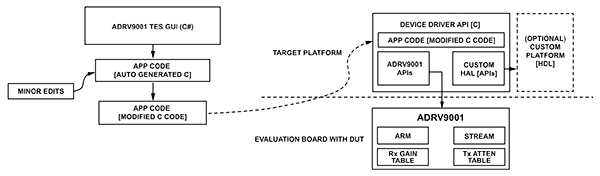

โฟลว์ SDK ยังสนับสนุนการโยกย้ายโดยตรงจากการประเมินและการสร้างต้นแบบด้วยบอร์ดประเมินผลไปยังสภาพแวดล้อมเป้าหมายที่กำหนดเองของนักพัฒนา (รูปที่ 6)

รูปที่ 6: สถาปัตยกรรม SDK ช่วยให้นักพัฒนาขยายผลการประเมินไปยังแพลตฟอร์มเป้าหมายของตนเองได้อย่างง่ายดาย (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 6: สถาปัตยกรรม SDK ช่วยให้นักพัฒนาขยายผลการประเมินไปยังแพลตฟอร์มเป้าหมายของตนเองได้อย่างง่ายดาย (แหล่งที่มาภาพ: Analog Devices)

ในขั้นตอนการโยกย้ายนี้ นักพัฒนาปล่อยให้ TES สร้างโค้ดอัตโนมัติเหมือนเมื่อก่อน อย่างไรก็ตาม แทนที่จะใช้โดยตรง นักพัฒนาจะปรับใช้โค้ดที่สร้างขึ้นในเวอร์ชันแก้ไขแล้วบนแพลตฟอร์มเป้าหมาย ในทางปฏิบัติ การแก้ไขที่จำเป็นส่วนใหญ่จำกัดอยู่ที่การลบการเรียกใช้ฟังก์ชันที่อ้างอิงถึงส่วนประกอบฮาร์ดแวร์ที่เครื่องมือ TES รู้จัก แต่ไม่จำเป็นในระบบเป้าหมาย สถาปัตยกรรม SDK ประกอบด้วยอินเทอร์เฟซ Hardware Abstraction Layer (HAL) ระหว่างไลบรารี ADRV9001 และฮาร์ดแวร์ของนักพัฒนา ดังนั้นนักพัฒนาจึงจำเป็นต้องจัดเตรียมเฉพาะโค้ดแบบกำหนดเองที่ใช้โค้ดอินเทอร์เฟซ HAL สำหรับฮาร์ดแวร์เฉพาะของตนเท่านั้น เป็นผลให้นักพัฒนาสามารถย้ายจากการประเมินผลโดยใช้การ์ด Analog Devices และบอร์ด AMD ไปสู่การพัฒนาสำหรับสภาพแวดล้อมเป้าหมายที่กำหนดเองได้อย่างรวดเร็ว

สรุป

ADEF เผชิญกับความท้าทายที่เพิ่มขึ้นในสภาพแวดล้อมของสัญญาณที่ซับซ้อนมากขึ้น นอกเหนือจากการตอบสนองความต้องการประสิทธิภาพที่สูงขึ้นในช่วงความถี่ที่กว้างขึ้นแล้ว นักพัฒนายังจำเป็นต้องลด SWaP ลงเพื่อรองรับการโยกย้ายการใช้งานเหล่านี้ไปยังระบบที่ใช้พลังงานจากแบตเตอรี่ การใช้ตัวรับส่งสัญญาณที่มีการบูรณาการสูงจาก Analog Devices นักพัฒนาสามารถใช้โซลูชัน SDR เพื่อตอบสนองความต้องการเหล่านี้ได้อย่างมีประสิทธิภาพมากขึ้น

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.