การใช้การแยกเพื่อรักษาความแม่นยำและเพิ่มประสิทธิภาพในการรวบรวมข้อมูล

Contributed By DigiKey's North American Editors

2024-12-20

เนื่องจากข้อมูลอัจฉริยะถูกย้ายไปยังระดับเอดจ์เพื่อแก้ไขปัญหาใหม่ๆ และซับซ้อน การรับประกันความน่าเชื่อถือ ความแม่นยำ และประสิทธิภาพของการรวบรวมข้อมูล (DAQ) จึงกลายเป็นสิ่งสำคัญมากขึ้น ซึ่งจะต้องให้ผู้ออกแบบจัดเตรียมโซ่สัญญาณความแม่นยำแบบแยกจากกันระหว่างสัญญาณที่ได้รับและโปรเซสเซอร์ของระบบ

การรับประกันว่าการแยกกันในห่วงโซ่การวัดสัญญาณแอนะล็อกอย่างแม่นยำเป็นงานที่ท้าทาย ต้องให้ความใส่ใจในรายละเอียดอย่างรอบคอบเพื่อรักษาประสิทธิภาพของโซ่สัญญาณ แม้จะมีปัจจัยที่ทำลายสัญญาณและการเบี่ยงเบนของอุณหภูมิที่หลีกเลี่ยงไม่ได้ สำหรับนักออกแบบหลายๆ คน การเข้าใจปัญหาต่างๆ ที่เกี่ยวข้องให้ดีขึ้นก่อนที่จะเลือกและใช้เทคโนโลยีการแยกที่เหมาะสมอาจเป็นประโยชน์

บทความนี้จะกล่าวถึงปัญหาต่างๆ ที่เกี่ยวข้องกับการพัฒนาและการปรับแต่งระบบ DAQ แบบแยกระดับไฮเอนด์ โดยที่คำว่า "ระดับไฮเอนด์" จะรวมถึงคุณลักษณะต่างๆ เช่น ความแม่นยำ ความถูกต้อง ความสมบูรณ์ของสัญญาณ และความสม่ำเสมอ จากนั้นจะแนะนำโซลูชันห่วงโซ่สัญญาณ DAQ จาก Analog Devices และแสดงให้เห็นว่าสามารถนำมาใช้สร้างระบบดังกล่าวได้อย่างไร

การเพิ่มประสิทธิภาพของแต่ละบล็อคฟังก์ชัน

ระบบ DAQ ทั่วไปประกอบด้วยบล็อกฟังก์ชันชุดหนึ่ง ซึ่งช่วยให้สัญญาณผ่านจากระบบกายภาพผ่านเซ็นเซอร์ จากนั้นข้อมูลจะเดินทางไปที่ฟร้อนเอนด์แบบแอนะล็อก (AFE) เพื่อปรับสภาพสัญญาณ และไปที่ตัวแปลงแอนะล็อกเป็นดิจิทัล (ADC) เพื่อการแปลงเป็นดิจิทัล จากนั้นจึงไปที่อุปกรณ์อ่านข้อมูลหรือตัวควบคุมที่ใช้คอมพิวเตอร์ (ซึ่งอาจมีตั้งแต่ไมโครคอนโทรลเลอร์ไปจนถึงระบบที่ใหญ่กว่ามาก (รูปที่ 1)

รูปที่ 1: ระบบ DAQ ประกอบด้วยโซ่สัญญาณเชิงเส้นที่กำหนดอย่างชัดเจนจากระบบทางกายภาพที่วัดและเซ็นเซอร์ไปยังโปรเซสเซอร์โฮสต์ (แหล่งที่มาภาพ: Bill Schweber)

รูปที่ 1: ระบบ DAQ ประกอบด้วยโซ่สัญญาณเชิงเส้นที่กำหนดอย่างชัดเจนจากระบบทางกายภาพที่วัดและเซ็นเซอร์ไปยังโปรเซสเซอร์โฮสต์ (แหล่งที่มาภาพ: Bill Schweber)

การตระหนักถึงความแม่นยำและความถูกต้องของ DAQ เริ่มต้นจากการเลือกส่วนประกอบปรับสภาพสัญญาณฟร้อนเอนด์ โดยเฉพาะทรานสดิวเซอร์พรีแอมป์ โดยประสิทธิภาพการลดสัญญาณรบกวนนั้นเป็นหนึ่งในปัจจัยสำคัญหลายประการสำหรับฟังก์ชันนี้ เนื่องจากการออกแบบให้ลดสัญญาณรบกวนภายในเป็นเรื่องยาก รวมถึงการขยายไปพร้อมกับสัญญาณที่ต้องการ อัตราส่วนสัญญาณต่อสัญญาณรบกวนพื้นฐาน (SNR) ได้ถูกสร้างขึ้นที่นี่ และหลีกเลี่ยงไม่ได้ที่จะลดลงอีกเมื่อสัญญาณผ่านขั้นตอนเพิ่มเติม

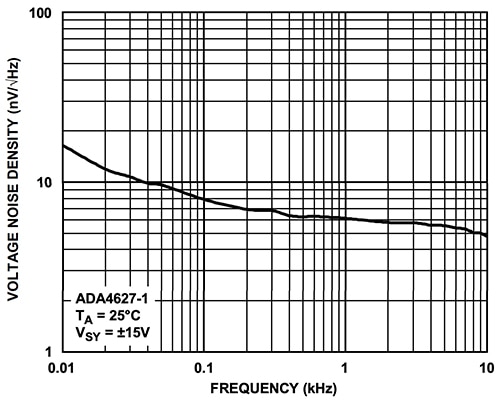

ด้วยเหตุนี้ AFE จึงมักใช้วงจรขยายเชิงดำเนินการ (ออปแอมป์) ฟังก์ชันเดียวมีการปรับสัญญาณรบกวน ตัวเลือกที่ดีสำหรับพรีแอมป์แบบฟรอนท์เอนด์คือ Analog Devices ADA4627-1BRZ-R7, ออปแอมป์ JFET 30 V (±15 V แหล่งจ่ายไฟคู่) ความเร็วสูง สัญญาณรบกวนต่ำ กระแสไบอัสต่ำ ในบรรดาคุณสมบัติที่ปรับให้เหมาะกับเซ็นเซอร์มากมายนั้น มีลักษณะเด่นคือแรงดันออฟเซ็ตต่ำที่ 200 µV (สูงสุด) ดริฟต์ออฟเซ็ตที่ 1 μV/°C (ทั่วไป) และกระแสไบอัสอินพุตที่ 5 พิโกแอมป์ (pA) (สูงสุด) ข้อกำหนดแรงดันไฟฟ้าวิกฤตสำหรับสัญญาณรบกวนคือ 6.1 nV ต่อรากที่สองของเฮิรตซ์ (nV/√Hz) ที่ 1 กิโลเฮิรตซ์ (kHz) (รูปที่ 2)

รูปที่ 2: ออปแอมป์ JFET รุ่น ADA4627 มีสัญญาณรบกวนแรงดันไฟฟ้า 6.1 nV/√Hz (1 kHz) (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 2: ออปแอมป์ JFET รุ่น ADA4627 มีสัญญาณรบกวนแรงดันไฟฟ้า 6.1 nV/√Hz (1 kHz) (แหล่งที่มาภาพ: Analog Devices)

การแยกตัวทำให้เกิดประโยชน์มากมาย

เมื่อสัญญาณได้รับการขยายและแปลงเป็นดิจิทัลแล้ว ขั้นตอนถัดไปคือการสร้างการแยกไฟฟ้าระหว่างสัญญาณและส่วนดิจิทัลของระบบและโปรเซสเซอร์ที่เกี่ยวข้อง มีสาเหตุหลักสามประการสำหรับขั้นตอนนี้:

- การลดสัญญาณรบกวนและการรบกวน: การแยกทางไฟฟ้าแบบกัลวานิกสามารถกำจัดความแปรผันของแรงดันไฟฟ้าโหมดทั่วไป ลูปกราวด์ และสัญญาณรบกวนทางแม่เหล็กไฟฟ้า (EMI) และยังป้องกันแหล่งกำเนิดสัญญาณรบกวนจากภายนอกไม่ให้มาทำลายสัญญาณที่รับได้ ทำให้การวัดค่าชัดเจนและแม่นยำยิ่งขึ้น

- การกำจัดกราวด์ลูป: กราวด์ลูปอาจก่อให้เกิดความต่างศักย์ไฟฟ้าที่ทำให้สัญญาณที่วัดผิดเพี้ยนได้ การแยกจะทำลายเส้นทางกราวด์ลูป จึงกำจัดการรบกวนที่เกิดจากการเปลี่ยนแปลงของศักย์ไฟฟ้ากราวด์ และปรับปรุงความแม่นยำในการวัด

- ความปลอดภัยและการป้องกัน: ตัวกั้นไฟฟ้าช่วยให้ปลอดภัยจากไฟฟ้ากระชากที่เป็นอันตราย หรือไฟกระชากจากการเข้าถึงส่วนประกอบการวัดที่ละเอียดอ่อน ซึ่งจะช่วยปกป้องวงจรการวัดและอุปกรณ์ที่เชื่อมต่อ ช่วยให้มั่นใจได้ว่าจะทำงานได้ปลอดภัยและเชื่อถือได้ นอกจากนี้ ตัวกั้นดังกล่าวจะช่วยขจัดอันตรายทางไฟฟ้าต่อผู้ใช้หากเซ็นเซอร์ระดับแรงดันต่ำสัมผัสสายไฟแรงสูงหรือไฟฟ้ากระแสสลับแม้เพียงสั้นๆ

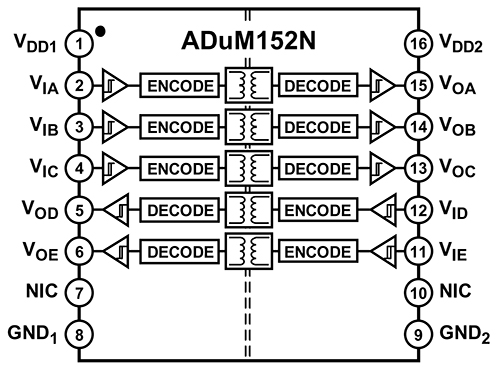

มีเทคนิคต่างๆ มากมายสำหรับการแยกสัญญาณดิจิทัลโดยอาศัยหลักการทางแม่เหล็ก ออปติคอล ความจุ และแม้แต่ RF ซึ่ง Analog Devices ได้นำเสนอโซลูชันประสิทธิภาพสูงหลากหลายประเภท รวมถึง ADUM152N1BRZ-RL7 ไอโซเลเตอร์สัญญาณดิจิตอลห้าช่องสัญญาณโดยใช้เทคโนโลยี iCoupler ที่เป็นกรรมสิทธิ์ (รูปที่ 3)

รูปที่ 3: ไอโซเลเตอร์ดิจิทัลห้าช่อง ADuM152N ใช้การเชื่อมต่อแม่เหล็กที่เป็นกรรมสิทธิ์เพื่อให้ได้ประสิทธิภาพสูง (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 3: ไอโซเลเตอร์ดิจิทัลห้าช่อง ADuM152N ใช้การเชื่อมต่อแม่เหล็กที่เป็นกรรมสิทธิ์เพื่อให้ได้ประสิทธิภาพสูง (แหล่งที่มาภาพ: Analog Devices)

ไอโซเลเตอร์เหล่านี้รวมวงจร CMOS ความเร็วสูงและเทคโนโลยีหม้อแปลงแกนอากาศโมโนลิธิก เพื่อให้แน่ใจว่าประสิทธิภาพสอดคล้องกับความต้องการของลิงก์ดิจิทัลความเร็วสูง ความล่าช้าในการแพร่กระจายสูงสุดคือ 13 นาโนวินาที (ns) โดยมีความบิดเบือนความกว้างพัลส์น้อยกว่า 4.5 ns ที่ 5 V และการจับคู่ช่องสัญญาณต่อช่องของความล่าช้าในการแพร่กระจายนั้นมีค่า 4.0 ns (สูงสุด) เวอร์ชันสองช่องสัญญาณที่คล้ายกัน ADUM120N1BRZ-RL7 สามารถใช้งานได้เพื่อให้จำนวนช่องสัญญาณแยกทั้งหมดตรงกับความกว้างของบัสได้

ไอโซเลเตอร์สัญญาณเหล่านี้ได้รับการปรับให้เหมาะสมสำหรับประสิทธิภาพความเร็วสูงด้วยอัตราข้อมูลที่รับประกันที่ 150 เมกะบิตต่อวินาที (Mbits/s) อุปกรณ์เหล่านี้ให้ภูมิคุ้มกันชั่วคราวโหมดทั่วไป (CMTI) สูงถึง 100 กิโลโวลต์ต่อไมโครวินาที (kV/μs) ทนแรงดันไฟฟ้าได้ 3 กิโลโวลต์รากที่สองเฉลี่ย (rms) และปฏิบัติตามข้อกำหนดทางกฎหมายที่เกี่ยวข้องทั้งหมด

การแยกสัญญาณเป็นเพียงส่วนหนึ่งของเรื่องราวการแยกโดยรวม โดยรางไฟ DC ทั้งหมดที่ไปยังระบบ DAQ จะต้องถูกแยกออกด้วย ส่วนใหญ่แล้ววิธีนี้จะทำได้โดยใช้หม้อแปลงเป็นส่วนประกอบแยก

หากแหล่งจ่ายไฟด้านปฐมภูมิเป็นไฟฟ้ากระแสสลับอยู่แล้ว ไฟฟ้าจะถูกส่งผ่านหม้อแปลง จากนั้นจึงทำการแก้ไขและควบคุม หากแหล่งจ่ายไฟเป็นไฟฟ้ากระแสตรง จะต้องตัดไฟฟ้าให้เป็นรูปคลื่นคล้ายไฟฟ้ากระแสสลับเสียก่อน ซึ่งจะง่ายขึ้นมากด้วยการใช้ส่วนประกอบเช่น LT3999 ไดรเวอร์ DC/DC ที่มีสัญญาณรบกวนต่ำ 1 แอมแปร์ (A) 50 kHz ถึง 1 เมกะเฮิรตซ์ (MHz)

ระบบ DAQ ประสิทธิภาพสูงแบบสมบูรณ์ต้องมีส่วนประกอบหลักและอุปกรณ์ต่อพ่วงเพิ่มเติม การออกแบบและการจัดวางจะต้องทำให้การวัดและความสมบูรณ์ของข้อมูลแม่นยำ นอกเหนือจากวงจรขยายสัญญาณและตัวกั้นการแยกสัญญาณแล้ว ห่วงโซ่สัญญาณความแม่นยำยังประกอบด้วยองค์ประกอบการกรอง ADC ความละเอียดสูง และสวิตช์อีกด้วย ส่วนประกอบเหล่านี้รวมกันเพื่อกำจัดสัญญาณรบกวน ลดการรบกวนให้เหลือน้อยที่สุด และให้การแสดงสัญญาณที่แม่นยำ

รวมทั้งหมดเข้าด้วยกัน

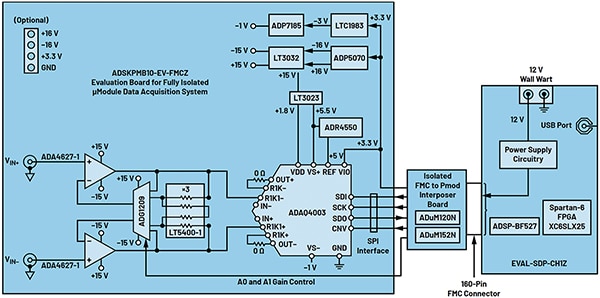

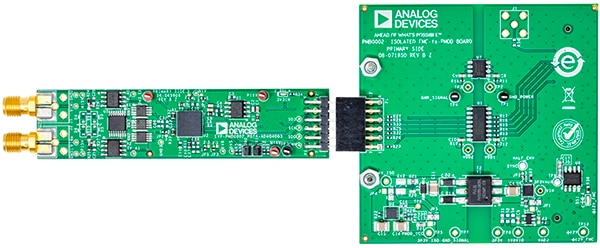

ตัวอย่างของโซ่สัญญาณแบบแยกที่ใช้ส่วนประกอบสำคัญเหล่านี้คือ ADSKPMB10-EV-FMCZ แพลตฟอร์มแม่นยำที่ใช้ระบบ DAQ แบบช่องสัญญาณเดียว แยกอย่างสมบูรณ์ และมีความหน่วงเวลาต่ำ (รูปที่ 4) โซลูชันนี้รวมเอาวงจรขยายสัญญาณเครื่องมือวัดค่าเกนที่ตั้งโปรแกรมได้ (PGIA) สำหรับการปรับสภาพสัญญาณเพื่อรองรับความไวของอินเทอร์เฟซเซ็นเซอร์ต่างๆ ด้วยการแยกสัญญาณดิจิทัลและพลังงานภายในบอร์ดขนาดกะทัดรัด

รูปที่ 4: ADKSPMB10-EV-FMCZ เป็นแพลตฟอร์มแม่นยำที่ใช้งานระบบ DAQ แบบช่องสัญญาณเดียว แยกอย่างสมบูรณ์ และมีความหน่วงเวลาต่ำ บอร์ดอินเทอร์โพเซอร์ PMOD ถึง FMC (บล็อกกลาง) ทำหน้าที่แยกสัญญาณและทำหน้าที่อื่นๆ (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 4: ADKSPMB10-EV-FMCZ เป็นแพลตฟอร์มแม่นยำที่ใช้งานระบบ DAQ แบบช่องสัญญาณเดียว แยกอย่างสมบูรณ์ และมีความหน่วงเวลาต่ำ บอร์ดอินเทอร์โพเซอร์ PMOD ถึง FMC (บล็อกกลาง) ทำหน้าที่แยกสัญญาณและทำหน้าที่อื่นๆ (แหล่งที่มาภาพ: Analog Devices)

สำหรับการประเมิน จะได้รับการกำหนดค่าเป็นโซลูชันหลายบอร์ดที่ประกอบด้วย ADSKPMB10-EV-FMCZ บนฟอร์มแฟกเตอร์ PMOD (รูปที่ 5) ร่วมกับบอร์ดอินเทอร์เฟซแพลตฟอร์มสาธิตระบบ (SDP) EVAL-SDP-CH1Z ระหว่างบอร์ดทั้งสองนี้คือบอร์ดอินเทอร์โพเซอร์ PMOD-to-FMC ที่แยกกันอย่างสมบูรณ์

รูปที่ 5: ADSKPMB10-EV-FMCZ (ซ้าย) เชื่อมต่อกับบอร์ดอินเทอร์เฟซ SDP (ไม่แสดง) ผ่านบอร์ดอินเทอร์โพเซอร์ PMOD-to-FMC (ขวา) โดยโซนแยกแนวตั้งบนแผงอินเทอร์โพเซอร์แสดงตำแหน่งที่ติดตั้งแผงกั้นแยก (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 5: ADSKPMB10-EV-FMCZ (ซ้าย) เชื่อมต่อกับบอร์ดอินเทอร์เฟซ SDP (ไม่แสดง) ผ่านบอร์ดอินเทอร์โพเซอร์ PMOD-to-FMC (ขวา) โดยโซนแยกแนวตั้งบนแผงอินเทอร์โพเซอร์แสดงตำแหน่งที่ติดตั้งแผงกั้นแยก (แหล่งที่มาภาพ: Analog Devices)

ADSKPMB10-EV-FMCZ มี PGIA แบบแยกที่สร้างขึ้นโดยใช้ออปแอมป์ ADA4627-1 โดย PGIA มีความต้านทานอินพุตสูง ซึ่งจำเป็นสำหรับการรองรับการเชื่อมต่อโดยตรงกับเซ็นเซอร์ต่างๆ โมดูลนี้ยังมีเครือข่ายตัวต้านทานแบบจับคู่สี่ตัวที่มีความแม่นยำสำหรับการตั้งค่าเกน มัลติเพล็กเซอร์สี่ช่อง และไดรเวอร์ ADC ของแอมพลิฟายเออร์แบบดิฟเฟอเรนเชียลอย่างสมบูรณ์สำหรับ ADAQ4003 ซึ่ง ADAQ4003 เป็นระบบย่อย ADC และ DAQ 18 บิต 2 เมกะแซมเปิลต่อวินาที (MSPS) ที่ใช้งานเป็น μModule

โมดูลนี้เป็นมากกว่าแค่ ADC ความละเอียดสูง ADAQ4003 มีเทคนิคการลดสัญญาณรบกวนหลายวิธีเพื่อให้สามารถจับสัญญาณที่มีความเที่ยงตรงสูงได้ ตัวอย่างเช่น ฟิลเตอร์ตัวต้านทาน-ตัวเก็บประจุ (RC) ขั้วเดี่ยวแบบโลว์พาสจะถูกวางไว้ระหว่างเอาต์พุตของไดรเวอร์ ADC และอินพุต ADC ภายใน μModule เพื่อกำจัดสัญญาณรบกวนความถี่สูงและลด "การตีกลับ" ของประจุจากอินพุตของ ADC ภายใน

นอกจากนี้ การจัดวางของ μModule ช่วยให้แน่ใจว่าเส้นทางแอนะล็อกและดิจิตอลถูกแยกจากกันเพื่อหลีกเลี่ยงการครอสโอเวอร์และลดสัญญาณรบกวนที่แผ่ออกมาให้เหลือน้อยที่สุด

บอร์ดอินเทอร์โพเซอร์ PMOD-to-FMC แบบแยกอย่างสมบูรณ์ประกอบด้วยไดรเวอร์ LT3999 DC/DC, ไอโซเลเตอร์ดิจิทัลห้าและสองช่อง, ตัวควบคุมแรงดันไฟฟ้าแบบลดความถี่ต่ำ (LDO) ที่มีสัญญาณรบกวนต่ำ และ LDO ที่มีสัญญาณรบกวนต่ำเป็นพิเศษ บอร์ดอินเทอร์โพเซอร์ทำหน้าที่เป็นสะพานเชื่อมและเชื่อมต่อกับบอร์ดอินเทอร์เฟซ SDP

บอร์ดอินเทอร์เฟซ SDP ดำเนินการประมวลผล การจัดการ และการเชื่อมต่อหลังการรวม โดยบอร์ดนี้มีขั้วต่อ FMC 160 พิน แหล่งจ่ายไฟ 12 VDC ซึ่งได้รับการควบคุมและแบ่งพาร์ติชั่นเพิ่มเติมสำหรับบอร์ดอื่นๆ โปรเซสเซอร์ Blackfin ที่มีการรักษาความปลอดภัยด้วยฮาร์ดแวร์สำหรับการป้องกันรหัสและเนื้อหา พอร์ต USB และ FPGA Spartan-6

ประสิทธิภาพการทำงานเป็นตัวตัดสิน

การประเมินประสิทธิภาพการทำงานของระบบ DAQ ที่แม่นยำไม่ใช่กระบวนการที่ง่ายมากนัก เนื่องจากเครื่องมือ การจัดเตรียมการทดสอบ และถือเป็นสิ่งสำคัญ แม้ว่าพารามิเตอร์ไดนามิกหลายตัวจะมีความสัมพันธ์กับประสิทธิภาพของระบบ DAQ แต่พารามิเตอร์ที่เปิดเผยมากที่สุดคือช่วงไดนามิก อัตราส่วนสัญญาณต่อสัญญาณรบกวน (SNR) และความเพี้ยนฮาร์มอนิกรวม (THD)

ช่วงไดนามิกคือช่วงระหว่างระดับสัญญาณรบกวนพื้นฐานของอุปกรณ์และระดับเอาต์พุตสูงสุดที่ระบุ

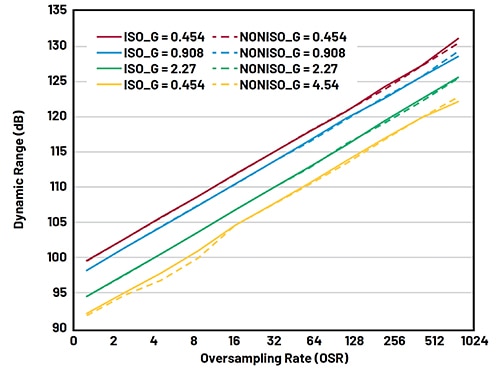

การออกแบบนี้มีช่วงไดนามิกที่เป็นมาตรฐานที่ 93 เดซิเบล (dB) ที่การตั้งค่าเกนสูงสุดและ 100 dB ที่การตั้งค่าเกนต่ำสุด ถือว่าน่าประทับใจ (รูปที่ 6) การเพิ่มอัตราส่วนการสุ่มตัวอย่างเกินเป็นแฟคเตอร์ 1,024× จะช่วยปรับปรุงการวัดได้ดีขึ้น โดยจะไปถึงจุดสูงสุดที่ 123 dB และ 130 dB ตามลำดับ

รูปที่ 6: ช่วงไดนามิกประมาณ 100 dB ของวงจรทั้งหมดและห่วงโซ่สัญญาณ ขึ้นอยู่กับค่าเกนและการตั้งค่าอื่นๆ แสดงให้เห็นถึงระบบ DAQ ประสิทธิภาพสูง (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 6: ช่วงไดนามิกประมาณ 100 dB ของวงจรทั้งหมดและห่วงโซ่สัญญาณ ขึ้นอยู่กับค่าเกนและการตั้งค่าอื่นๆ แสดงให้เห็นถึงระบบ DAQ ประสิทธิภาพสูง (แหล่งที่มาภาพ: Analog Devices)

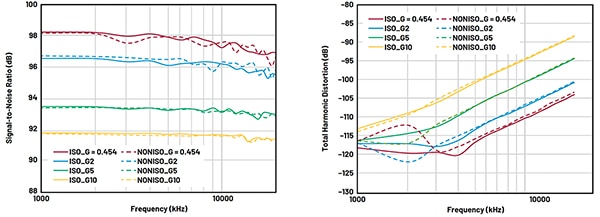

SNR คืออัตราส่วนของแอมพลิจูดสัญญาณ rms ต่อค่าเฉลี่ยของค่ารากที่สองของผลรวมกำลังสอง (RSS) ของส่วนประกอบสเปกตรัมอื่นทั้งหมด โดยไม่รวมฮาร์โมนิกและ DC THD คืออัตราส่วนของค่า rms ของสัญญาณพื้นฐานต่อค่าเฉลี่ยของ RSS ของฮาร์โมนิก

ค่า SNR และ THD ของการออกแบบนี้เห็นได้ชัดว่ามีประสิทธิภาพสูง เนื่องจากห่วงโซ่สัญญาณสามารถบรรลุค่า SNR สูงสุดที่ 98 dB (รูปที่ 7 (ซ้าย)) และ THD ที่ -118 dB (รูปที่ 7 (ขวา)) ทั้งนี้ขึ้นอยู่กับการตั้งค่าเกน

รูปที่ 7: ควบคู่ไปกับช่วงไดนามิก SNR ที่สูง (ซ้าย) และ THD ที่ต่ำ (ขวา) ให้หลักฐานที่จับต้องได้ของประสิทธิภาพ DAQ ที่เน้นแอนะล็อกที่เหนือกว่า (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 7: ควบคู่ไปกับช่วงไดนามิก SNR ที่สูง (ซ้าย) และ THD ที่ต่ำ (ขวา) ให้หลักฐานที่จับต้องได้ของประสิทธิภาพ DAQ ที่เน้นแอนะล็อกที่เหนือกว่า (แหล่งที่มาภาพ: Analog Devices)

สรุป

การออกแบบและการใช้งานห่วงโซ่สัญญาณความแม่นยำแบบแยกที่รักษาความแม่นยำ ลดสัญญาณรบกวนและการรบกวนให้เหลือน้อยที่สุด และรับรองความสมบูรณ์ของข้อมูล ถือเป็นภารกิจการออกแบบและการใช้งานที่สำคัญ ซึ่งสามารถทำได้โดยใช้การขยายสัญญาณที่แม่นยำ เทคนิคการแยกสัญญาณ ADC และโมดูลที่มีความละเอียดสูง และการจัดการพลังงานที่มีสัญญาณรบกวนต่ำ เพื่อให้สามารถวัดค่าได้อย่างแม่นยำ แม้ในสภาพแวดล้อมที่มีความท้าทายทางไฟฟ้า ทำได้ด้วยการใช้ส่วนประกอบขั้นสูงจาก Analog Devices ตั้งแต่ออปแอมป์พื้นฐานจนถึงอุปกรณ์แยกขั้นสูง และรองรับด้วยฟังก์ชันต่อพ่วงที่จำเป็น ควบคู่ไปกับเอกสารข้อมูลโดยละเอียดและแนวทางการใช้งาน

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.