ใช้ FPGA Fast Path เพื่อสร้างแอปพลิเคชั่น Edge AI ที่มีประสิทธิภาพสูง

Contributed By DigiKey's North American Editors

2021-01-12

นักออกแบบที่ต้องการใช้อัลกอริธึมปัญญาประดิษฐ์ (AI) บนโปรเซสเซอร์เชิงอนุมานที่ Edge อยู่ภายใต้แรงกดดันอย่างต่อเนื่องเพื่อลดการใช้พลังงานและเวลาในการพัฒนาแม้ว่าความต้องการในการประมวลผลจะเพิ่มขึ้นก็ตาม อาร์เรย์เกทที่ตั้งโปรแกรมได้ภาคสนาม (FPGA) นำเสนอการผสมผสานที่มีประสิทธิภาพโดยเฉพาะอย่างยิ่งระหว่างความเร็วและประสิทธิภาพการใช้พลังงานสำหรับการใช้เอ็นจิ้นการอนุมานของเครือข่ายประสาทเทียม (NN) ที่จำเป็นสำหรับ Edge AI อย่างไรก็ตามสำหรับนักพัฒนาที่ไม่คุ้นเคยกับ FPGA วิธีการพัฒนา FPGA แบบเดิมอาจดูซับซ้อนซึ่งมักทำให้นักพัฒนาหันไปใช้โซลูชันที่เหมาะสมน้อยกว่า

บทความนี้อธิบายวิธีการที่ง่ายกว่าจาก Microchip Technology ที่ช่วยให้นักพัฒนาข้ามการพัฒนา FPGA แบบเดิมเพื่อสร้าง NN ที่ผ่านการฝึกอบรมโดยใช้ FPGA และชุดพัฒนาซอฟต์แวร์ (SDK) หรือใช้ชุดวิดีโอที่ใช้ FPGA เพื่อย้ายไปสู่การพัฒนาแอปพลิเคชันการมองเห็นแบบฝังอัจฉริยะในทันที

ทำไมต้องใช้ AI?

การประมวลผลแบบ Edge มอบประโยชน์มากมายให้กับแอปพลิเคชัน Internet of Things (IoT) ในกลุ่มต่างๆเช่นระบบอัตโนมัติในอุตสาหกรรมระบบรักษาความปลอดภัยบ้านอัจฉริยะและอื่น ๆ ในแอปพลิเคชัน IoT สำหรับอุตสาหกรรม (IIoT) ที่กำหนดเป้าหมายไปที่พื้นโรงงานการประมวลผลแบบขอบสามารถปรับปรุงเวลาตอบสนองในลูปการควบคุมกระบวนการได้อย่างมาก โดยขจัดความล่าช้าในการเดินทางไปกลับของแอปพลิเคชันบนคลาวด์ ในทำนองเดียวกันระบบรักษาความปลอดภัยแบบ edge หรือระบบล็อคประตูบ้านอัจฉริยะสามารถทำงานต่อไปได้แม้ว่าการเชื่อมต่อกับระบบคลาวด์จะขาดหายไปโดยไม่ตั้งใจหรือตั้งใจก็ตาม ในหลาย ๆ กรณีการใช้ edge computing ในแอปพลิเคชันเหล่านี้สามารถช่วยลดต้นทุนการดำเนินงานโดยรวมได้โดยการลดการพึ่งพาทรัพยากรบนคลาวด์ของผลิตภัณฑ์ แทนที่จะต้องเผชิญกับความต้องการทรัพยากรระบบคลาวด์ที่มีราคาแพงโดยไม่คาดคิดเนื่องจากความต้องการผลิตภัณฑ์ของตนเพิ่มขึ้นนักพัฒนาสามารถพึ่งพาความสามารถในการประมวลผลในพื้นที่ที่มีอยู่ในผลิตภัณฑ์ของตนเพื่อช่วยรักษาค่าใช้จ่ายในการดำเนินงานให้คงที่

การยอมรับอย่างรวดเร็วและความต้องการที่เพิ่มขึ้นสำหรับรูปแบบการอนุมานของ machine learning (ML) ช่วยเพิ่มความสำคัญของการประมวลผลแบบขอบ สำหรับนักพัฒนาการประมวลผลแบบจำลองการอนุมานในพื้นที่ช่วยลดเวลาในการตอบสนองและต้นทุนของทรัพยากรระบบคลาวด์ที่จำเป็นสำหรับการอนุมานบนคลาวด์ สำหรับผู้ใช้การใช้แบบจำลองการอนุมานเฉพาะที่ช่วยเพิ่มความมั่นใจว่าผลิตภัณฑ์ของตนจะยังคงทำงานต่อไปแม้จะสูญเสียการเชื่อมต่ออินเทอร์เน็ตเป็นครั้งคราวหรือการเปลี่ยนแปลงข้อเสนอบนคลาวด์ของผู้จำหน่ายผลิตภัณฑ์ นอกจากนี้ความกังวลเกี่ยวกับความปลอดภัยและความเป็นส่วนตัวยังสามารถผลักดันความจำเป็นในการประมวลผลในพื้นที่และการอนุมานเพื่อ จำกัด จำนวนข้อมูลที่ละเอียดอ่อนที่ถูกถ่ายโอนไปยังระบบคลาวด์ผ่านอินเทอร์เน็ตสาธารณะ

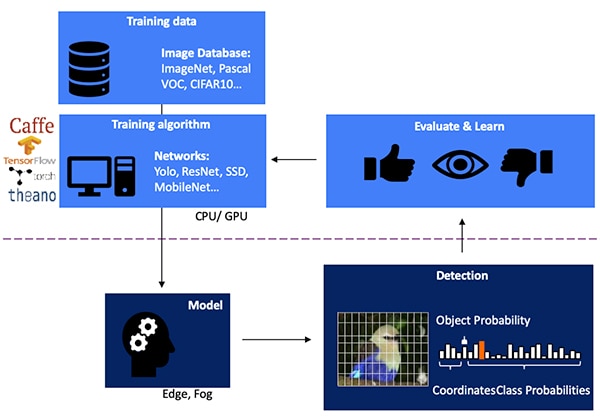

การพัฒนาแบบจำลองการอนุมาน NN สำหรับการตรวจจับวัตถุด้วยการมองเห็นเป็นกระบวนการหลายขั้นตอนโดยเริ่มจากการฝึกโมเดลซึ่งโดยทั่วไปจะดำเนินการบนเฟรมเวิร์ก ML เช่น TensorFlow โดยใช้รูปภาพที่มีป้ายกำกับสาธารณะหรือรูปภาพที่มีป้ายกำกับแบบกำหนดเอง เนื่องจากความต้องการในการประมวลผลโดยทั่วไปการฝึกโมเดลจึงดำเนินการกับหน่วยประมวลผลกราฟิก (GPU) ในระบบคลาวด์หรือแพลตฟอร์มคอมพิวเตอร์ประสิทธิภาพสูงอื่น ๆ หลังจากการฝึกอบรมเสร็จสิ้นโมเดลจะถูกแปลงเป็นแบบจำลองการอนุมานที่สามารถรันบนทรัพยากรการประมวลผลแบบ edge หรือแบบหมอกและส่งผลการอนุมานเป็นชุดของความน่าจะเป็นของคลาสอ็อบเจ็กต์ (รูปที่ 1)

รูปที่ 1: การใช้แบบจำลองการอนุมานสำหรับ edge AI อยู่ที่ส่วนท้ายของกระบวนการหลายขั้นตอนที่ต้องการการฝึกอบรมและการเพิ่มประสิทธิภาพของ NN บนเฟรมเวิร์กโดยใช้ข้อมูลการฝึกอบรมที่มีอยู่หรือกำหนดเอง (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 1: การใช้แบบจำลองการอนุมานสำหรับ edge AI อยู่ที่ส่วนท้ายของกระบวนการหลายขั้นตอนที่ต้องการการฝึกอบรมและการเพิ่มประสิทธิภาพของ NN บนเฟรมเวิร์กโดยใช้ข้อมูลการฝึกอบรมที่มีอยู่หรือกำหนดเอง (แหล่งที่มาภาพ: Microchip Technology)

เหตุใดแบบจำลองการอนุมานจึงมีความท้าทายต่อการคำนวณ

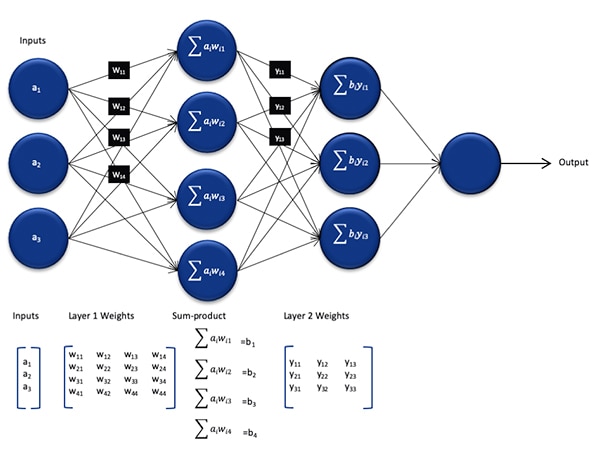

แม้ว่าจะมีขนาดและความซับซ้อนลดลงเมื่อเทียบกับแบบจำลองที่ใช้ในระหว่างกระบวนการฝึกอบรม แต่แบบจำลองการอนุมานแบบ NN ยังคงเป็นความท้าทายในการคำนวณสำหรับโปรเซสเซอร์ที่ใช้งานทั่วไปเนื่องจากต้องมีการคำนวณจำนวนมาก ในรูปแบบทั่วไปแบบจำลอง NN แบบลึกประกอบด้วยชุดเซลล์ประสาทหลายชั้น ภายในแต่ละชั้นในเครือข่ายที่เชื่อมต่อกันอย่างสมบูรณ์แต่ละเซลล์ประสาท nij จำเป็นต้องคำนวณผลรวมของผลิตภัณฑ์ของแต่ละอินพุตด้วยน้ำหนักที่สัมพันธ์กัน wij (รูปที่ 2)

รูปที่ 2: จำนวนการคำนวณที่จำเป็นสำหรับการอนุมานด้วย NN สามารถกำหนดภาระงานการคำนวณที่สำคัญได้ (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 2: จำนวนการคำนวณที่จำเป็นสำหรับการอนุมานด้วย NN สามารถกำหนดภาระงานการคำนวณที่สำคัญได้ (แหล่งที่มาภาพ: Microchip Technology)

ไม่แสดงในรูปที่ 2 คือข้อกำหนดการคำนวณเพิ่มเติมที่กำหนดโดยฟังก์ชันการกระตุ้นที่ปรับเปลี่ยนเอาต์พุตของเซลล์ประสาทแต่ละเซลล์โดยการแมปค่าลบเป็นศูนย์ค่าการแมปที่มากกว่า 1 ถึง 1 และฟังก์ชันที่คล้ายกัน ผลลัพธ์ของฟังก์ชันกระตุ้นสำหรับแต่ละเซลล์ประสาท nij ทำหน้าที่เป็นอินพุตไปยังเลเยอร์ถัดไป i + 1 โดยดำเนินการต่อในลักษณะนี้สำหรับแต่ละเลเยอร์ สุดท้ายชั้นเอาต์พุตของแบบจำลอง NN จะสร้างเวกเตอร์เอาต์พุตที่แสดงถึงความน่าจะเป็นที่เวกเตอร์อินพุตดั้งเดิม (หรือเมทริกซ์) สอดคล้องกับหนึ่งในคลาส (หรือป้ายกำกับ) ที่ใช้ในระหว่างกระบวนการเรียนรู้ภายใต้การดูแล

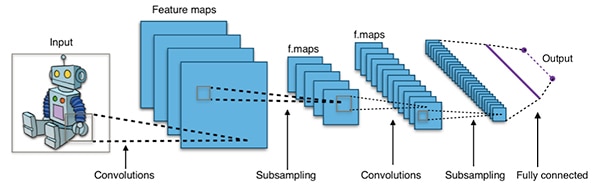

แบบจำลอง NN ที่มีประสิทธิภาพถูกสร้างขึ้นด้วยสถาปัตยกรรมที่ใหญ่กว่าและซับซ้อนกว่าสถาปัตยกรรม NN ทั่วไปที่เป็นตัวแทนที่แสดงไว้ด้านบน ตัวอย่างเช่น คอนโวลูชั่นแนลเอ็นเอ็น (CNN) ทั่วไปที่ใช้สำหรับการตรวจจับวัตถุรูปภาพจะใช้หลักการเหล่านี้ในลักษณะทีละชิ้นการสแกนตามความกว้างความสูงและความลึกของสีของภาพอินพุตเพื่อสร้างชุดแผนที่คุณลักษณะที่ให้ผลลัพธ์ของเวกเตอร์การคาดคะเนเอาต์พุตในที่สุด (รูปที่ 3)

รูปที่ 3: CNN ที่ใช้สำหรับการตรวจจับวัตถุรูปภาพเกี่ยวข้องกับเซลล์ประสาทจำนวนมากในหลาย ๆ ชั้นทำให้มีความต้องการมากขึ้นบนแพลตฟอร์มประมวลผล (แหล่งรูปภาพ: Aphex34 CC BY-SA 4.0)

รูปที่ 3: CNN ที่ใช้สำหรับการตรวจจับวัตถุรูปภาพเกี่ยวข้องกับเซลล์ประสาทจำนวนมากในหลาย ๆ ชั้นทำให้มีความต้องการมากขึ้นบนแพลตฟอร์มประมวลผล (แหล่งรูปภาพ: Aphex34 CC BY-SA 4.0)

การใช้ FPGA เพื่อเร่งการคำนวณ NN

แม้ว่าจะยังคงมีตัวเลือกมากมายสำหรับการดำเนินการแบบจำลองการอนุมานที่ขอบ แต่ทางเลือกไม่กี่ทางที่ให้การผสมผสานที่ดีที่สุดระหว่างความยืดหยุ่นประสิทธิภาพและประสิทธิภาพการใช้พลังงานที่จำเป็นสำหรับการอนุมานความเร็วสูงที่ใช้งานได้จริงที่ edge ในบรรดาทางเลือกที่พร้อมใช้งานสำหรับ Edge AI นั้น FPGA มีประสิทธิภาพเป็นพิเศษเนื่องจากสามารถให้การดำเนินการที่เน้นการประมวลผลโดยใช้ฮาร์ดแวร์ที่มีประสิทธิภาพสูงในขณะที่ใช้พลังงานค่อนข้างน้อย

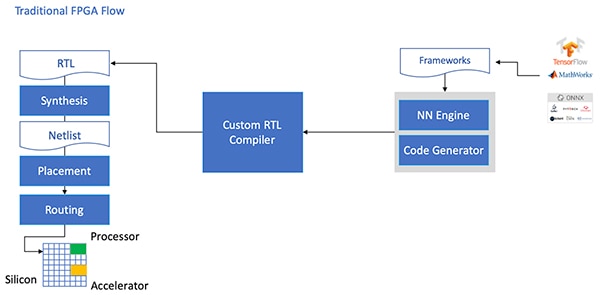

แม้จะมีข้อได้เปรียบ แต่บางครั้ง FPGA ก็ถูกข้ามไปเนื่องจากขั้นตอนการพัฒนาแบบดั้งเดิมที่อาจสร้างความกังวลใจให้กับนักพัฒนาที่ไม่มีประสบการณ์ FPGA ที่กว้างขวาง ในการสร้างการใช้งาน FPGA ที่มีประสิทธิภาพของโมเดล NN ที่สร้างโดยกรอบงาน NN ผู้พัฒนาจะต้องเข้าใจความแตกต่างของการแปลงโมเดลเป็นภาษาการถ่ายโอนการลงทะเบียน (RTL) การสังเคราะห์การออกแบบและการทำงานผ่านสถานที่สุดท้ายและการออกแบบทางกายภาพของเส้นทาง ขั้นตอนในการสร้างการนำไปใช้งานที่เหมาะสมที่สุด (รูปที่ 4)

รูปที่ 4: ในการใช้โมเดล NN บน FPGA นักพัฒนาจำเป็นต้องเข้าใจวิธีการแปลงโมเดลเป็น RTL และทำงานผ่านโฟลว์ FPGA แบบเดิม (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 4: ในการใช้โมเดล NN บน FPGA นักพัฒนาจำเป็นต้องเข้าใจวิธีการแปลงโมเดลเป็น RTL และทำงานผ่านโฟลว์ FPGA แบบเดิม (แหล่งที่มาภาพ: Microchip Technology)

ด้วย โพลาร์ไฟร์ FPGA ซอฟต์แวร์เฉพาะและทรัพย์สินทางปัญญา (IP) ที่เกี่ยวข้อง Microchip Technology นำเสนอโซลูชันที่ทำให้การอนุมานที่มีประสิทธิภาพสูงและใช้พลังงานต่ำที่ขอบพร้อมใช้งานสำหรับนักพัฒนาที่ไม่มีประสบการณ์ FPGA

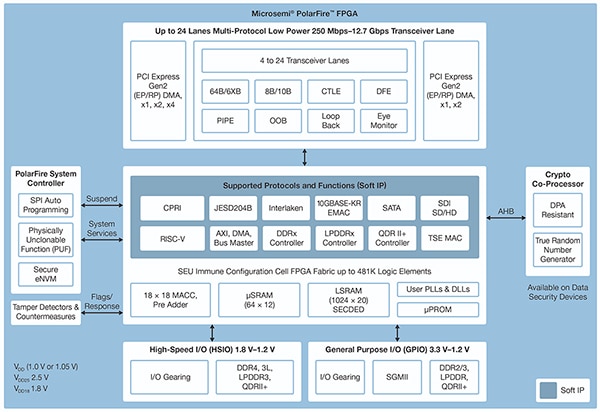

PolarFire FPGA ผลิตด้วยเทคโนโลยีขั้นสูงที่ไม่ระเหยได้รับการออกแบบมาเพื่อเพิ่มความยืดหยุ่นและประสิทธิภาพสูงสุดในขณะที่ลดการใช้พลังงาน นอกเหนือจากอินเทอร์เฟซความเร็วสูงมากมายสำหรับการสื่อสารและอินพุต/เอาต์พุต (I/O) แล้วยังมีแฟบริก FPGA ที่สามารถรองรับการทำงานขั้นสูงโดยใช้คอร์ IP แบบอ่อนรวมถึงโปรเซสเซอร์ RISC-V ตัวควบคุมหน่วยความจำขั้นสูงและอื่น ๆ ระบบย่อยของอินเตอร์เฟสมาตรฐาน (รูปที่ 5)

รูปที่ 5: สถาปัตยกรรม Microchip Technology PolarFire เป็นเนื้อผ้าที่ออกแบบมาเพื่อรองรับความต้องการการออกแบบที่มีประสิทธิภาพสูงรวมถึงการใช้โมเดลการอนุมานที่เน้นการประมวลผล (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 5: สถาปัตยกรรม Microchip Technology PolarFire เป็นเนื้อผ้าที่ออกแบบมาเพื่อรองรับความต้องการการออกแบบที่มีประสิทธิภาพสูงรวมถึงการใช้โมเดลการอนุมานที่เน้นการประมวลผล (แหล่งที่มาภาพ: Microchip Technology)

ผ้า PolarFire FPGA มีชุดองค์ประกอบลอจิกและบล็อกพิเศษที่หลากหลายซึ่งได้รับการสนับสนุนในช่วงความสามารถโดยสมาชิกที่แตกต่างกันของตระกูล PolarFire FPGA รวมถึง MPF100T, MPF200T, MPF300Tและ MPF500T ซีรีส์ (ตารางที่ 1)

|

ตารางที่ 1: คุณสมบัติและความสามารถของผ้า FPGA ที่หลากหลายมีอยู่ในซีรีส์ PolarFire (แหล่งที่มาของตาราง: DigiKey อ้างอิงจากแผ่นข้อมูล PolarFire ของ Microchip Technology)

ในบรรดาคุณสมบัติที่น่าสนใจเป็นพิเศษสำหรับการเร่งการอนุมานสถาปัตยกรรม PolarFire มีบล็อกการคำนวณเฉพาะที่ให้ฟังก์ชันการสะสมทวีคูณ (MAC) ที่มีลายเซ็น 18 บิต× 18 บิตพร้อมตัวเพิ่มล่วงหน้า โหมดผลิตภัณฑ์จุดในตัวใช้บล็อกการคำนวณเดียวในการดำเนินการคูณ 8 บิตสองครั้งซึ่งเป็นกลไกในการเพิ่มขีดความสามารถโดยใช้ประโยชน์จากผลกระทบเล็กน้อยของการหาจำนวนแบบจำลองต่อความแม่นยำ

นอกเหนือจากการเร่งการดำเนินการทางคณิตศาสตร์แล้วสถาปัตยกรรม PolarFire ยังช่วยลดความแออัดของหน่วยความจำที่พบเมื่อใช้แบบจำลองการอนุมานบนสถาปัตยกรรมวัตถุประสงค์ทั่วไปเช่นหน่วยความจำแบบกระจายขนาดเล็กสำหรับจัดเก็บผลลัพธ์ระดับกลางที่สร้างขึ้นระหว่างการดำเนินการอัลกอริทึม NN นอกจากนี้ค่าน้ำหนักและค่าอคติของแบบจำลอง NN ยังสามารถจัดเก็บไว้ในหน่วยความจำแบบอ่านอย่างเดียว (ROM) แบบสัมประสิทธิ์ 16 ค่าสัมประสิทธิ์ 18 บิตที่สร้างขึ้นจากองค์ประกอบลอจิกที่อยู่ใกล้บล็อกการคำนวณ

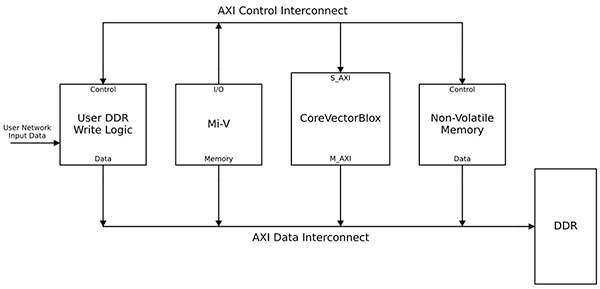

เมื่อรวมกับคุณสมบัติอื่น ๆ ของผ้า PolarFire FPGA บล็อกการคำนวณเป็นรากฐานสำหรับ CoreVectorBlox IP ระดับที่สูงขึ้นของ Microchip Technology สิ่งนี้ทำหน้าที่เป็นเครื่อง NN ที่ยืดหยุ่นซึ่งสามารถรัน NN ประเภทต่างๆได้ นอกจากชุดของการลงทะเบียนควบคุมแล้ว CoreVectorBlox IP ยังมีบล็อกการทำงานที่สำคัญสามบล็อก:

- ไมโครคอนโทรลเลอร์: ซอฟต์โปรเซสเซอร์ RISC-V อย่างง่ายที่อ่านอ็อบเจ็กต์ไบนารีไบนารีของเฟิร์มแวร์ Microchip และไฟล์ NN BLOB เฉพาะของผู้ใช้จากที่จัดเก็บข้อมูลภายนอก มันควบคุมการทำงานของ CoreVectorBlox โดยรวมโดยดำเนินการตามคำสั่งจากเฟิร์มแวร์ BLOB

- เมทริกซ์โปรเซสเซอร์ (MXP): หน่วยประมวลผลแบบอ่อนประกอบด้วยหน่วยตรรกะเลขคณิต 32 บิต (ALU) แปดหน่วยและได้รับการออกแบบมาเพื่อดำเนินการแบบขนานบนเวกเตอร์ข้อมูลโดยใช้การดำเนินการเทนเซอร์ตามองค์ประกอบรวมถึงการเพิ่มย่อย xor shift mul dotprod และอื่น ๆ โดยใช้ความแม่นยำแบบ 8 บิต 16 บิตและ 32 บิตแบบผสมตามต้องการ

- ตัวเร่งความเร็ว CNN: เร่งการดำเนินการ MXP โดยใช้อาร์เรย์สองมิติของฟังก์ชัน MAC ที่ใช้งานโดยใช้บล็อกการคำนวณและทำงานด้วยความแม่นยำ 8 บิต

ระบบประมวลผล NN ที่สมบูรณ์จะรวมบล็อก IP ของ CoreVectorBlox หน่วยความจำตัวควบคุมหน่วยความจำและตัวประมวลผลโฮสต์เช่นแกนประมวลผลซอฟต์แวร์ Microsoft RISC-V (Mi-V) (รูปที่ 6)

รูปที่ 6: CoreVectorBlox IP block ทำงานร่วมกับโฮสต์โปรเซสเซอร์เช่นไมโครคอนโทรลเลอร์ Mi-V RISC-V ของ Microchip เพื่อใช้รูปแบบการอนุมาน NN (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 6: CoreVectorBlox IP block ทำงานร่วมกับโฮสต์โปรเซสเซอร์เช่นไมโครคอนโทรลเลอร์ Mi-V RISC-V ของ Microchip เพื่อใช้รูปแบบการอนุมาน NN (แหล่งที่มาภาพ: Microchip Technology)

ในการใช้งานระบบวิดีโอโปรเซสเซอร์โฮสต์จะโหลดเฟิร์มแวร์และ BLOB ของเครือข่ายจากหน่วยความจำแฟลชระบบและคัดลอกลงในหน่วยความจำเข้าถึงโดยสุ่ม (RAM) อัตราข้อมูลสองเท่า (DDR) เพื่อใช้โดยบล็อก CoreVectorBlox เมื่อเฟรมวิดีโอมาถึงโปรเซสเซอร์โฮสต์จะเขียนลงใน DDR RAM และส่งสัญญาณไปที่บล็อก CoreVectorBlox เพื่อเริ่มประมวลผลภาพ หลังจากรันรูปแบบการอนุมานที่กำหนดไว้ใน BLOB เครือข่ายบล็อก CoreVectorBlox จะเขียนผลลัพธ์รวมถึงการจัดประเภทรูปภาพกลับไปที่ DDR RAM เพื่อใช้โดยแอปพลิเคชันเป้าหมาย

ขั้นตอนการพัฒนาทำให้การใช้งาน NN FPGA ง่ายขึ้น

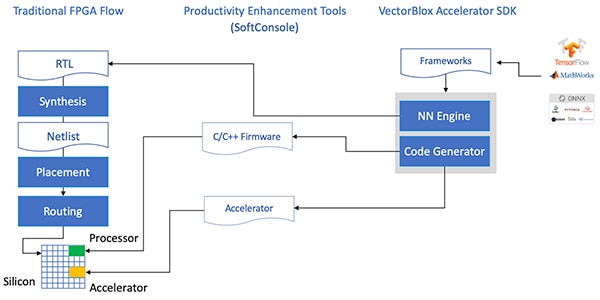

Microchip ป้องกันนักพัฒนาจากความซับซ้อนของการนำแบบจำลองการอนุมาน NN ไปใช้บน PolarFire FPGA แทนที่จะจัดการกับรายละเอียดของโฟลว์ FPGA แบบเดิมนักพัฒนาโมเดล NN จะทำงานกับเฟรมเวิร์ก NN ของพวกเขาตามปกติและโหลดโมเดลผลลัพธ์ลงในอุปกรณ์จาก Microchip Technology คือ VectorBlox Accelerator Software Development Kit (SDK) SDK สร้างชุดไฟล์ที่ต้องการรวมถึงไฟล์ที่จำเป็นสำหรับขั้นตอนการพัฒนา FPGA ปกติและไฟล์เฟิร์มแวร์และเครือข่าย BLOB ที่กล่าวถึงก่อนหน้านี้ (รูปที่ 7)

รูปที่ 7: VectorBlox Accelerator SDK จัดการรายละเอียดของการนำโมเดล NN ไปใช้บน FPGA สร้างไฟล์ที่จำเป็นโดยอัตโนมัติในการออกแบบและรันโมเดลการอนุมานตาม FPGA (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 7: VectorBlox Accelerator SDK จัดการรายละเอียดของการนำโมเดล NN ไปใช้บน FPGA สร้างไฟล์ที่จำเป็นโดยอัตโนมัติในการออกแบบและรันโมเดลการอนุมานตาม FPGA (แหล่งที่มาภาพ: Microchip Technology)

เนื่องจากโฟลว์ VectorBlox Accelerator SDK ซ้อนทับการออกแบบ NN บนเอ็นจิ้น NN ที่ใช้ใน FPGA NN ที่แตกต่างกันจึงสามารถทำงานบนการออกแบบ FPGA เดียวกันได้โดยไม่จำเป็นต้องทำโฟลว์สังเคราะห์การออกแบบ FPGA ซ้ำ นักพัฒนาสร้างโค้ด C / C ++ สำหรับระบบผลลัพธ์และสามารถสลับโมเดลภายในระบบได้ทันทีหรือรันโมเดลพร้อมกันโดยใช้การแบ่งเวลา

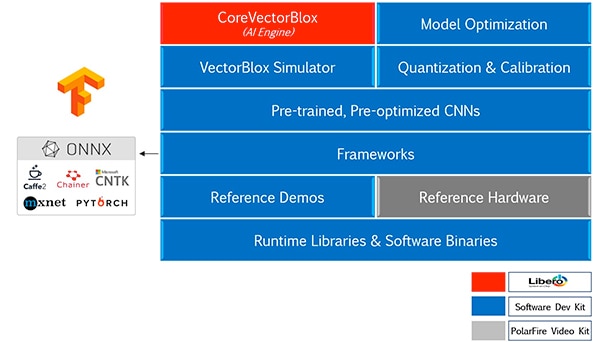

VectorBlox Accelerator SDK ผสานเทคโนโลยีไมโครชิป Libero ชุดออกแบบ FPGA พร้อมชุดความสามารถที่ครอบคลุมสำหรับการพัฒนาแบบจำลองการอนุมาน NN นอกเหนือจากการเพิ่มประสิทธิภาพโมเดลการหาปริมาณและบริการสอบเทียบแล้ว SDK ยังมีโปรแกรมจำลอง NN ที่ช่วยให้นักพัฒนาใช้ไฟล์ BLOB เดียวกันเพื่อประเมินโมเดลก่อนที่จะใช้ในการใช้งานฮาร์ดแวร์ FPGA (รูปที่ 8)

รูปที่ 8: VectorBlox Accelerator SDK มีชุดบริการที่ครอบคลุมซึ่งออกแบบมาเพื่อเพิ่มประสิทธิภาพการใช้งาน FPGA ของแบบจำลองการอนุมานที่สร้างขึ้นโดยเฟรมเวิร์ก (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 8: VectorBlox Accelerator SDK มีชุดบริการที่ครอบคลุมซึ่งออกแบบมาเพื่อเพิ่มประสิทธิภาพการใช้งาน FPGA ของแบบจำลองการอนุมานที่สร้างขึ้นโดยเฟรมเวิร์ก (แหล่งที่มาภาพ: Microchip Technology)

VectorBlox Accelerator SDK รองรับโมเดลในรูปแบบ Open Neural Network Exchange (ONNX) รวมถึงโมเดลจากเฟรมเวิร์กต่าง ๆ เช่น TensorFlow, Caffe, Chainer, PyTorch และ MXNET สถาปัตยกรรม CNN ที่รองรับ ได้แก่ MNIST เวอร์ชัน MobileNet ResNet-50 Tiny Yolo V2 และ Tiny Yolo V3 ไมโครชิปกำลังดำเนินการเพื่อขยายการสนับสนุนเพื่อรวมเครือข่ายส่วนใหญ่ไว้ในโอเพนซอร์ส ชุดเครื่องมือ OpenVINO โมเดลเปิด zoo ของรุ่นก่อนการฝึกอบรม ได้แก่ Yolo V3, Yolo V4, RetinaNet และ SSD-MobileNet และอื่น ๆ อีกมากมาย

ชุดวิดีโอสาธิตการอนุมานโดย FPGA

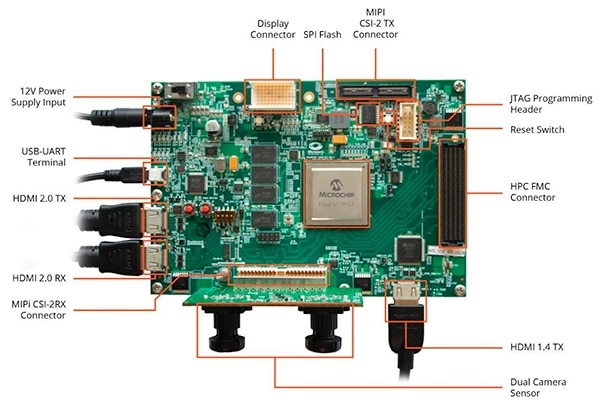

เพื่อช่วยให้นักพัฒนาก้าวไปสู่การพัฒนาแอปพลิเคชันการมองเห็นแบบฝังอัจฉริยะได้อย่างรวดเร็ว Microchip Technology จึงจัดเตรียมแอปพลิเคชันตัวอย่างที่ครอบคลุมซึ่งออกแบบมาเพื่อทำงานใน MPF300-VIDEO-KIT ของบริษัท PolarFire FPGA Video และชุดเครื่องมือ Imaging และการออกแบบอ้างอิง

จาก Microchip MPF300T PolarFire FPGA บอร์ดของชุดนี้จะรวมเซ็นเซอร์กล้องคู่, แรม 4 (DDR4) อัตราข้อมูลสองเท่า, หน่วยความจำแฟลช, การจัดการพลังงานและอินเทอร์เฟซที่หลากหลาย (รูปที่ 9)

รูปที่ 9: MPF300-VIDEO-KIT PolarFire FPGA Video และชุดเครื่องมือ Imaging และซอฟต์แวร์ที่เกี่ยวข้องช่วยให้นักพัฒนาสามารถเริ่มต้นการอนุมานโดยใช้ FPGA ในแอปพลิเคชันการมองเห็นแบบฝังอัจฉริยะได้อย่างรวดเร็ว (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 9: MPF300-VIDEO-KIT PolarFire FPGA Video และชุดเครื่องมือ Imaging และซอฟต์แวร์ที่เกี่ยวข้องช่วยให้นักพัฒนาสามารถเริ่มต้นการอนุมานโดยใช้ FPGA ในแอปพลิเคชันการมองเห็นแบบฝังอัจฉริยะได้อย่างรวดเร็ว (แหล่งที่มาภาพ: Microchip Technology)

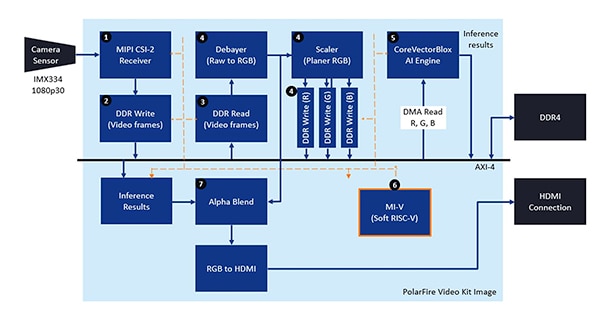

ชุดนี้มาพร้อมกับโครงการออกแบบ Libero ที่สมบูรณ์ซึ่งใช้ในการสร้างเฟิร์มแวร์และไฟล์ BLOB ของเครือข่าย หลังจากตั้งโปรแกรมไฟล์ BLOB ลงในหน่วยความจำแฟลชในตัวนักพัฒนาคลิกที่ปุ่มเรียกใช้ใน Libero เพื่อเริ่มการสาธิตซึ่งประมวลผลภาพวิดีโอจากเซ็นเซอร์กล้องและแสดงผลการอนุมานบนจอแสดงผล (รูปที่ 10)

รูปที่ 10: Microchip Technology PolarFire FPGA Video and Imaging Kit แสดงให้เห็นถึงวิธีการออกแบบและใช้การติดตั้ง FPGA ของระบบการมองเห็นแบบฝังตัวอัจฉริยะที่สร้างขึ้นโดยใช้เอ็นจิ้น Microchip CoreVectorBlox NN (แหล่งที่มาภาพ: Microchip Technology)

รูปที่ 10: Microchip Technology PolarFire FPGA Video and Imaging Kit แสดงให้เห็นถึงวิธีการออกแบบและใช้การติดตั้ง FPGA ของระบบการมองเห็นแบบฝังตัวอัจฉริยะที่สร้างขึ้นโดยใช้เอ็นจิ้น Microchip CoreVectorBlox NN (แหล่งที่มาภาพ: Microchip Technology)

สำหรับเฟรมวิดีโออินพุตแต่ละเฟรมระบบที่ใช้ FPGA ดำเนินการตามขั้นตอนต่อไปนี้ (โดยหมายเลขขั้นตอนที่สัมพันธ์กับรูปที่ 10):

- โหลดเฟรมออกจากกล้อง

- จัดเก็บเฟรมใน RAM

- อ่านเฟรมจากแรม

- แปลงภาพดิบเป็น RGB, Planer RGB และเก็บผลลัพธ์ไว้ใน RAM

- โปรเซสเซอร์ Mi-V soft RISC-V เริ่มต้นเอ็นจิ้น CoreVectorBlox ซึ่งดึงภาพจาก RAM ทำการอนุมานและเก็บผลลัพธ์ความน่าจะเป็นในการจำแนกประเภทกลับไปที่ RAM

- Mi-V ใช้ผลลัพธ์เพื่อสร้างเฟรมซ้อนทับที่มีกรอบล้อมรอบผลการจัดประเภทและข้อมูลเมตาอื่น ๆ และเก็บเฟรมไว้ใน RAM

- เฟรมต้นฉบับผสมผสานกับเฟรมโอเวอร์เลย์และเขียนลงในจอแสดงผล HDMI

การสาธิตรองรับการเร่งความเร็วของรุ่น Tiny Yolo V3 และ MobileNet V2 แต่นักพัฒนาสามารถเรียกใช้รุ่นอื่น ๆ ที่รองรับ SDK โดยใช้วิธีการที่อธิบายไว้ก่อนหน้านี้โดยทำการเปลี่ยนแปลงรหัสเล็กน้อยเพื่อเพิ่มชื่อรุ่นและข้อมูลเมตาลงในรายการที่มีอยู่ซึ่งมีโมเดลเริ่มต้นสองรุ่น

สรุป

อัลกอริทึม AI เช่นโมเดล NN มักจะกำหนดปริมาณงานที่ต้องใช้การประมวลผลสูงซึ่งต้องการทรัพยากรการประมวลผลที่มีประสิทธิภาพมากกว่าที่มีอยู่ในโปรเซสเซอร์วัตถุประสงค์ทั่วไป ในขณะที่ FPGA มีความพร้อมที่จะตอบสนองความต้องการด้านประสิทธิภาพและความต้องการพลังงานต่ำของการดำเนินการแบบจำลองการอนุมานวิธีการพัฒนา FPGA แบบเดิมอาจดูซับซ้อนซึ่งมักทำให้นักพัฒนาหันไปใช้โซลูชันที่ไม่เหมาะสม

ดังที่แสดงให้เห็นว่าการใช้ IP และซอฟต์แวร์เฉพาะจาก Microchip Technology นักพัฒนาที่ไม่มีประสบการณ์ FPGA สามารถใช้การออกแบบที่ใช้การอนุมานได้ดีกว่าซึ่งสามารถตอบสนองความต้องการด้านประสิทธิภาพพลังงานและกำหนดการออกแบบได้

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.