สาเหตุที่ใช้ Efinix FPGA สำหรับการสร้างภาพ AI/ML และวิธีการใช้งาน — ตอนที่ 1: เริ่มต้นใช้งาน

Contributed By DigiKey's European Editors

2023-04-20

หมายเหตุจากผู้เรียบเรียง: แนวทางใหม่สำหรับสถาปัตยกรรม FPGA ทำให้เกิดการควบคุมที่ละเอียดยิ่งขึ้นและมีความยืดหยุ่นมากขึ้นเพื่อตอบสนองความต้องการของแมชชีนเลิร์นนิ่ง (ML) และปัญญาประดิษฐ์ (AI) ตอนที่ 1 ของชุดบทความจะแนะนำสถาปัตยกรรมดังกล่าวจาก Efinix และวิธีเริ่มต้นใช้งานโดยใช้บอร์ดพัฒนา ตอนที่ 2 กล่าวถึงการเชื่อมต่อบอร์ดพัฒนากับอุปกรณ์ภายนอกและอุปกรณ์ต่อพ่วง เช่น กล้อง

FPGA มีบทบาทสำคัญในการใช้งานจำนวนมาก ตั้งแต่การควบคุมอุตสาหกรรมและความปลอดภัย ไปจนถึงวิทยาการหุ่นยนต์ การบินและอวกาศ และยานยนต์ ด้วยลักษณะที่ยืดหยุ่นของคอร์ลอจิกที่ตั้งโปรแกรมได้และความสามารถในการเชื่อมต่อที่กว้าง หนึ่งในการใช้งาน FPGA ที่เพิ่มขึ้นคือการประมวลผลภาพเมื่อต้องการใช้การอนุมานของ ML ซึ่ง FPGA เหมาะอย่างยิ่งสำหรับการใช้งานโซลูชันที่มีอินเทอร์เฟซกล้องความเร็วสูงหลายตัว นอกจากนี้ FPGA ยังช่วยให้สามารถใช้งานไปป์ไลน์การประมวลผลเฉพาะในลอจิกได้ ซึ่งจะช่วยขจัดปัญหาคอขวดที่จะเกี่ยวข้องกับโซลูชันที่ใช้ CPU หรือ GPU

อย่างไรก็ตามการใช้งานของเหล่านักพัฒนาต้องการฟังก์ชัน ML/AI และการควบคุมหรือการเลือกเส้นทางและลอจิกที่ละเอียดยิ่งขึ้น ซึ่งเกินกว่าที่สถาปัตยกรรม FPGA แบบคลาสสิกที่มีบล็อกลอจิกผสม (CLB) จะสามารถให้ได้ ซึ่งจะมีแนวทางใหม่สำหรับสถาปัตยกรรม FPGA ที่สามารถแก้ไขปัญหาเหล่านี้ ตัวอย่างเช่น สถาปัตยกรรมควอนตัมของ Efinix ใช้บล็อก eXchangeable Logic and Routing (XLR)

บทความนี้กล่าวถึงคุณลักษณะที่สำคัญของสถาปัตยกรรม Efinix FPGA โดยเน้นย้ำถึงความสามารถด้าน AI/ML และแนะนำการใช้งานจริง จากนั้นจะกล่าวถึงบอร์ดพัฒนาและเครื่องมือที่เกี่ยวข้องซึ่งนักพัฒนาสามารถใช้เพื่อเริ่มต้นการออกแบบภาพ AI/ML ถัดไปได้อย่างรวดเร็ว

อุปกรณ์ Efinix FPGA

ปัจจุบัน Efinix นำเสนออุปกรณ์สองกลุ่ม ในขั้นต้นจะแนะนำกลุ่ม Trion ซึ่งมีความหนาแน่นของลอจิกตั้งแต่ 4000 (4K) ถึง 120K องค์ประกอบลอจิก (LE) และสร้างขึ้นโดยใช้กระบวนการ SMIC 40LL และกลุ่มอุปกรณ์ใหม่ล่าสุดคือ Titanium ที่มีความหนาแน่นของลอจิกตั้งแต่ 35K ถึง 1 ล้าน (1M) องค์ประกอบลอจิก และสร้างขึ้นบนโหนด TSMC 16 นาโนเมตร (nm) ที่ได้รับความนิยมอย่างมาก

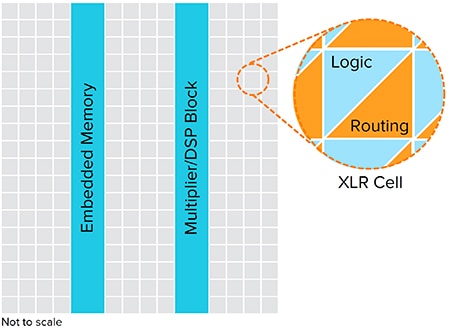

ทั้งสองมีพื้นฐานมาจากสถาปัตยกรรมควอนตัม ซึ่งเป็นเอกลักษณ์ของ FPGA โดยสถาปัตยกรรม FPGA มาตรฐานอ้างอิงมาจาก CLB ซึ่งอยู่ในระดับที่ง่ายที่สุด ประกอบด้วย Look-up Table (LUT) และ Flip-flop ซึ่ง CLB ใช้สมการลอจิกที่เชื่อมต่อกันผ่านการเลือกเส้นทาง แต่สถาปัตยกรรมควอนตัมของ Efinix จะไม่ใช้บล็อกลอจิกและการกำหนดเส้นทางที่แตกต่างกันโดยใช้บล็อก XLR

สิ่งที่ทำให้บล็อก XLR ไม่เหมือนใครคือสามารถกำหนดค่าให้ทำงานเป็นเซลล์ลอจิกที่มี LUT, รีจิสเตอร์และแอดเดอร์ หรือเมทริกซ์การกำหนดเส้นทาง โดยวิธีการนี้นำเสนอสถาปัตยกรรมที่ละเอียดมากกว่า ซึ่งให้ความยืดหยุ่นในการกำหนดเส้นทาง ทำให้สามารถใช้งานที่มีการใช้ลอจิกมากหรือมีการกำหนดเส้นทางจำนวนมากเพื่อให้ได้ประสิทธิภาพที่ต้องการ

รูปที่ 1: สิ่งที่ทำให้บล็อก XLR ไม่เหมือนใครคือสามารถกำหนดค่าให้ทำงานเป็นเซลล์ลอจิกที่มี LUT, รีจิสเตอร์และแอดเดอร์ หรือเมทริกซ์การกำหนดเส้นทาง (แหล่งที่มาภาพ: Efinix)

รูปที่ 1: สิ่งที่ทำให้บล็อก XLR ไม่เหมือนใครคือสามารถกำหนดค่าให้ทำงานเป็นเซลล์ลอจิกที่มี LUT, รีจิสเตอร์และแอดเดอร์ หรือเมทริกซ์การกำหนดเส้นทาง (แหล่งที่มาภาพ: Efinix)

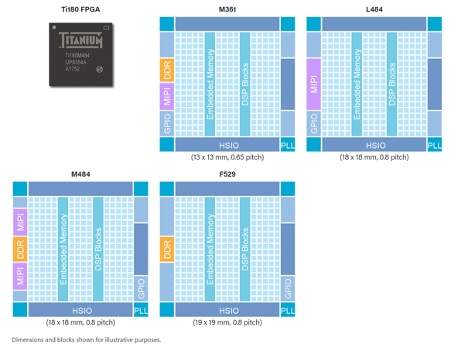

เนื่องจากเป็นกลุ่มอุปกรณ์ใหม่ล่าสุด อุปกรณ์ Titanium นำเสนอคุณสมบัติขั้นสูงที่สุดสำหรับนักพัฒนา (รูปที่ 2) นอกเหนือจากแกน XLR แล้ว อุปกรณ์เหล่านี้ยังมีลิงค์อนุกรมหลายกิกะบิตซึ่งทำงานที่ความเร็ว 16 กิกะบิตต่อวินาที (Gbps) หรือ 25.8 Gbps ขึ้นอยู่กับอุปกรณ์ที่เลือก ลิงค์หลายกิกะบิตเหล่านี้มีความสำคัญต่อการใช้งานในการถ่ายโอนข้อมูลความเร็วสูงทั้งในและนอกชิป

รูปที่ 2: Titanium FPGA Ti180 มีตัวเลือกมากมายขึ้นอยู่กับความกว้างของบัส I/O และข้อกำหนดของหน่วยความจำ (แหล่งที่มาภาพ: Efinix)

รูปที่ 2: Titanium FPGA Ti180 มีตัวเลือกมากมายขึ้นอยู่กับความกว้างของบัส I/O และข้อกำหนดของหน่วยความจำ (แหล่งที่มาภาพ: Efinix)

อุปกรณ์รุ่น Titanium ยังมีความสามารถในการเชื่อมต่ออินพุต/เอาต์พุต (I/O) ที่หลากหลาย ซึ่งสามารถจัดกลุ่มเป็น I/O สำหรับวัตถุประสงค์ทั่วไป (GPIO) และสามารถรองรับมาตรฐาน I/O แบบซิงเกิลเอ็นต์ เช่น CMOS แรงดันต่ำ ( LVCMOS) ที่ 3.3 โวลต์ 2.5 โวลต์ และ 1.8 โวลต์

สำหรับการเชื่อมต่อความเร็วสูงและแบบดิฟเฟอเรนเชียล อุปกรณ์ Titanium ให้ I/O ความเร็วสูง (HSIO) ซึ่งรองรับมาตรฐาน I/O แบบซิงเกิลเอ็นต์ เช่น LVCMOS ที่ 1.2 โวลต์ 1.5 โวลต์ และ SSTL และ HSTL มาตรฐาน I/O ดิฟเฟอเรนเชียลที่ HSIO รองรับ ได้แก่ การส่งสัญญาณดิฟเฟอเรนเชียลแรงดันต่ำ (LVDS), ดิฟเฟอเรนเชียล SSTL และ HSTL

FPGA สมัยใหม่ยังต้องการหน่วยความจำแบนด์วิธสูงที่เชื่อมต่ออย่างใกล้ชิด ซึ่งใช้ในการจัดเก็บเฟรมภาพสำหรับการประมวลผลภาพ ข้อมูลตัวอย่างสำหรับการประมวลผลสัญญาณ รวมทั้งเพื่อเรียกใช้ระบบปฏิบัติการและซอฟต์แวร์สำหรับโปรเซสเซอร์ที่ใช้งานภายใน FPGA โดยกลุ่มอุปกรณ์ Titanium ให้ความสามารถในการเชื่อมต่อกับ DDR4 และ DDR4(x) พลังงานต่ำ (LPDDR4(x)) โดยมีการรองรับความกว้างของบัสที่ x32 (J) หรือ x16 (M) ขึ้นอยู่กับอุปกรณ์ Titanium ที่เลือก ในขณะที่อุปกรณ์บางอย่างไม่รองรับ LPDDR4 (L)

Titanium FPGA เป็นแบบ SRAM และต้องการหน่วยความจำการกำหนดค่า โดยการกำหนดค่าอุปกรณ์ดำเนินการโดย Serial Peripheral Interconnect (SPI) มาสเตอร์/สเลฟหรือ JTAG เพื่อให้แน่ใจว่าวิธีการกำหนดค่านี้มีความปลอดภัย Titanium FPGA ใช้การเข้ารหัส AES GCM ของบิตสตรีม พร้อมด้วย AES GCM และ RSA-4096 เพื่อรับรองความถูกต้องของบิตสตรีม ซึ่งจำเป็นต้องมีการรักษาความปลอดภัยที่แข็งแกร่งเช่นนี้ เนื่องจาก FPGA ถูกปรับใช้ที่เอดจ์ซึ่งผู้ประสงค์ร้ายสามารถเข้าถึงและควบคุมพฤติกรรมของอุปกรณ์ได้

แนะนำบอร์ดพัฒนา

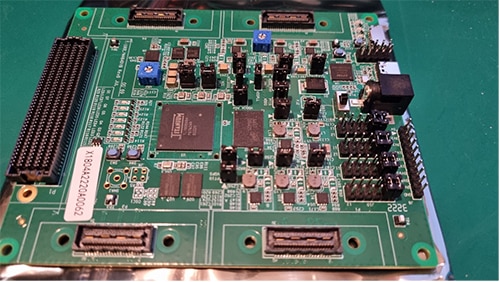

บอร์ดพัฒนาเป็นองค์ประกอบที่สำคัญของกระบวนการประเมิน FPGA เนื่องจากสามารถใช้เพื่อสำรวจความสามารถของอุปกรณ์และการใช้งานต้นแบบ ซึ่งจะช่วยลดความเสี่ยงโดยรวม บอร์ดพัฒนาชุดแรกที่มีไว้เพื่อประเมิน Titanium FPGA และเริ่มสร้างต้นแบบการใช้งานคือ Ti180 M484 (รูปที่ 3) โดยที่บอร์ดมีคอนเนคเตอร์ FPGA Mezzanine Card (FMC) และคอนเนคเตอร์ Samtec QSE สี่ตัว

รูปที่ 3: ชุดพัฒนา Ti180 M484 มีคอนเนคเตอร์ FMC และคอนเนคเตอร์ Samtec QSE สี่ตัว ใช้ควบคู่ไปกับ Titanium FPGA (แหล่งที่มาภาพ: Adam Taylor)

รูปที่ 3: ชุดพัฒนา Ti180 M484 มีคอนเนคเตอร์ FMC และคอนเนคเตอร์ Samtec QSE สี่ตัว ใช้ควบคู่ไปกับ Titanium FPGA (แหล่งที่มาภาพ: Adam Taylor)

Ti180 FPGA ที่ติดตั้งกับบอร์ดพัฒนานี้มีเซลล์ XLR 172K เซลล์, นาฬิกาสากล 32 วงจร, องค์ประกอบการประมวลผลสัญญาณดิจิตอล (DSP) 640 องค์ประกอบ และ RAM แบบฝัง 13 เมกะบิต (Mbits) โดยองค์ประกอบ DSP ให้ความสามารถในการใช้การคูณจุดคงที่ 18 x 19 และการคูณ 48 บิต ซึ่ง DSP นี้สามารถปรับให้เหมาะสมสำหรับการดำเนินการหลายข้อมูลด้วยคำสั่งเดียว (SIMD) ที่ใช้ในการกำหนดค่าแบบคู่หรือสี่ส่วน นอกจากนี้ยังสามารถกำหนดค่าองค์ประกอบ DSP เพื่อดำเนินการกับจุดลอยตัวได้

เช่นเดียวกับบอร์ดพัฒนาส่วนใหญ่ บอร์ดพัฒนา Ti180 มีไฟ LED และปุ่มที่เรียบง่าย อย่างไรก็ตาม พลังที่แท้จริงของมันมาจากความสามารถในการเชื่อมต่อ โดยบอร์ดพัฒนา Ti180 มีคอนเนคเตอร์ FMC แบบจำนวนพินต่ำที่ช่วยให้เชื่อมต่ออุปกรณ์ต่อพ่วงได้หลากหลาย เนื่องจากเป็นมาตรฐานที่ใช้กันอย่างแพร่หลาย จึงมีการ์ด FMC จำนวนมากที่สามารถเชื่อมต่อกับตัวแปลงอนาล็อกเป็นดิจิตอล (ADC) ความเร็วสูง,ตัวแปลงดิจิตอลเป็นอนาล็อก (DAC), ระบบเครือข่าย และโซลูชันหน่วยความจำ/การจัดเก็บ

นอกจากการเชื่อมต่อ FMC แล้ว บอร์ดยังมีตัวเชื่อมต่อ Samtec QSE สี่ตัว ซึ่งช่วยให้นักพัฒนาสามารถเพิ่มการ์ดส่วนต่อขยายได้ ตัวเชื่อมต่อ QSE เหล่านี้ใช้เพื่อให้อินพุตและเอาต์พุต MIPI โดยตัวเชื่อมต่อ QSE แต่ละตัวจะมีอินพุตหรือเอาต์พุต MIPI

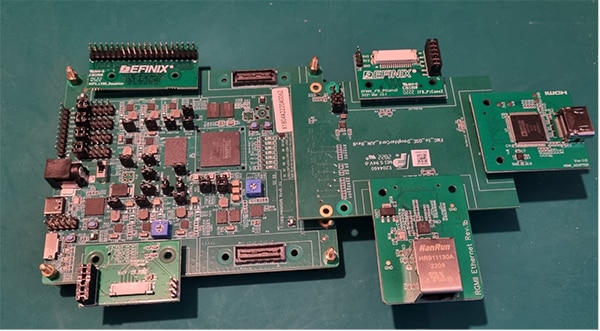

รูปที่ 4: ชุดพัฒนา Ti180 M484 พร้อมตัวเลือกการขยายที่หลากหลายจากคอนเนคเตอร์ QSE และ FMC (แหล่งที่มาภาพ: Adam Taylor)

รูปที่ 4: ชุดพัฒนา Ti180 M484 พร้อมตัวเลือกการขยายที่หลากหลายจากคอนเนคเตอร์ QSE และ FMC (แหล่งที่มาภาพ: Adam Taylor)

บอร์ด Ti180 ยังให้ LPDDR4 256 Mbit เพื่อรองรับหน่วยความจำประสิทธิภาพสูงที่จำเป็นในการประมวลผลภาพหรือสัญญาณ นอกจากนี้ บอร์ดพัฒนายังมีช่วงของตัวเลือกสัญญาณนาฬิกาที่ 25, 33.33, 50 และ 74.25 เมกะเฮิรตซ์ (MHz) ซึ่งสามารถใช้กับ Device Phase Lock Loop (PLL) เพื่อสร้างความถี่ภายในที่แตกต่างกัน

ความสามารถในการตั้งโปรแกรมใหม่และดีบักบนบอร์ดระหว่างการพัฒนานั้นมีความสำคัญอย่างยิ่ง และจำเป็นต้องมีการเชื่อมต่อ JTAG ซึ่งมีให้บนบอร์ดผ่านอินเทอร์เฟซ USB-C นอกจากนี้ ยังมีหหน่วยความจำถาวรในรูปแบบของอุปกรณ์แฟลช NOR ขนาด 256 เมกะบิตสองตัวที่สามารถใช้เพื่อสาธิตโซลูชันการกำหนดค่าได้

บอร์ดนี้ใช้พลังงานจากอแดปเตอร์แปลงไฟสากล 12 โวลต์ที่ให้มาในกล่อง พร้อมทั้งการแบ่ง FMC-to-QSE และการ์ดส่วนขยายที่ใช้ QSE สำหรับ HDMI, Ethernet, MIPI และ LVDS เพื่อแสดงให้เห็นถึงความสามารถในการประมวลผลภาพ Ti180 จึงมีการ์ดลูก RPI คู่และการ์ดกล้อง IMX477 สองแผ่น

สภาพแวดล้อมซอฟต์แวร์

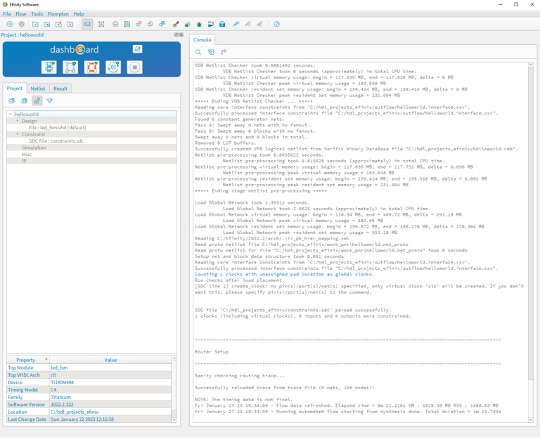

การใช้การออกแบบที่กำหนดเป้าหมายบอร์ดพัฒนา Ti180 ใช้ซอฟต์แวร์ Efinity ของ Efinix ซอฟต์แวร์นี้เปิดใช้งานการสร้างสตรีมบิตผ่านการสังเคราะห์และการ Place & Route นอกจากนี้ยังให้บล็อกทรัพย์สินทางปัญญา (IP) แก่นักพัฒนา การวิเคราะห์เวลา และการดีบักบนชิป

โปรดทราบว่าจำเป็นต้องมีบอร์ดพัฒนาเพื่อเข้าถึงซอฟต์แวร์ Efinity เครื่องมือนี้ไม่มีเวอร์ชันอื่นที่ต้องมีใบอนุญาตเพิ่มเติม ซึ่งแตกต่างจากผู้ขายรายอื่น ๆ

ภายใน Efinity โปรเจ็กต์ใหม่จะถูกสร้างขึ้นโดยกำหนดเป้าหมายไปยังอุปกรณ์ที่เลือก จากนั้นสามารถเพิ่มไฟล์ RTL ในโปรเจ็กต์ และข้อจำกัดที่สร้างขึ้นสำหรับเวลาและการออกแบบ I/O ภายใน Efinity นักพัฒนายังสามารถใช้การออกแบบ I/O โดยใช้ HSIO, GPIO และ I/O พิเศษ

รูปที่ 5: ภายใน Efinity โปรเจ็กต์ใหม่จะถูกสร้างขึ้นโดยกำหนดเป้าหมายไปยังอุปกรณ์ที่เลือก (แหล่งที่มาภาพ: Adam Taylor)

รูปที่ 5: ภายใน Efinity โปรเจ็กต์ใหม่จะถูกสร้างขึ้นโดยกำหนดเป้าหมายไปยังอุปกรณ์ที่เลือก (แหล่งที่มาภาพ: Adam Taylor)

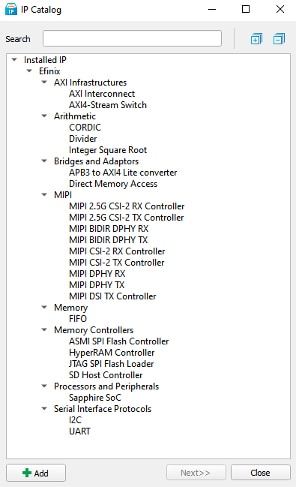

องค์ประกอบที่สำคัญของการออกแบบ FPGA คือการใช้ประโยชน์จาก IP โดยเฉพาะอย่างยิ่งสำหรับ IP ที่ซับซ้อน เช่น การเชื่อมต่อระหว่าง AXI ตัวควบคุมหน่วยความจำ และตัวประมวลผลซอฟต์คอร์ โดย Efinity จะให้บล็อค IP แก่นักพัฒนาที่สามารถใช้เพื่อเร่งกระบวนการออกแบบ

รูปที่ 6: Efinity ให้แคตตาล็อก IP แก่นักพัฒนาซึ่งพวกเขาสามารถใช้เพื่อเร่งกระบวนการออกแบบ (แหล่งที่มาภาพ: Adam Taylor)

รูปที่ 6: Efinity ให้แคตตาล็อก IP แก่นักพัฒนาซึ่งพวกเขาสามารถใช้เพื่อเร่งกระบวนการออกแบบ (แหล่งที่มาภาพ: Adam Taylor)

แม้ว่า FPGA จะใช้โครงสร้างการประมวลผลแบบขนานได้อย่างยอดเยี่ยม การออกแบบ FPGA จำนวนมาก รวมถึงโปรเซสเซอร์ซอฟต์คอร์ ซึ่งทำให้สามารถใช้การประมวลผลตามลำดับ เช่น การสื่อสารผ่านเครือข่าย เพื่อเปิดใช้งานการปรับใช้โปรเซสเซอร์ซอฟต์คอร์ในอุปกรณ์ Efinix โดย Efinity ได้จัดเตรียมเครื่องมือการกำหนดค่า Sapphire system-on-chip (SoC) โดย Sapphire ช่วยให้นักพัฒนาสามารถกำหนดระบบหลายโปรเซสเซอร์ที่มีทั้งแคชและแคชที่เชื่อมโยงกันระหว่างโปรเซสเซอร์หลายตัว พร้อมกับความสามารถในการเรียกใช้ระบบปฏิบัติการ Linux แบบฝังตัว ภายใน Sapphire ผู้พัฒนาสามารถเลือกโปรเซสเซอร์ซอฟต์คอร์ได้ระหว่างหนึ่งและสี่ตัว

โปรเซสเซอร์ซอฟต์คอร์ที่นำมาใช้คือซีพียูซอฟต์ VexRiscV ซึ่งใช้สถาปัตยกรรมชุดคำสั่ง RISC-V โปรเซสเซอร์ VexRiscV เป็นการใช้งานแบบ 32 บิตซึ่งมีส่วนขยายสำหรับการไปป์ไลน์และมีชุดคุณสมบัติที่กำหนดค่าได้ ทำให้เหมาะอย่างยิ่งสำหรับการใช้งานในอุปกรณ์ Efinix การกำหนดค่าทางเลือกประกอบด้วยตัวคูณ คำสั่งอะตอม ส่วนขยายจำนวนจุดลอยตัว และคำสั่งที่บีบอัด ประสิทธิภาพจะอยู่ระหว่าง 0.86 ถึง 1.05 DMIPS/MHz ขึ้นอยู่กับการกำหนดค่าของระบบ SoC

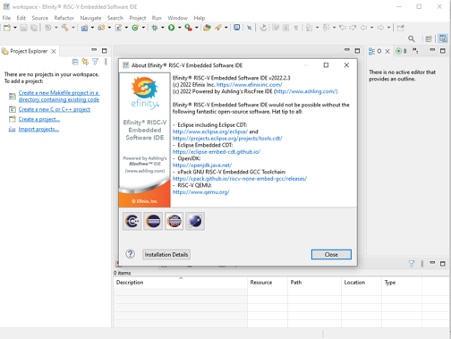

เมื่อสภาพแวดล้อมฮาร์ดแวร์ได้รับการออกแบบและใช้งานในอุปกรณ์ Efinix แล้ว ซอฟต์แวร์แอปพลิเคชันสามารถพัฒนาได้โดยใช้ Ashling RiscFree IDE ซึ่ง Ashling RiscFree เป็น IDE ที่ใช้ Eclipse ที่ช่วยให้สามารถสร้างและคอมไพล์ซอฟต์แวร์แอปพลิเคชันได้ พร้อมกับการดีบักบนเป้าหมายเพื่อปรับแต่งแอปพลิเคชันอย่างละเอียดก่อนการปรับใช้

รูปที่ 7: Ashling RiscFree เป็น IDE ที่ใช้ Eclipse ซึ่งเปิดใช้งานการสร้างและคอมไพล์ซอฟต์แวร์แอปพลิเคชัน พร้อมกับการดีบักบนเป้าหมาย (แหล่งที่มาภาพ: Adam Taylor)

รูปที่ 7: Ashling RiscFree เป็น IDE ที่ใช้ Eclipse ซึ่งเปิดใช้งานการสร้างและคอมไพล์ซอฟต์แวร์แอปพลิเคชัน พร้อมกับการดีบักบนเป้าหมาย (แหล่งที่มาภาพ: Adam Taylor)

หากกำลังพัฒนาโซลูชัน Linux แบบฝัง จะมีวรจรไฟฟ้ารบกวนสำหรับบูตที่จำเป็นทั้งหมด รวมถึง First Stage Boot Loader, OpenSBI, U-Boot และ Linux โดยใช้ Buildroot อีกทางหนึ่ง นักพัฒนาสามารถใช้ FreeRTOS ได้หากต้องการโซลูชันแบบเรียลไทม์

การใช้งาน AI

การเริ่มจากการทำงานซอฟต์คอร์ RISC-V คือการนำ AI ของ Efinix ไปใช้ สิ่งนี้ใช้ประโยชน์จากความสามารถในการสั่งการแบบกำหนดเองของโปรเซสเซอร์ RISC-V เพื่อเปิดใช้งานการเร่งความเร็วของโซลูชัน TensorFlow Lite การใช้โปรเซสเซอร์ RISC-V ยังช่วยให้ผู้ใช้สามารถสร้างคำสั่งแบบกำหนดเองที่สามารถใช้เป็นส่วนหนึ่งของการประมวลผลล่วงหน้าหรือหลังการประมวลผลตามการอนุมานของ AI ทำให้เกิดโซลูชันที่ตอบสนองและกำหนดขึ้นได้

ในการเริ่มต้นใช้งาน AI ขั้นตอนแรกคือการสำรวจโมเดลที่เทรนเรียบร้อยแล้วของ Efinix ซึ่งเป็นไลบรารีของโมเดล AI/ML ที่ปรับให้เหมาะกับเทคโนโลยีปลายทาง สำหรับนักพัฒนาที่ทำงานกับอุปกรณ์ Efinix สามารถเข้าถึงโมเดลเหล่านั้นและเครือข่ายที่เทรนมาแล้วโดยใช้ Jupyter Notebooks หรือ Google Colab เมื่อเครือข่ายได้รับการเทรน จะสามารถแปลงจากแบบจำลองจุดลอยตัวเป็นแบบเชิงปริมาณได้โดยใช้ตัวแปลง TensorFlow Lite

เมื่ออยู่ในรูปแบบ TensorFlow Lite แล้ว สามารถใช้ตัวเร่งความเร็ว tinyML ของ Efinix เพื่อสร้างโซลูชันที่ปรับใช้ได้บนโซลูชัน RISC-V ตัวสร้าง TinyML ช่วยให้นักพัฒนาสามารถปรับแต่งการใช้งานตัวเร่งและสร้างไฟล์โครงการได้ เมื่อปรับใช้ในลักษณะนี้ การเร่งความเร็วสามารถอยู่ระหว่าง 4x ถึง 200x ขึ้นอยู่กับสถาปัตยกรรมที่เลือกและการปรับแต่ง

สรุป

อุปกรณ์ Efinix ช่วยให้นักพัฒนามีความยืดหยุ่นด้วยสถาปัตยกรรม XLR ที่เป็นเอกลักษณ์ ซึ่ง Toolchain ให้ความสามารถไม่เพียงแต่การปรับใช้การออกแบบ RTL เท่านั้น แต่ยังใช้โซลูชัน SoC ที่ซับซ้อนซึ่งปรับใช้โปรเซสเซอร์ซอฟต์คอร์ RISC-V การเริ่มจากซอฟต์คอร์ SoC คือโซลูชัน AI/ML ที่ช่วยให้ปรับใช้การอนุมานของ ML ได้

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.