เหตุผลและวิธีใช้ Efinix FPGA สำหรับ AI/ML Imaging ตอนที่ 2: การจับภาพและการประมวลผล

Contributed By DigiKey's European Editors

2023-05-05

หมายเหตุจากผู้เรียบเรียง: แนวทางใหม่สำหรับสถาปัตยกรรม FPGA ทำให้เกิดการควบคุมที่ละเอียดยิ่งขึ้นและมีความยืดหยุ่นมากขึ้นเพื่อตอบสนองความต้องการของแมชชีนเลิร์นนิ่ง (ML) และปัญญาประดิษฐ์ (AI) ส่วนที่ 1 ของซีรีส์สองตอนนี้จะแนะนำสถาปัตยกรรมดังกล่าวจากอีฟินิกซ์ และวิธีเริ่มต้นใช้งานโดยใช้บอร์ดพัฒนา ส่วนที่ 2 กล่าวถึงการเชื่อมต่อบอร์ดพัฒนากับอุปกรณ์ภายนอกและอุปกรณ์ต่อพ่วง เช่น กล้อง และวิธีการใช้ประโยชน์จาก FPGA เพื่อขจัดปัญหาคอขวดในการประมวลผลภาพ

FPGA มีบทบาทสำคัญในการใช้งานจำนวนมาก ตั้งแต่การควบคุมอุตสาหกรรมและความปลอดภัย ไปจนถึงวิทยาการหุ่นยนต์ การบินและอวกาศ และยานยนต์ ด้วยลักษณะที่ยืดหยุ่นของคอร์ลอจิกที่ตั้งโปรแกรมได้และความสามารถในการเชื่อมต่อที่กว้าง ทำให้กรณีการใช้งานที่เพิ่มขึ้นสำหรับ FPGA อยู่ในการประมวลผลภาพ ซึ่งสามารถนำแมชชีนเลิร์นนิง (ML) ไปใช้งานได้ FPGA เหมาะอย่างยิ่งสำหรับการใช้งานโซลูชันที่มีอินเทอร์เฟซกล้องความเร็วสูงหลายตัวด้วยโครงสร้างลอจิกแบบขนาน นอกจากนี้ FPGA ยังเปิดใช้งานการใช้ไปป์ไลน์การประมวลผลเฉพาะในลอจิก ดังนั้นจึงช่วยขจัดปัญหาคอขวดของทรัพยากรที่ใช้ร่วมกันซึ่งจะเกี่ยวข้องกับโซลูชันที่ใช้ CPU หรือ GPU

รูปลักษณ์ที่สองของ Efinixไทเทเนียม FPGA จะตรวจสอบแอปพลิเคชันการประมวลผลภาพอ้างอิงที่มาพร้อมกับ FPGATi180 M484 คณะกรรมการพัฒนา จุดมุ่งหมายคือเพื่อทำความเข้าใจส่วนประกอบของการออกแบบ และระบุตำแหน่งที่เทคโนโลยี FPGA ช่วยขจัดปัญหาคอขวดหรือให้ประโยชน์อื่นๆ แก่นักพัฒนา

การออกแบบอ้างอิงที่ใช้ Ti180 M484

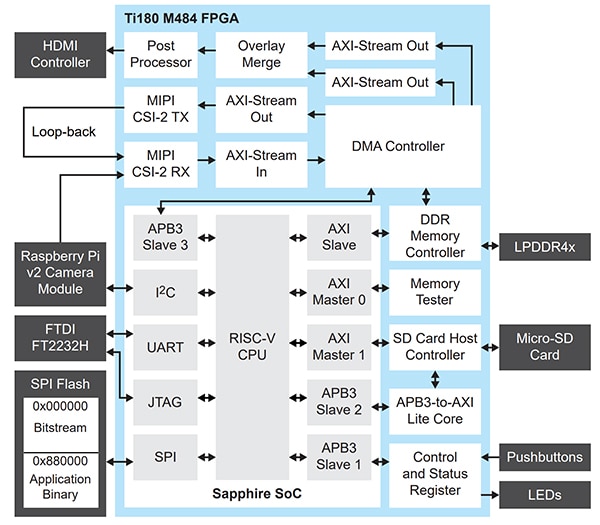

ตามแนวคิดแล้ว การออกแบบอ้างอิง (รูปที่ 1) จะรับภาพจากกล้อง Mobile Industry Processor Interface (MIPI) หลายตัว ดำเนินการเฟรมบัฟเฟอร์ใน LPDDR4x แล้วส่งออกภาพไปยังจอแสดงผล High Definition Multimedia Interface (HDMI) การ์ด FPGA Mezzanine (FMC) และสี่แซมเทคคำพูดคำจา อินเทอร์เฟซบนบอร์ดใช้เพื่อจัดหาอินพุตกล้องและเอาต์พุต HDMI

รูปที่ 1: ตามแนวคิดแล้ว การออกแบบอ้างอิง Ti180 M484 รับภาพจากกล้อง MIPI หลายตัว ทำการเฟรมบัฟเฟอร์ใน LPDDR4x แล้วส่งออกภาพไปยังจอแสดงผล HDMI >(แหล่งรูปภาพ: Efinix)

รูปที่ 1: ตามแนวคิดแล้ว การออกแบบอ้างอิง Ti180 M484 รับภาพจากกล้อง MIPI หลายตัว ทำการเฟรมบัฟเฟอร์ใน LPDDR4x แล้วส่งออกภาพไปยังจอแสดงผล HDMI >(แหล่งรูปภาพ: Efinix)

เดอะเอฟ.เอ็ม.ซี การ์ดขยายไปยัง QSE ใช้ร่วมกับการ์ดลูกสาว HDMI เพื่อให้เส้นทางวิดีโอออก ในขณะที่ตัวเชื่อมต่อ QSE สามตัวใช้เพื่อเชื่อมต่อกับDFRobotSEN0494 กล้อง MIPI หากไม่มีกล้อง MIPI หลายตัว สามารถใช้กล้องตัวเดียวได้โดยการวนกลับช่องกล้องเดียวเพื่อจำลองกล้องเพิ่มเติม

ในระดับสูง แอปพลิเคชันนี้อาจดูตรงไปตรงมา อย่างไรก็ตาม การรับสตรีม MIPI ความละเอียดสูง (HD) หลายรายการที่อัตราเฟรมสูงเป็นสิ่งที่ท้าทาย นี่คือจุดที่เทคโนโลยี FPGA มีประโยชน์ เนื่องจากช่วยให้นักออกแบบสามารถใช้สตรีม MIPI หลายรายการพร้อมกันได้

สถาปัตยกรรมของการออกแบบอ้างอิงใช้ประโยชน์จากโครงสร้างการประมวลผลทั้งแบบขนานและแบบต่อเนื่องด้วย FPGA โครงสร้างคู่ขนานถูกนำมาใช้เพื่อดำเนินการไปป์ไลน์การประมวลผลภาพ ในขณะที่โปรเซสเซอร์ RISC-V ให้การประมวลผลตามลำดับที่ใช้สำหรับตารางการค้นหา FPGA (LUTs)

ไปป์ไลน์การประมวลผลภาพสามารถแบ่งออกเป็นสององค์ประกอบภายในระบบประมวลผลภาพที่ใช้ FPGA จำนวนมาก ได้แก่ สตรีมอินพุตและเอาท์พุต สตรีมอินพุตเชื่อมต่อกับอินเทอร์เฟซของกล้อง/เซ็นเซอร์ และฟังก์ชันการประมวลผลจะถูกนำไปใช้กับเอาต์พุตของเซ็นเซอร์ ฟังก์ชันเหล่านี้อาจรวมถึงการแปลงไบเออร์ ไวต์บาลานซ์อัตโนมัติ และการปรับปรุงอื่นๆ ในเอาต์พุตสตรีม รูปภาพจะถูกเตรียมไว้สำหรับการแสดง ซึ่งรวมถึงการเปลี่ยนปริภูมิสี (เช่น RGB เป็น YUV) และการประมวลผลภายหลังสำหรับรูปแบบเอาต์พุตที่ต้องการ เช่น HDMI

บ่อยครั้งที่ห่วงโซ่การประมวลผลภาพอินพุตทำงานที่อัตราสัญญาณนาฬิกาพิกเซลของเซ็นเซอร์ สิ่งนี้มีจังหวะเวลาที่แตกต่างกันไปยังเชนเอาต์พุต ซึ่งประมวลผลที่ความถี่การแสดงผลเอาต์พุต

เฟรมบัฟเฟอร์ใช้เพื่อเชื่อมต่ออินพุตกับไปป์ไลน์การประมวลผลเอาต์พุต ซึ่งมักจะจัดเก็บไว้ในหน่วยความจำประสิทธิภาพสูงภายนอก เช่น LPDDR4x เฟรมบัฟเฟอร์นี้จะแยกระหว่างไปป์ไลน์อินพุตและเอาท์พุต ทำให้สามารถเข้าถึงเฟรมบัฟเฟอร์ผ่านการเข้าถึงหน่วยความจำโดยตรงที่ความถี่สัญญาณนาฬิกาที่เหมาะสม

การออกแบบอ้างอิง Ti180 ใช้วิธีการที่คล้ายกันกับแนวคิดที่สรุปไว้ข้างต้น ไปป์ไลน์การประมวลผลภาพอินพุตใช้แกนหลักทรัพย์สินทางปัญญา (IP) ของตัวรับสัญญาณ MIPI Camera Serial Interface 2 (CSI-2) ซึ่งสร้างขึ้นบนชั้นทางกายภาพของ MIPI (MIPI D-PHY) - อินพุต/เอาต์พุต (I/O) ที่มีความสามารถ ไทเทเนียม FPGA MIPI เป็นอินเทอร์เฟซที่ท้าทายเพราะใช้ทั้งการส่งสัญญาณแบบปลายเดี่ยวและดิฟเฟอเรนเชียลบนคู่ดิฟเฟอเรนเชียลเดียวกัน นอกเหนือจากการสื่อสารความเร็วต่ำและความเร็วสูง การรวม MIPI D-PHY ภายใน FPGA I/O ช่วยลดความซับซ้อนของการออกแบบการ์ดวงจร ขณะเดียวกันก็ลดรายการวัสดุ (BOM)

เมื่อได้รับสตรีมรูปภาพจากกล้องแล้ว การออกแบบอ้างอิงจะแปลงเอาต์พุตของ MIPI CSI-2 RX เป็นสตรีมอินเทอร์เฟซขั้นสูง eXtensible (AXI) AXI Stream เป็นอินเทอร์เฟซความเร็วสูงแบบทิศทางเดียวที่ให้สตรีมข้อมูลจากมาสเตอร์ไปยังสเลฟ มีสัญญาณการจับมือเพื่อถ่ายโอนระหว่างมาสเตอร์และทาส (tvalid และ tready) พร้อมกับสัญญาณไซด์แบนด์ สัญญาณแถบข้างเหล่านี้สามารถใช้เพื่อถ่ายทอดข้อมูลเวลาของภาพ เช่น จุดเริ่มต้นของเฟรมและจุดสิ้นสุดของเส้น

AXI Stream เหมาะอย่างยิ่งสำหรับแอปพลิเคชันการประมวลผลภาพ และทำให้ Efinix สามารถจัดเตรียมช่วง IP การประมวลผลภาพ ซึ่งสามารถรวมเข้ากับห่วงโซ่การประมวลผลได้อย่างง่ายดายตามที่แอปพลิเคชันต้องการ

หลังจากได้รับ ข้อมูลภาพ MIPI CSI-2 และสัญญาณเวลาจะถูกแปลงเป็น AXI Stream และป้อนเข้าสู่โมดูลการเข้าถึงหน่วยความจำโดยตรง (DMA) ซึ่งเขียนเฟรมภาพไปยัง LPDDR4x และทำหน้าที่เป็นบัฟเฟอร์เฟรม

โมดูล DMA นี้ทำงานภายใต้การควบคุมของคอร์ RISC-V ใน FPGA ภายในระบบ Sapphire บนชิป (SoC) SoC นี้ให้การควบคุม เช่น การหยุดและเริ่มเขียน DMA นอกเหนือจากการให้ข้อมูลที่จำเป็นแก่ช่องเขียน DMA เพื่อเขียนข้อมูลภาพไปยัง LPDDR4x อย่างถูกต้อง ซึ่งรวมถึงข้อมูลเกี่ยวกับตำแหน่งหน่วยความจำและความกว้างและความสูงของภาพที่กำหนดเป็นไบต์

ช่องสัญญาณออกในการออกแบบอ้างอิงอ่านข้อมูลภาพจากเฟรมบัฟเฟอร์ LPDDR4x ภายใต้การควบคุมของ RISC-V SoC ข้อมูลจะถูกส่งออกจาก DMA IP เป็น AXI Stream ซึ่งจะถูกแปลงจากรูปแบบ RAW ที่เซนเซอร์ให้มาในรูปแบบ RGB (รูปที่ 2) และเตรียมพร้อมสำหรับการส่งออกบนออนบอร์ดอุปกรณ์อนาล็อก'ADV7511 เครื่องส่งสัญญาณ HDMI

รูปที่ 2: ภาพตัวอย่างที่ส่งออกจากการออกแบบอ้างอิง (แหล่งที่มาภาพ: Adam Taylor)

รูปที่ 2: ภาพตัวอย่างที่ส่งออกจากการออกแบบอ้างอิง (แหล่งที่มาภาพ: Adam Taylor)

การใช้ DMA ยังช่วยให้ Sapphire SoC RISC-V สามารถเข้าถึงภาพที่จัดเก็บไว้ในเฟรมบัฟเฟอร์ รวมถึงสถิติเชิงนามธรรมและข้อมูลภาพ Sapphire SoC ยังสามารถเขียนโอเวอร์เลย์ลงใน LPDDR4x เพื่อให้สามารถรวมเข้ากับเอาต์พุตวิดีโอสตรีมได้

เซ็นเซอร์รับภาพ CMOS สมัยใหม่ (CIS) มีโหมดการทำงานหลายโหมด และสามารถกำหนดค่าให้มีการประมวลผลบนชิป และรูปแบบเอาต์พุตและรูปแบบการตอกบัตรที่แตกต่างกันหลายแบบ การกำหนดค่านี้มีให้ตามปกติผ่านอินเทอร์เฟซ I²C ในการออกแบบอ้างอิงของ Efinix การสื่อสาร I²C นี้กับกล้อง MIPI มีให้โดยโปรเซสเซอร์ Sapphire SoC RISC-V

การรวมโปรเซสเซอร์ RISC-V ภายใน Titanium FPGA ช่วยลดขนาดโดยรวมของโซลูชันขั้นสุดท้าย เนื่องจากไม่จำเป็นต้องติดตั้งทั้งเครื่องสถานะ FPGA ที่ซับซ้อนซึ่งเพิ่มความเสี่ยงในการออกแบบ เช่นเดียวกับโปรเซสเซอร์ภายนอกที่เพิ่มลงใน BOM

การรวมโปรเซสเซอร์ยังรองรับ IP เพิ่มเติมเพื่อสื่อสารกับการ์ด MicroSD สิ่งนี้เปิดใช้งานแอปพลิเคชันในโลกแห่งความเป็นจริงซึ่งอาจต้องจัดเก็บรูปภาพสำหรับการวิเคราะห์ในภายหลัง

โดยรวมแล้ว สถาปัตยกรรมของการออกแบบอ้างอิง Ti180 ได้รับการปรับแต่งเพื่อให้เป็นโซลูชันที่มีขนาดกะทัดรัด ต้นทุนต่ำ แต่มีประสิทธิภาพสูง ซึ่งช่วยให้นักพัฒนาสามารถลดต้นทุน BOM ผ่านการรวมระบบ

ประโยชน์หลักประการหนึ่งของการออกแบบอ้างอิงคือสามารถใช้เพื่อเริ่มต้นการพัฒนาแอปพลิเคชันบนฮาร์ดแวร์แบบกำหนดเอง ทำให้นักพัฒนาสามารถใช้องค์ประกอบที่สำคัญของการออกแบบและต่อยอดด้วยการปรับแต่งที่จำเป็น ซึ่งรวมถึงความสามารถในการใช้โฟลว์ TinyML ของ Efinix เพื่อนำแอปพลิเคชัน TinyML ที่อิงตามการมองเห็นมาใช้ซึ่งทำงานบน FPGA สิ่งนี้สามารถใช้ประโยชน์จากธรรมชาติแบบขนานของลอจิก FPGA และความสามารถในการเพิ่มคำสั่งที่กำหนดเองลงในโปรเซสเซอร์ RISC-V ได้อย่างง่ายดาย ทำให้สามารถสร้างตัวเร่งความเร็วภายในลอจิก FPGA

การดำเนินการ

ตามที่กล่าวไว้ในส่วนที่ 1 สถาปัตยกรรม Efinix มีลักษณะเฉพาะตรงที่ใช้เซลล์ eXchangeable Logic and Routing (XLR) เพื่อจัดเตรียมทั้งฟังก์ชันการกำหนดเส้นทางและลอจิก ระบบวิดีโอ เช่น การออกแบบอ้างอิงเป็นแบบผสมที่มีทั้งลอจิกและการจัดเส้นทางที่หนักหน่วง: ต้องใช้ลอจิกที่กว้างขวางเพื่อใช้คุณสมบัติการประมวลผลภาพ และการกำหนดเส้นทางที่กว้างขวางเป็นสิ่งจำเป็นเพื่อเชื่อมต่อเซลล์ IP ที่ความถี่ที่ต้องการ

การออกแบบอ้างอิงใช้ประมาณ 42% ของเซลล์ XLR ภายในอุปกรณ์ เหลือพื้นที่เพียงพอสำหรับการเพิ่ม รวมถึงแอปพลิเคชันแบบกำหนดเอง เช่น edge ML

การใช้บล็อก RAM และบล็อกการประมวลผลสัญญาณดิจิทัล (DSP) ยังมีประสิทธิภาพมาก โดยใช้บล็อก DSP เพียง 4 จาก 640 บล็อก และ 40% ของบล็อกหน่วยความจำ (รูปที่ 3)

|

รูปที่ 3: การจัดสรรทรัพยากรบนสถาปัตยกรรม Efinix แสดงเพียง 42% ของเซลล์ XLR ที่ใช้งาน ทำให้เหลือพื้นที่เพียงพอสำหรับกระบวนการเพิ่มเติม (แหล่งรูปภาพ: อดัม เทย์เลอร์)

ที่อุปกรณ์ IO อินเทอร์เฟซ DDR สำหรับ LPDDR4x ใช้เพื่อจัดหาหน่วยความจำแอปพลิเคชันสำหรับ Sapphire SoC และบัฟเฟอร์เฟรมภาพ ทรัพยากร MIPI เฉพาะอุปกรณ์ทั้งหมดจะถูกใช้พร้อมกับ 50% ของเฟสล็อคลูป (รูปที่ 4)

|

รูปที่ 4: ภาพรวมของอินเทอร์เฟซและทรัพยากร I/O ที่ใช้ (แหล่งรูปภาพ: อดัม เทย์เลอร์)

I/O วัตถุประสงค์ทั่วไป (GPIO) ใช้เพื่อจัดเตรียมการสื่อสาร I²C พร้อมกับอินเทอร์เฟซต่างๆ ที่เชื่อมต่อกับ Sapphire SoC รวมถึง NOR FLASH, USB UART และการ์ด SD HSIO ใช้เพื่อส่งสัญญาณวิดีโอความเร็วสูงไปยังเครื่องส่งสัญญาณ HDMI ADC7511

องค์ประกอบสำคัญประการหนึ่งเมื่อออกแบบด้วย FPGA ไม่ใช่แค่การนำไปใช้และเหมาะสมกับการออกแบบภายใน FPGA เท่านั้น แต่ยังสามารถวางการออกแบบลอจิกภายใน FPGA และบรรลุประสิทธิภาพด้านเวลาที่ต้องการเมื่อกำหนดเส้นทาง

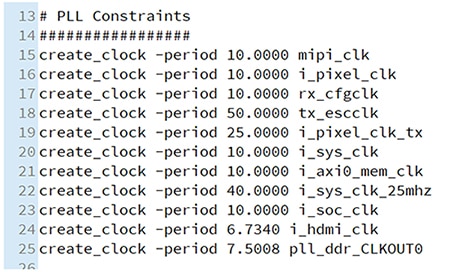

หมดยุคของการออกแบบ FPGA แบบโดเมนนาฬิกาเดียวไปนานแล้ว มีนาฬิกาหลายตัวที่แตกต่างกัน ทั้งหมดทำงานที่ความถี่สูงในการออกแบบอ้างอิง Ti180 ตารางเวลาสุดท้ายแสดงความถี่สูงสุดที่ทำได้สำหรับนาฬิกาภายในระบบ นี่คือจุดที่ประสิทธิภาพการกำหนดเวลาที่ร้องขอสามารถดูได้ในข้อจำกัด (รูปที่ 5) ซึ่งมีความถี่สัญญาณนาฬิกาสูงสุด 148.5 เมกะเฮิรตซ์ (MHz) สำหรับสัญญาณนาฬิกาเอาต์พุต HDMI

รูปที่ 5: ข้อจำกัดด้านนาฬิกาสำหรับการออกแบบอ้างอิง (แหล่งที่มาภาพ: Adam Taylor)

รูปที่ 5: ข้อจำกัดด้านนาฬิกาสำหรับการออกแบบอ้างอิง (แหล่งที่มาภาพ: Adam Taylor)

การดำเนินการตามเวลาเทียบกับข้อจำกัดแสดงให้เห็นถึงศักยภาพของโครงสร้าง Titanium FPGA XLR เนื่องจากช่วยลดความล่าช้าในการกำหนดเส้นทางที่เป็นไปได้ ซึ่งจะเป็นการเพิ่มประสิทธิภาพการออกแบบ (รูปที่ 6)

|

รูปที่ 6: การจับเวลาเทียบกับข้อจำกัดแสดงให้เห็นศักยภาพของโครงสร้าง Titanium FPGA XLR เพื่อลดความล่าช้าในการกำหนดเส้นทางที่เป็นไปได้ ซึ่งจะเป็นการเพิ่มประสิทธิภาพการออกแบบ (แหล่งรูปภาพ: อดัม เทย์เลอร์)

สรุป

การออกแบบอ้างอิง Ti180 M484 แสดงความสามารถของ Efinix FPGA และ Ti180 โดยเฉพาะอย่างชัดเจน การออกแบบนี้ใช้ประโยชน์จากโครงสร้าง I/O ที่ไม่ซ้ำกันหลายโครงสร้างเพื่อใช้เส้นทางการประมวลผลภาพที่ซับซ้อนซึ่งรองรับสตรีม MIPI ขาเข้าหลายรายการ ระบบประมวลผลภาพนี้ทำงานภายใต้การควบคุมของซอฟต์คอร์ Sapphire SoC ซึ่งใช้องค์ประกอบการประมวลผลตามลำดับที่จำเป็นของแอปพลิเคชัน

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.