ตอบสนองความต้องการด้านฟังก์ชันและความปลอดภัยที่หลากหลายด้วยโปรเซสเซอร์แบบมัลติคอร์

Contributed By DigiKey's North American Editors

2020-10-01

ยานยนต์อุตสาหกรรมหุ่นยนต์ การควบคุมอาคารและแอพพลิเคชั่นระบบฝังตัวที่สำคัญอื่น ๆ คาดว่าจะรับภาระงานที่หลากหลายมากขึ้นซึ่งครอบคลุมตั้งแต่การตรวจสอบแบบเรียลไทม์ที่ใช้พลังงานต่ำไปจนถึงแอปพลิเคชันมัลติมีเดียระดับสูงที่มีการแสดงกราฟิกแบบหลายหน้าจอสำหรับอินเทอร์เฟซสำหรับมนุษย์กับเครื่องจักร (HMI) ในขณะที่เป็นไปตามข้อกำหนดด้านการทำงานที่กว้างเหล่านี้พวกเขายังต้องสามารถรองรับมาตรฐานด้านความปลอดภัยที่เข้มงวด ลดต้นทุนและฟุตปริ๊นต์ และปรับสมดุลพลังงาน/ประสิทธิภาพให้เหมาะสม

เพื่อให้เป็นไปตามข้อกำหนดที่ขัดแย้งกันบ่อยครั้งเหล่านี้นักพัฒนาต้องถูกบังคับให้สละความสามารถในการใช้งานหรือออกแบบและผลิตที่ซับซ้อนด้วยอุปกรณ์เพิ่มเติมที่จำเป็นเพื่อรองรับข้อกำหนดเฉพาะสำหรับกราฟิก ความปลอดภัยและความปลอดภัยเป็นต้น สิ่งที่นักพัฒนาต้องการจริง ๆ คือโซลูชันเดียวที่สามารถรองรับผลิตภัณฑ์หลากหลายประเภทที่ตรงตามข้อกำหนดเหล่านี้ในแอปพลิเคชันระบบฝังตัวที่สำคัญหลากหลายประเภท

บทความนี้อธิบายถึงวิวัฒนาการของการออกแบบระบบฝังตัวที่สำคัญอย่างรวดเร็ว จากนั้นจะแสดงให้เห็นว่าโปรเซสเซอร์แอปพลิเคชันแบบมัลติคอร์ - ออกแบบมาเป็นพิเศษโดย NXP Semiconductors เพื่อรองรับรายการข้อกำหนดที่ขยายตัวอย่างรวดเร็วสำหรับทั้งฟังก์ชันการทำงานกว้าง ๆ และความสามารถที่รับรองด้านความปลอดภัยสามารถใช้เพื่อจัดการกับความท้าทายของนักพัฒนา

วิวัฒนาการของข้อควรพิจารณาในการออกแบบระบบฝังตัว

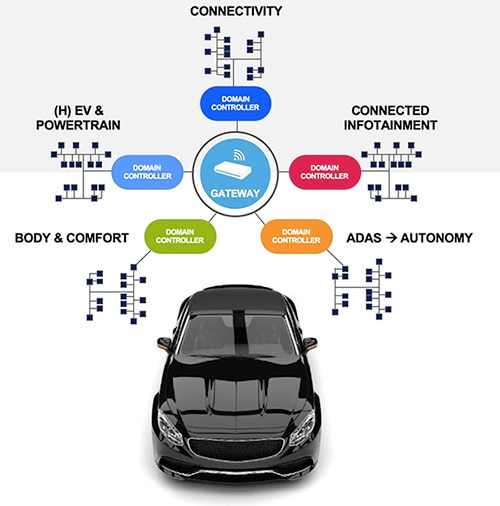

บทบาทดั้งเดิมของอุปกรณ์ฝังตัวในการสนับสนุนชุดฟังก์ชันระบบที่จำกัดส่วนใหญ่ถูกแทนที่ด้วยความต้องการอุปกรณ์ที่ให้ความสามารถในวงกว้าง ตัวอย่างเช่นในงานอุตสาหกรรม ความต้องการความสามารถ HMI ที่เพิ่มขึ้นในเครื่องมือและอุปกรณ์อัจฉริยะเรียกร้องให้โปรเซสเซอร์ที่สามารถส่งมอบกราฟิกที่เหมาะสมที่สุดในขณะที่ตอบสนองความต้องการแบบเรียลไทม์ของอุตสาหกรรม ในทำนองเดียวกันแนวโน้มในการใช้งานยานยนต์ที่มีต่อสถาปัตยกรรมแบบลำดับชั้นซึ่งประกอบด้วยคลัสเตอร์โดเมนที่ใช้งานได้และเกตเวย์ทำให้เกิดความต้องการโปรเซสเซอร์ที่สามารถตอบสนองความต้องการเหล่านั้นได้อย่างเต็มที่ (รูปที่ 1)

รูปที่ 1: แนวโน้มของสถาปัตยกรรมระบบยานยนต์ที่มีลำดับชั้นมากขึ้นทำให้เกิดความต้องการโซลูชันโปรเซสเซอร์แบบบูรณาการและปรับขนาดได้มากขึ้น (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

รูปที่ 1: แนวโน้มของสถาปัตยกรรมระบบยานยนต์ที่มีลำดับชั้นมากขึ้นทำให้เกิดความต้องการโซลูชันโปรเซสเซอร์แบบบูรณาการและปรับขนาดได้มากขึ้น (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

ภายในแต่ละโดเมนที่ใช้งานได้ความต้องการความสามารถที่ซับซ้อนมากขึ้นยังคงเพิ่มขีดจำกัด สำหรับประสิทธิภาพและความสามารถแบบบูรณาการ ตัวอย่างเช่นการเกิดขึ้นของจอแสดงผลแบบ Head-up ต้องการโซลูชันที่สามารถให้ข้อมูลกราฟิกที่สำคัญแก่ผู้ขับขี่ได้อย่างต่อเนื่อง นอกเหนือจากจอแสดงผลรุ่นใหม่เหล่านี้ความต้องการที่เพิ่มขึ้นสำหรับการรับรู้ของผู้ขับขี่ยังเพิ่มข้อกำหนดเพิ่มเติมสำหรับอินเทอร์เฟซของกล้องและการใช้งานซอฟต์แวร์การจดจำขั้นสูงที่มีประสิทธิภาพสูงซึ่งสามารถตรวจจับอาการง่วงนอนได้

ในขณะที่แอปพลิเคชันมีการพัฒนาอย่างต่อเนื่องความต้องการโซลูชันแบบบูรณาการที่ปรับขนาดได้จึงเป็นเรื่องเร่งด่วนมากขึ้นเพื่อตอบสนองความต้องการที่หลากหลายมากขึ้นในขณะที่ลดขนาดการออกแบบต้นทุนและความซับซ้อนให้น้อยที่สุด การใช้ NXP's i.MX 8 แฟมิลี่ของโปรเซสเซอร์แอพพลิเคชั่น นักพัฒนาสามารถใช้ประโยชน์จากแพลตฟอร์มที่เข้ากันได้ของโปรเซสเซอร์ที่มีความสามารถและประสิทธิภาพที่หลากหลายเพื่อรองรับความต้องการของแอพพลิเคชั่นที่หลากหลาย ภายใน i.MX 8 family, the NXP i.MX 8X ซีรีส์ตอบสนองความต้องการที่เกิดขึ้นใหม่สำหรับโปรเซสเซอร์ที่ได้รับการรับรองด้านความปลอดภัยซึ่งมีความจำเป็นในอุตสาหกรรมยานยนต์ระดับกลางและการใช้งานในอุตสาหกรรม

สถาปัตยกรรมหลายคอร์จัดการกับปริมาณงานที่หลากหลาย

ความยากลำบากอย่างหนึ่งที่นักพัฒนาต้องเผชิญในการนำอุปกรณ์มาใช้สำหรับยานยนต์และงานอุตสาหกรรมคือความต้องการที่กว้างมากขึ้น ในกรณีที่นักพัฒนาสามารถคาดหวังว่าจะจัดการกับภาระงานการประมวลผลแอปพลิเคชันระดับสูงแบบเรียลไทม์หรือระดับสูงความต้องการระบบย่อยอัจฉริยะได้รวมการประมวลผลประเภทต่าง ๆ เหล่านี้เข้าด้วยกันอย่างมีนัยสำคัญ นักพัฒนาต้องการโซลูชันที่สามารถให้ทั้งการตอบสนองแบบเรียลไทม์ที่เชื่อถือได้และการเรียกใช้แอปพลิเคชันประสิทธิภาพสูงในขณะที่รองรับข้อกำหนดด้านความปลอดภัยในการทำงาน

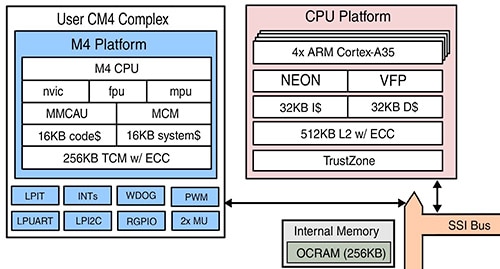

ออกแบบมาเพื่อมอบความสามารถแบบเรียลไทม์การประมวลผลประสิทธิภาพสูงและการใช้พลังงานต่ำโปรเซสเซอร์ NXP i.MX 8X series ใช้ประโยชน์อย่างเต็มที่จากสถาปัตยกรรมหน่วยประมวลผลกลาง (CPU) แบบมัลติคอร์ที่ซับซ้อนเพื่อจัดการปริมาณงานคำนวณที่หลากหลาย (รูปที่ 2)

รูปที่ 2: NXP i.MX 8X series ใช้สถาปัตยกรรมแบบมัลติคอร์ ซึ่งประกอบ Arm โปรเซสเซอร์แบบฝัง Cortex-M4 (CM4) และโปรเซสเซอร์แอพพลิเคชั่น Arm Cortex-A35 หลายตัวเพื่อรองรับปริมาณงานซอฟต์แวร์แบบผสม (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

รูปที่ 2: NXP i.MX 8X series ใช้สถาปัตยกรรมแบบมัลติคอร์ ซึ่งประกอบ Arm โปรเซสเซอร์แบบฝัง Cortex-M4 (CM4) และโปรเซสเซอร์แอพพลิเคชั่น Arm Cortex-A35 หลายตัวเพื่อรองรับปริมาณงานซอฟต์แวร์แบบผสม (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

สำหรับงานประมวลผลแบบเรียลไทม์ทั่วไปอุปกรณ์ i.MX 8X ประกอบด้วยโปรเซสเซอร์ Arm Cortex-M4 (CM4) พร้อมหน่วยจุดลอยตัว (FPU) หน่วยป้องกันหน่วยความจำ (MPU) หน่วยเร่งความเร็วการเข้ารหัสที่แมปหน่วยความจำ (MMCAU) และ โมดูลควบคุมเบ็ดเตล็ด (MCM) เพื่อรองรับอุปกรณ์ต่อพ่วงภายนอกเช่นเซ็นเซอร์และแอคชูเอเตอร์คอมเพล็กซ์ CM4 ของผู้ใช้นี้ได้รวมตัวควบคุมการขัดจังหวะเวกเตอร์ (NVIC) แบบซ้อนเข้ากับชุดอินเทอร์เฟซและโมดูลที่ครอบคลุมรวมถึงตัวจับเวลาการขัดจังหวะเป็นระยะพลังงานต่ำ (LPIT) การมอดูเลตความกว้างพัลส์ (PWM) และ ฟังก์ชันอื่น ๆ ที่จำเป็นโดยทั่วไปในการใช้งานยานยนต์และอุตสาหกรรม คู่ของหน่วยความจำแคชและหน่วยความจำคู่อย่างแน่นหนา (TCM) พร้อมความสามารถในการแก้ไขข้อผิดพลาด (ECC) ช่วยลดการเข้าถึงหน่วยความจำภายนอกการประมวลผลความเร็วและจัดการกับข้อผิดพลาดของหน่วยความจำ

สำหรับการเรียกใช้ปริมาณงานแอปพลิเคชันอย่างรวดเร็ว แพลตฟอร์ม CPU ประกอบด้วยตัวประมวลผลแอปพลิเคชัน Arm Cortex-A35 ที่ประหยัดพลังงานหลายตัว - AP สองตัวในโปรเซสเซอร์ 8DualXPlus เช่น MIMX8UX6AVLFZACและ AP สี่ตัวในโปรเซสเซอร์ 8QuadXPlus เช่น MIMX8QX6AVLFZAC นอกเหนือจากคำสั่งเฉพาะ (I$) และแคชข้อมูล (D$) แล้วแพลตฟอร์ม CPU ยังมีแคช 512 กิโลไบต์ (Kbyte) ระดับ 2 (L2) ที่ใช้ร่วมกันกับ ECC

คอร์ Arm Cortex-A35 ของสถาปัตยกรรมให้ทั้งความเข้ากันได้ของซอฟต์แวร์และความสามารถในการปรับขยายประสิทธิภาพโดยรองรับทั้งความเข้ากันได้แบบย้อนหลัง 32 บิตและประสิทธิภาพ 64 บิต เพื่อเพิ่มความเร็วในการเรียกใช้อัลกอริธึมที่เน้นการประมวลผลเช่นการประมวลผลสัญญาณและการเรียนรู้ของเครื่องโปรเซสเซอร์ Arm Cortex-A35 ให้การประมวลผลจุดลอยตัวเวกเตอร์ (VFP) และส่วนขยายสถาปัตยกรรมข้อมูลหลายข้อมูล (SIMD) Neon single instruction ของ Arm เพื่อเร่งการทำงานของซอฟต์แวร์สำหรับการประมวลผลภาพการมองเห็นของคอมพิวเตอร์และการเรียนรู้ของเครื่อง Arm Compute Library นำเสนอฟังก์ชั่นที่ปรับให้เหมาะกับสถาปัตยกรรมของโปรเซสเซอร์ Arm และหน่วยประมวลผลกราฟิก (GPU) และโอเพ่นซอร์ส Ne10 ไลบรารี C มีฟังก์ชันที่ปรับให้เหมาะสมกับแขนสำหรับการดำเนินการที่ต้องใช้การประมวลผล

เครื่องยนต์เฉพาะจะลดการโหลดซีพียูหลัก

นอกจากผู้ใช้ CM4 complex และแพลตฟอร์มซีพียูแบบมัลติคอร์ Arm Cortex-A35 แล้วสถาปัตยกรรมยังมีเอ็นจิ้นเฉพาะเพิ่มเติมสำหรับแอปพลิเคชันมัลติมีเดีย นอกเหนือจากตัวประมวลผลสัญญาณดิจิทัล (DSP) สำหรับการประมวลผลตัวแปลงสัญญาณเสียงและเสียงแล้วสถาปัตยกรรมยังรวมทั้ง GPU และหน่วยประมวลผลวิดีโอ (VPU) GPU ของอุปกรณ์รองรับไลบรารีกราฟิกมาตรฐานเร่งการดำเนินการโดยใช้เวกเตอร์จุดลอยตัวสี่องค์ประกอบสี่ส่วนแยกกัน (vec4) พร้อมหน่วยประมวลผล 16 หน่วยและเอ็นจิ้น blit บิตประสิทธิภาพสูงสองมิติ VPU จัดการรูปแบบวิดีโอยอดนิยมเร่งการถอดรหัสสูงสุด 4Kp30 (โปรเกรสซีฟ 30 Hz) และเข้ารหัสสูงสุด 1080p30 ในทางกลับกันบล็อกคอนโทรลเลอร์การแสดงผลเฉพาะของชิปสามารถขับเคลื่อนเอาต์พุตกราฟิกไปยังจอแสดงผลแยกกันได้มากถึงสามจอ

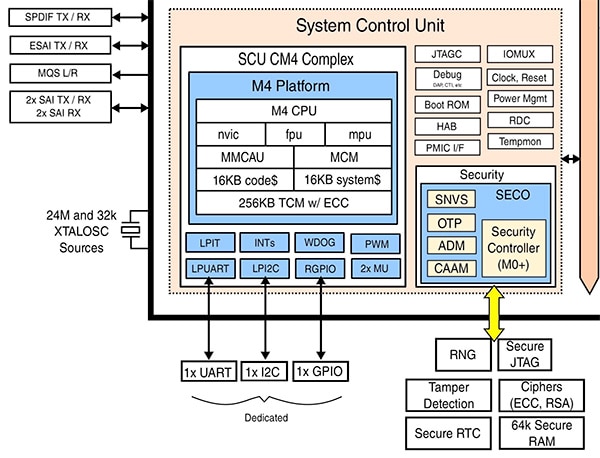

เพื่อเพิ่มประสิทธิภาพสูงสุดสถาปัตยกรรม i.MX 8X ยังรวมแกนประมวลผลเพิ่มเติมที่ออกแบบมาเพื่อปลดปล่อยแพลตฟอร์ม CPU หลักจากภาระการประมวลผลเพิ่มเติมที่มักเกิดขึ้นในการดำเนินการจัดการระบบและบริการความปลอดภัย สำหรับการจัดการระบบหน่วยควบคุมระบบของสถาปัตยกรรม (SCU) จะรวมคอมเพล็กซ์ CM4 ที่ตรงกับคอมเพล็กซ์ CM4 ของผู้ใช้ แต่ยังคงทุ่มเทให้กับการดำเนินการ SCU อย่างสมบูรณ์และไม่สามารถใช้งานได้โดยนักพัฒนา (รูปที่ 3)

รูปที่ 3: ภายในตัวประมวลผล NXP i.MX 8X แบบรวมลึกและไม่พร้อมใช้งานสำหรับนักพัฒนา SCU ใช้ระบบย่อย Arm Cortex-M4 (CM4) เฉพาะเพื่อยกเลิกการโหลดงานการจัดการระบบจากโปรเซสเซอร์หลักของอุปกรณ์ (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

รูปที่ 3: ภายในตัวประมวลผล NXP i.MX 8X แบบรวมลึกและไม่พร้อมใช้งานสำหรับนักพัฒนา SCU ใช้ระบบย่อย Arm Cortex-M4 (CM4) เฉพาะเพื่อยกเลิกการโหลดงานการจัดการระบบจากโปรเซสเซอร์หลักของอุปกรณ์ (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

นอกเหนือจากการจัดการพลังงานการตอกบัตรและฟังก์ชันภายในอื่น ๆ แล้ว SCU ยังควบคุมความแรงของช่องสัญญาณมัลติเพล็กซ์พินและอินพุต/เอาท์พุต (I/O) ในการทำงานปกติ ในความเป็นจริงผู้ใช้ CM4 complex และ Arm Cortex-A35 APs ไม่สามารถเข้าถึงความสามารถของฮาร์ดแวร์ระดับต่ำต่าง ๆ เหล่านี้ได้โดยตรง แต่ SCU ทำหน้าที่แยกความสามารถเหล่านี้ออกไปดังนั้นซอฟต์แวร์ที่ทำงานบน CM4 หรือ AP ของผู้ใช้จึงจำเป็นต้องเรียกใช้ฟังก์ชัน SCU firmware application programming interface (API) เพื่อทำหน้าที่ต่าง ๆ เช่นการปิดโดเมนพลังงานที่ไม่จำเป็น ตัวอย่างเช่นหากโดเมนพลังงานนั้นถูกแชร์กับโปรเซสเซอร์อื่น SCU ก็เพียงแค่รับทราบคำขอปิดเครื่อง แต่จะยังคงขับเคลื่อนโดเมนจนกว่าโปรเซสเซอร์อื่นจะออกคำขอปิดเครื่องเช่นกัน

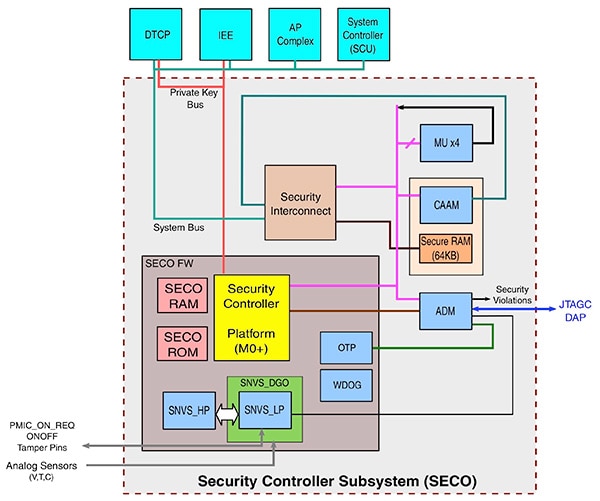

ในการจัดการการสนับสนุนด้านความปลอดภัยที่ครอบคลุมของอุปกรณ์ i.MX 8X โปรเซสเซอร์เฉพาะอีกตัวจะเข้ามามีบทบาทในระบบย่อยตัวควบคุมความปลอดภัย (SECO) ของอุปกรณ์ ภายในระบบย่อย SECO โปรเซสเซอร์ Arm Cortex-M0 + ที่ใช้พลังงานต่ำในตัวจะรันเฟิร์มแวร์ที่รองรับความสามารถในการรักษาความปลอดภัยบนฮาร์ดแวร์ รวมถึงการเข้าถึงบัสส่วนตัวสำหรับคีย์ที่ปลอดภัยหน่วยความจำที่ตั้งโปรแกรมได้ครั้งเดียว (OTP) สำหรับการจัดเก็บคีย์ที่ปลอดภัยและรักษาความปลอดภัยที่ไม่ หน่วยเก็บข้อมูลแบบระเหย (SNVS) สำหรับข้อมูลส่วนตัวเพิ่มเติมหรือคีย์ชั่วคราว (รูปที่ 4)

รูปที่ 4: ภายในระบบย่อย NXP i.MX 8X security controller (SECO) โปรเซสเซอร์ Arm Cortex-M0 + ที่ใช้พลังงานต่ำโดยเฉพาะจะจัดการการดำเนินการด้านความปลอดภัยวาดบนบัสคีย์ส่วนตัวและโมดูลฮาร์ดแวร์หลายตัวเพื่อการจัดเก็บที่ปลอดภัยการเร่งการเข้ารหัสและการเข้าถึงการดีบักที่พิสูจน์ตัวตน (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

รูปที่ 4: ภายในระบบย่อย NXP i.MX 8X security controller (SECO) โปรเซสเซอร์ Arm Cortex-M0 + ที่ใช้พลังงานต่ำโดยเฉพาะจะจัดการการดำเนินการด้านความปลอดภัยวาดบนบัสคีย์ส่วนตัวและโมดูลฮาร์ดแวร์หลายตัวเพื่อการจัดเก็บที่ปลอดภัยการเร่งการเข้ารหัสและการเข้าถึงการดีบักที่พิสูจน์ตัวตน (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

นอกเหนือจากกลไกการรักษาความปลอดภัยหลักเหล่านี้แล้วระบบย่อย SECO จะประสานการดำเนินการด้านความปลอดภัยสำหรับการตรวจจับการงัดแงะและการแก้จุดบกพร่องที่ปลอดภัยซึ่งเป็นสื่อกลางผ่าน Authenticated Debug Module (ADM) สำหรับการดำเนินการที่ปลอดภัยโมดูลการรักษาความปลอดภัยฮาร์ดแวร์ Cryptographic Acceleration and Assurance Module (CAAM) ในตัวรองรับอัลกอริธึมการรักษาความปลอดภัยเต็มรูปแบบซึ่งรวมถึงการเข้ารหัสแบบสมมาตรและไม่สมมาตรฟังก์ชันแฮชและตัวสร้างตัวเลขสุ่ม (RNG)

ในการทำงานปกติหน่วยประมวลผลอุปกรณ์ซึ่งรวมถึงตัวเร่งความเร็ว SCU, AP และ Digital Transport Content Protection (DTCP) จะใช้การเชื่อมต่อระหว่าง SECO เพื่อเข้าถึงฟังก์ชัน CAAM ผ่านบัสระบบ นอกเหนือจากการเข้าถึงผ่านฟังก์ชัน CAAM direct memory access (DMA) แล้วโปรเซสเซอร์ Cortex-M0 + เฉพาะของ SECO จะไม่สามารถเข้าถึงบัสระบบได้ แต่จะใช้การเชื่อมต่อภายในที่มีการป้องกันเพื่อเข้าถึงอุปกรณ์ต่อพ่วงหน่วยความจำเข้าถึงโดยสุ่มที่ปลอดภัย (RAM) และหน่วยความจำแบบอ่านอย่างเดียว (ROM) และบัสคีย์ส่วนตัวพิเศษแทน

นอกเหนือจากการใช้ตัวเร่งความเร็ว DTCP แล้วไพรเวตคีย์บัสนี้ยังมีบทบาทสำคัญในการสนับสนุนโปรเซสเซอร์ i.MX 8X สำหรับการเข้ารหัสและถอดรหัสแบบ on-the-fly ที่นี่ตัวประมวลผลความปลอดภัยใช้ทรัพยากรเพื่อจัดหาคีย์ส่วนตัวที่จำเป็นสำหรับโมดูล Inline Encryption/Decryption Engine (IEE) ของอุปกรณ์เนื่องจากอ่านหรือเขียนไปยังที่เก็บข้อมูลที่เข้ารหัสอย่างปลอดภัยโดยไม่ต้องเกี่ยวข้องกับโปรเซสเซอร์ที่ร้องขอคอนโทรลเลอร์ DMA หรือ I/O อุปกรณ์

ด้วยเทคโนโลยี TrustZone ของ Arm ที่รวมอยู่ในโปรเซสเซอร์ Cortex-A35 ของอุปกรณ์ระบบย่อย SECO ยังทำงานร่วมกับ SCU ในระหว่างกระบวนการบูตที่ปลอดภัย ในกระบวนการนี้ SCU จะตีความการตั้งค่าการบูตกำหนดค่าแหล่งที่มาสำหรับการบูตและโหลดอิมเมจสำหรับบูตไปยังหน่วยความจำภายในหรือภายนอก ในทางกลับกันระบบย่อย SECO จะใช้ฟังก์ชันการเข้ารหัสเพื่อตรวจสอบความถูกต้องของอิมเมจเฟิร์มแวร์ที่มีการเซ็นชื่อหลังจากโหลดแล้ว แต่ก่อนที่จะดำเนินการ

การปกป้องจอแสดงผลที่สำคัญและควบคุมฟังก์ชันการทำงาน

ในขณะที่ความสามารถในการประมวลผลปริมาณงานที่หลากหลายอย่างมีประสิทธิภาพและปลอดภัยเป็นสิ่งสำคัญสำหรับการใช้งานที่มีความสำคัญต่อภารกิจเช่นในกลุ่มยานยนต์และอุตสาหกรรมความสามารถในการปกป้องความสามารถหลักก็มีความสำคัญไม่แพ้กัน ตระกูล i.MX 8X ของ NXP รวมความสามารถในการประมวลผลเข้ากับความสามารถในการรับรองความปลอดภัยที่จำเป็นเพื่อให้เป็นไปตามข้อกำหนดที่สำคัญเหล่านี้

การสนับสนุนด้านความปลอดภัยของตระกูลโปรเซสเซอร์ถูกสร้างขึ้นในหลายระดับโดยเริ่มจากการผลิตในเทคโนโลยีกระบวนการผลิตซิลิกอนที่ใช้ฉนวน (FD-SOI) ที่ใช้ซิลิกอนจนหมดซึ่งช่วยเพิ่มความเชื่อถือได้ เนื่องจากความปลอดภัยของระบบขึ้นอยู่กับพื้นฐานด้านความปลอดภัยที่แข็งแกร่งการรวมกันของ AP ที่เปิดใช้งาน TrustZone ระบบย่อย SECO และความสามารถในการบูตที่ปลอดภัยสามารถจัดเตรียมสภาพแวดล้อมที่เชื่อถือได้ซึ่งจำเป็นต่อการป้องกันภัยคุกคามด้านความปลอดภัยและความปลอดภัย

ในขณะเดียวกันความสามารถในการจัดการงานสำคัญด้านเวลาอย่างอิสระด้วย CM4 ที่ซับซ้อนของผู้ใช้และการถ่ายโอนงานระบบที่สำคัญไปยังระบบย่อย SCU และ SECO ช่วยให้มั่นใจได้ว่าความสามารถของแอปพลิเคชันภารกิจที่สำคัญยังคงพร้อมใช้งานแม้จะมีภาระการประมวลผลที่แตกต่างกัน ในความเป็นจริง NXP ขยายแนวคิดนี้เพื่อรองรับการแสดงผลภารกิจที่สำคัญผ่านเทคโนโลยี SafeAssure ของ บริษัท ซึ่งรวมเส้นทางความล้มเหลวในการแสดงฮาร์ดแวร์ระดับ B (ASIL B) ที่พร้อมใช้งานด้านความปลอดภัยของยานยนต์ในอุปกรณ์ i.MX 8X ด้วย SafeAssure ผู้ใช้จะได้รับภาพเฟลโอเวอร์โดยอัตโนมัติหากอุปกรณ์ตรวจพบความสมบูรณ์ของข้อมูลหรือข้อผิดพลาดของ GPU การทำงานในพื้นหลังภาพเฟลโอเวอร์นี้ช่วยให้มั่นใจได้ว่าข้อมูลสำคัญยังคงพร้อมใช้งานแม้ในระหว่างการแสดงผลหลักล้มเหลว

การสนับสนุนแอพพลิเคชั่นด้านความปลอดภัยขยายไปถึงการเข้าถึงหน่วยความจำในระบบที่ใช้ i.MX 8X ในบรรดาอินเทอร์เฟซหน่วยความจำที่รองรับอุปกรณ์ i.MX 8X มี 8-bit ECC สำหรับหน่วยความจำ Double Data Rate 3 แรงดันไฟฟ้าต่ำ (DDR3L) นอกจาก ECC ในแคช L2 แล้ว (ดูรูปที่ 2 อีกครั้ง) ความสามารถของ DDR3L ECC นี้รองรับความปลอดภัยของอุตสาหกรรมระดับ 3 (SIL 3) สถาปัตยกรรม i.MX 8X ยังขยายการรองรับ ECC ไปยังอุปกรณ์จัดเก็บข้อมูลแฟลชภายนอก ที่นี่โมดูลตัวเข้ารหัสและตัวถอดรหัส Bose, Ray-Chaudhuri, Hocquenghem (BCH) แบบบูรณาการให้ ECC 62 บิตสามารถแก้ไขข้อผิดพลาด 2 ถึง 20 บิตเดียวภายในบล็อกข้อมูลที่อ่านจากอุปกรณ์จัดเก็บข้อมูลเหล่านี้

การนำแอปพลิเคชันที่ใช้ i.MX 8X มาใช้

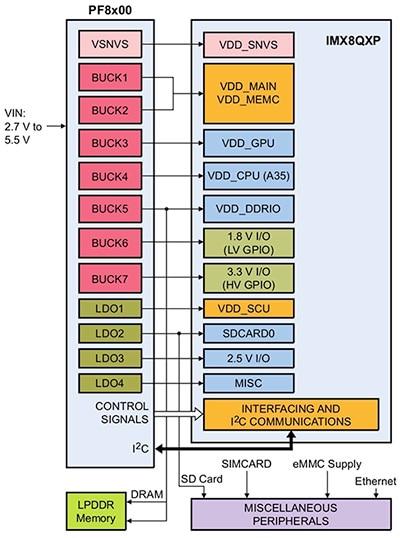

เช่นเดียวกับโปรเซสเซอร์ใด ๆ ในคลาสนี้การใช้การออกแบบที่ใช้ i.MX 8X จำเป็นต้องให้ความสำคัญอย่างรอบคอบกับข้อกำหนดที่เข้มงวดสำหรับพลังงานรวมถึงลำดับการเพิ่มพลังงานที่สำคัญ การเปิดเครื่องอุปกรณ์ i.MX 8X จำเป็นต้องเพิ่มกำลังไฟตามลำดับหรือพร้อมกันไปยังกลุ่มซัพพลายที่แตกต่างกันสี่กลุ่มโดยเริ่มจากระบบย่อย SVNS และดำเนินการต่อด้วย SCU, I/Os และอินเทอร์เฟซหน่วยความจำและในที่สุดก็เหลืออุปกรณ์ นักพัฒนาสามารถตอบสนองความต้องการนี้ได้เพียงใช้อุปกรณ์ PF8x00 power management integrated circuit (PMIC) ของ NXP ซึ่งมีรางแรงดันไฟฟ้าและสัญญาณควบคุมที่จำเป็นสำหรับรองรับโปรเซสเซอร์ i.MX 8X ตลอดจนหน่วยความจำภายนอกและอุปกรณ์ต่อพ่วงระบบทั่วไป (รูปที่ 5)

รูปที่ 5: NXP PF8x00 PMICs มีชุดรางแรงดันไฟฟ้าและสัญญาณควบคุมที่จำเป็นในการจ่ายไฟให้กับโปรเซสเซอร์ i.MX 8X (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

รูปที่ 5: NXP PF8x00 PMICs มีชุดรางแรงดันไฟฟ้าและสัญญาณควบคุมที่จำเป็นในการจ่ายไฟให้กับโปรเซสเซอร์ i.MX 8X (แหล่งรูปภาพ: NXP เซมิคอนดักเตอร์)

ในการนำการออกแบบที่ใช้ i.MX 8X ของตนเองไปใช้นักพัฒนาสามารถใช้ NXP MC33PF8100CCES PMIC ซึ่งตั้งโปรแกรมไว้ล่วงหน้าเพื่อใช้กับโปรเซสเซอร์ 8QuadXPlus เช่น MIMX8QX6AVLFZAC ตัวแปร PF8x00 อื่น ๆ เช่น MC33PF8100A0ES และ MC33PF8200A0ES รองรับโปรเซสเซอร์ i.MX 8X แต่ไม่ได้ตั้งโปรแกรมไว้ล่วงหน้า

สำหรับการใช้งานด้านความปลอดภัยอุปกรณ์ซีรีส์ PF8200 เช่น MC33PF8200A0ES จะรวมคุณสมบัติที่ออกแบบมาเพื่อรองรับระบบ ASIL B นอกเหนือจากจอภาพภายในหลายจอรวมถึงจอภาพแรงดันไฟฟ้าขาออกที่มีการอ้างอิงแบนด์แก็ปโดยเฉพาะแล้ว PF8200 PMIC ยังมีพินเอาต์พุตที่ไม่ปลอดภัย (FSOB) ที่ออกแบบมาเพื่อให้ระบบอยู่ในสถานะที่ปลอดภัยระหว่างการเปิดเครื่องหรือระหว่างเหตุการณ์ไฟฟ้าดับ นอกจากนี้กิจวัตรการทดสอบตัวเองแบบอะนาล็อก (ABIST) จะทดสอบจอภาพแรงดันไฟฟ้าทั้งหมดในขณะที่กิจวัตรการทดสอบตัวเองจะตรวจสอบการทำงานของอุปกรณ์อื่น ๆ

แม้ว่า PF8x00 PMIC จะช่วยลดความซับซ้อนในการออกแบบฮาร์ดแวร์ของระบบที่ใช้ i.MX 8X ได้ แต่นักพัฒนาบางรายอาจต้องเริ่มประเมินอุปกรณ์ i.MX 8X ทันทีและสร้างแอปพลิเคชันที่ใช้ i.MX 8X ขึ้นต้นแบบอย่างรวดเร็ว NXP’s MCIMX8QXP-CPU i.MX 8X Multisensory Enablement Kit (MEK) เป็นแพลตฟอร์มการพัฒนาที่พร้อมซึ่งรวมโปรเซสเซอร์ NXP i.MX 8QuadXPlus, NXP F8100 PMIC, แรม 3 กิกะไบต์ (Gbyte), หน่วยความจำ Multi-Media Controller (eMMC) ในตัว 32 Gbyte และ 64 หน่วยความจำแฟลชเมกะไบต์ (Mbyte) นอกจากอินเทอร์เฟซการแสดงผลกล้องและเสียงแล้วบอร์ด MEK ยังมีชุดเซ็นเซอร์ที่มักใช้ในยานยนต์หรือในอุตสาหกรรม สำหรับตัวเลือกการเชื่อมต่อเสียงและการขยายเพิ่มเติมนักพัฒนายังสามารถเพิ่มตัวเลือกของ NXP ได้อีกด้วย MCIMX8-8X-BB เบสบอร์ด

สรุป

สำหรับแอพพลิเคชั่นที่เพิ่มมากขึ้นเช่นยานยนต์อุตสาหกรรมการควบคุมอาคารและ HMIs ปริมาณงานการประมวลผลได้เพิ่มขึ้นเพื่อรวมทั้งการประมวลผล I/O แบบเรียลไทม์แบบดั้งเดิมและการประมวลผลระดับแอพพลิเคชั่นที่เกิดขึ้นใหม่พร้อมกราฟิกมัลติมีเดีย แม้ว่าจะมีตัวเลือกการออกแบบสำหรับปริมาณงานแต่ละประเภท แต่โซลูชันที่มีอยู่เพียงไม่กี่โซลูชันที่ตอบสนองความต้องการที่เพิ่มขึ้นสำหรับประสิทธิภาพสูงโซลูชันที่ประหยัดพลังงานสามารถตอบสนองความต้องการสำหรับการออกแบบที่ได้รับการรับรองด้านความปลอดภัยในยานยนต์และอุตสาหกรรม

ดังที่แสดงให้เห็นว่าการใช้โปรเซสเซอร์มัลติคอร์จาก NXP Semiconductors ทำให้นักพัฒนาสามารถใช้การออกแบบได้อย่างมีประสิทธิภาพมากขึ้นเพื่อตอบสนองความต้องการที่หลากหลายเหล่านี้และปรับขนาดได้ง่ายเพื่อตอบสนองความต้องการที่เกิดขึ้นใหม่เพื่อประสิทธิภาพสูง

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.