การใช้ประโยชน์จาก I3C เพื่อการสื่อสารระหว่าง IC ที่รวดเร็ว ง่ายขึ้น และยืดหยุ่นยิ่งขึ้น

Contributed By DigiKey's North American Editors

2024-12-17

อินเทอร์เฟซแบบอนุกรมออนบอร์ดสำหรับการสื่อสารระหว่างวงจรรวม (ไอซี, IC) นั้นส่วนใหญ่เป็นวงจรรวมระหว่างวงจร (I²C) และอินเทอร์เฟซอุปกรณ์ต่อพ่วงแบบอนุกรม (SPI) ซึ่งมีมาตั้งแต่ทศวรรษ 1980 อินเทอร์เฟซเหล่านี้ใช้กันอย่างแพร่หลายในการเชื่อมต่อเซ็นเซอร์และไอซีความเร็วต่ำเข้ากับหน่วยไมโครคอนโทรลเลอร์ (MCU) สำหรับการสื่อสารภายในบอร์ดในระยะทางสั้น อย่างไรก็ตาม เนื่องจากระบบดิจิทัลมีความเร็วมากขึ้น อินเทอร์เฟซเหล่านี้ซึ่งจำกัดอยู่ที่อัตราข้อมูลทั่วไป 1 เมกะบิตต่อวินาที (Mbit/s) สำหรับ I²C และ 10 Mbits/s สำหรับ SPI จึงกลายมาเป็นข้อจำกัดหลัก โดยข้อจำกัดอื่นๆ รวมทั้งสัญญาณอินเตอร์รัพท์หรือสัญญาณเปิดใช้งานชิป ต้องใช้การเชื่อมต่อสัญญาณเพิ่มเติม ทำให้จำนวนสายสัญญาณและความซับซ้อนของการเชื่อมต่อบัสเพิ่มขึ้น

บัสวงจรรวมระหว่างวงจรที่ได้รับการปรับปรุง (I3C) มีวัตถุประสงค์เพื่ออัปเกรดการสื่อสารระหว่างไอซี ซึ่งให้ระดับข้อมูลที่สูงขึ้น ความยืดหยุ่นที่มากขึ้น และอินเทอร์เฟซสองสายจริงพร้อมกับการอินเตอร์รัพแบบอินแบนด์ (IBI) แทนแบบภายนอก

บทความนี้จะกล่าวถึงคุณลักษณะของอินเทอร์เฟซ I3C และเหตุผลที่การอัปเกรดจากอินเทอร์เฟซอนุกรม I²C และ SPI อาจเป็นการอัปเกรดที่ดี โดยทั่วไปแล้วอุปกรณ์ MCU, สวิตช์ไอซี และเซ็นเซอร์จะถูกนำมาใช้เพื่อแสดงการใช้งานของตนเอง

บัสสื่อสารแบบฝังตัว

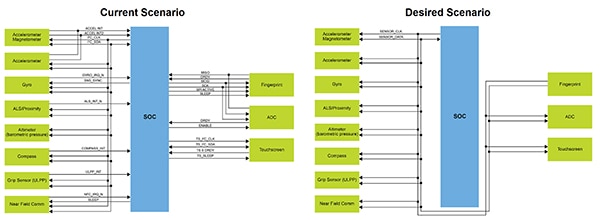

อินเตอร์คอนเนคแบบอนุกรมฝังตัว เช่น I²C และ SPI ถูกนำมาใช้ในการสื่อสารภายในบอร์ดมานานหลายปีแล้ว ส่วนใหญ่ใช้เป็นบัสการสื่อสารระหว่างเซ็นเซอร์และอุปกรณ์อินเทอร์เฟซผู้ใช้และโปรเซสเซอร์ควบคุม โดยจำนวนเซ็นเซอร์ในระบบทั่วไปเพิ่มขึ้นเป็นสิบถึงยี่สิบตัวในโทรศัพท์และมากกว่านั้นอย่างมากในยานพาหนะ ในเวลาเดียวกัน ข้อกำหนดด้านการสื่อสารกลายเป็นความท้าทายมากขึ้นสำหรับนักออกแบบ เนื่องจากความต้องการที่เพิ่มมากขึ้นในด้านความเร็วที่สูงขึ้น การใช้พลังงานที่น้อยลง และตัวนำที่น้อยลง นักออกแบบจะต้องตอบสนองความต้องการเหล่านี้ในขณะที่ยังคงควบคุมโปรเซสเซอร์ผ่านสัญญาณอินเตอร์รัพท์และสัญญาณเปิดใช้งาน (รูปที่ 1)

รูปที่ 1: การสื่อสารแบบฝังตัวควรรองรับความเร็วที่สูงกว่า พลังงานที่ต่ำลง และจำนวนสัญญาณขั้นต่ำ (แหล่งที่มาภาพ: NXP Semiconductors)

รูปที่ 1: การสื่อสารแบบฝังตัวควรรองรับความเร็วที่สูงกว่า พลังงานที่ต่ำลง และจำนวนสัญญาณขั้นต่ำ (แหล่งที่มาภาพ: NXP Semiconductors)

เทคโนโลยีปัจจุบันใช้เซ็นเซอร์และอินเทอร์เฟซอุปกรณ์ควบคุมผู้ใช้โดยใช้อินเทอร์เฟซ I²C สองสายหรือ SPI สี่สาย สัญญาณอินเตอร์รัพท์ สัญญาณเปิดใช้งาน และเส้นควบคุมอื่นๆ จะแยกจากสัญญาณนาฬิกาและสัญญาณข้อมูล ส่งผลให้มีสัญญาณต่ออินเทอร์เฟซมากขึ้น

นักออกแบบต้องใช้แนวทางอินเทอร์เฟซที่มองไปข้างหน้ามากขึ้นซึ่งจะกำจัดตัวนำพิเศษเหล่านี้ออกจากอินเตอร์คอนเนคและจัดการการทำงานเหล่านั้นแบบอินแบนด์โดยใช้เพียงสายสัญญาณนาฬิกาและข้อมูลเท่านั้น นอกจากนี้ บัสยังควรสามารถทำงานด้วยความเร็วที่สูงขึ้น และสูญเสียพลังงานน้อยลงด้วย

อินเทอร์เฟซ I3C

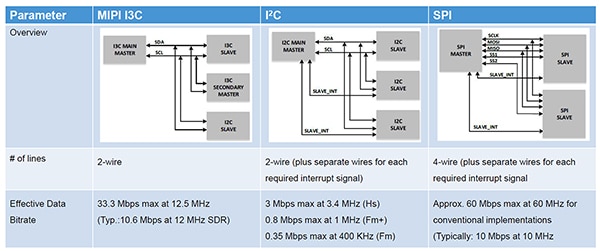

I3C ได้รับการพัฒนาโดย Mobile Industry Processor Interface (MIPI) Alliance เพื่อตอบสนองความต้องการเหล่านี้ โดยอินเทอร์เฟซมีให้ใช้งานทั้งในรูปแบบระหว่าง MIPI I3C และสมาชิก MIPI และในรูปแบบ MIPI I3C Basic โดยมีฟังก์ชันการทำงานที่ลดลงสำหรับอุปกรณ์ที่ไม่ใช่สมาชิก เช่นเดียวกับอินเทอร์เฟซ I²C และ SPI รุ่นเก่า รูปแบบที่ปรับปรุงแล้วนั้นเป็นแบบอนุกรมและใช้สายสัญญาณสองเส้นเพื่อลดจำนวนพินและจำนวนเส้นทางสัญญาณระหว่างส่วนประกอบ มีอัตราข้อมูลสูงถึง 12.5 Mbits/s ด้วยนาฬิกา 12.5 เมกะเฮิรตซ์ (MHz) โดยใช้โหมดอัตราข้อมูลเดี่ยว (SDR) ทำงานที่ระดับพลังงานต่ำและใช้สถาปัตยกรรมการออกแบบที่เรียบง่ายแต่ยืดหยุ่น

ที่น่าสังเกตคือ มาตรฐาน I3C ยังคงความเข้ากันได้ย้อนหลังกับระบบ I²C แบบจำกัด โดยอนุญาตให้เชื่อมต่ออุปกรณ์ I²C ที่มีอยู่เข้ากับบัส I3C ได้ ในขณะที่ยังอนุญาตให้บัสสลับไปใช้ความเร็วข้อมูลที่สูงกว่าสำหรับการสื่อสารระหว่างอุปกรณ์ I3C ที่เข้ากันได้ การเปรียบเทียบการกำหนดค่าระบบแสดงไว้ในรูปที่ 2

รูปที่ 2: การเปรียบเทียบการกำหนดค่าพื้นฐานของอินเทอร์เฟซ I3C, I²C และ SPI แสดงให้เห็นความเร็วที่ได้รับการปรับปรุงและการเดินสายที่ง่ายกว่าของ I3C (แหล่งที่มารูปภาพ: NXP Semiconductors)

รูปที่ 2: การเปรียบเทียบการกำหนดค่าพื้นฐานของอินเทอร์เฟซ I3C, I²C และ SPI แสดงให้เห็นความเร็วที่ได้รับการปรับปรุงและการเดินสายที่ง่ายกว่าของ I3C (แหล่งที่มารูปภาพ: NXP Semiconductors)

อินเทอร์เฟซ SPI สี่สายสามารถทำงานได้เร็วขึ้นและรองรับการสื่อสารแบบฟูลดูเพล็กซ์ โดย I²C สื่อสารโดยใช้การสื่อสารแบบฮาล์ฟดูเพล็กซ์บนบัสสองสายที่ประกอบด้วยสัญญาณนาฬิกา (SCL) และสัญญาณข้อมูล (SDA) ทั้งสองต้องใช้สายสัญญาณพิเศษเพื่อรองรับอินเตอร์รัพท์และฟังก์ชันการควบคุมอื่น ๆ เช่นการเลือกชิป ซึ่ง I3C ลดจำนวนสายที่ใช้ในอินเทอร์เฟซลงเหลือสองสาย โดยขจัดสายสัญญาณอินเตอร์รัพต์ สายสัญญาณเปิดใช้งาน และสัญญาณเลือกชิปที่แยกจากกันที่ใช้ใน I²C และ SPI การลดจำนวนสายลงนี้ถือเป็นข้อได้เปรียบที่สำคัญในระบบที่ต้องใช้เซ็นเซอร์แต่ละตัวจำนวน 10 ถึง 20 ตัวที่เชื่อมต่อกับโปรเซสเซอร์ โดยแต่ละตัวมีสายรองจำนวนหลายเส้น สัญญาณอินเตอร์รัพท์และสัญญาณควบคุมอื่น ๆ จะถูกแทนที่ด้วย IBI ในวิธีนี้ เซ็นเซอร์หรืออุปกรณ์เป้าหมายจะกำหนดที่อยู่ของตัวเองลงในส่วนหัวที่อยู่ของบัส I3C เพื่อแจ้งให้โปรเซสเซอร์ทราบถึงอินเตอร์รัพท์

ความแตกต่างของอัตราสัญญาณนาฬิการะหว่าง I²C และ I3C มีความสำคัญ โดยทั่วไป I²C จะมีความถี่อยู่ที่ 100 กิโลเฮิรตซ์ (kHz), 400 kHz หรือ 1 MHz ในขณะที่ I3C จะมีความถี่ได้ที่ 12.5 MHz ก่อนหน้านี้ SPI ใช้สำหรับอัตราความเร็วสัญญาณนาฬิกาที่สูงกว่า 1 MHz การเลือกการออกแบบจะอยู่ระหว่างอัตราความเร็วสัญญาณนาฬิกาและจำนวนสายไฟ I3C ได้เปลี่ยนแปลงสิ่งนั้นด้วยการเสนอสัญญาณนาฬิกาและอัตราข้อมูลที่สูงขึ้นโดยใช้โทโพโลยีสองสายจริง

เอาท์พุตแบบพุช-พูล ซึ่งสามารถสวิตช์ได้เร็วกว่าไดรเวอร์โอเพ่นเดรนหรือคอลเลกเตอร์ ถือเป็นปัจจัยสำคัญที่ช่วยเพิ่มอัตราสัญญาณนาฬิกาของ I3C เพื่อรักษาความเข้ากันได้กับอุปกรณ์ I²C นั้น I3C สามารถสวิตช์ระหว่างไดรเวอร์แบบโอเพ่นเดรนและแบบพุช-พูลได้ขึ้นอยู่กับสถานะของบัส การออกแบบแบบโอเพ่นเดรนหรือคอลเลกเตอร์จะใช้ระหว่างการกำหนดที่อยู่หรือการชี้ขาดเริ่มต้น ซึ่งทั้งอุปกรณ์ I²C และ I3C อาจอยู่บนสายพร้อมกันได้ I3C จะใช้การพุช-พูลเมื่อการสื่อสารเป็นทิศทางเดียว และไม่มีโอกาสที่อุปกรณ์ I²C จะสื่อสารพร้อมกัน

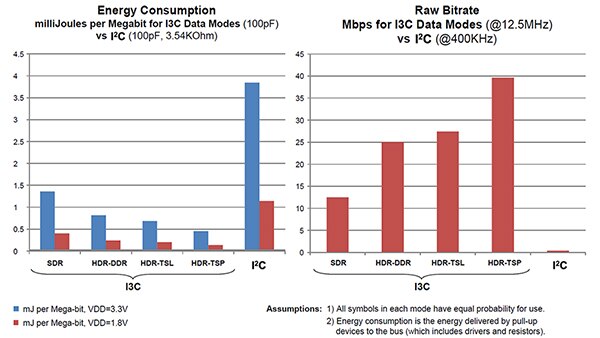

นอกเหนือจาก SDR มาตรฐานแล้ว I3C ยังรองรับโหมดอัตราข้อมูลสูง (HDR) เสริมอีกหลายโหมด ซึ่งโหมด HDR เหล่านี้ทำงานด้วยอัตราสัญญาณนาฬิกาเดียวกัน แต่ส่งข้อมูลด้วยความหนาแน่นของข้อมูลที่สูงกว่า โดยโหมด HDR แรกคือโหมด HDR double data rate (HDR-DDR) ซึ่งข้อมูลจะถูกบันทึกที่ขอบทั้งสองด้านของสัญญาณนาฬิกา ทำให้มีอัตราข้อมูลเพิ่มขึ้นเกือบสองเท่า สำหรับสัญญาณนาฬิกา 12.5 MHz โหมด DDR จะให้ความเร็วข้อมูลที่มีประสิทธิภาพ 20 Mbits/s

สัญลักษณ์เทอร์นารี HDR มี 2 เวอร์ชัน: สัญลักษณ์เทอร์นารี HDR แบบบริสุทธิ์ (HDR-TSP) สำหรับอุปกรณ์ I3C เท่านั้น และสัญลักษณ์เทอร์นารี HDR แบบเดิม (HDR-TSL) สำหรับบัสรวมทั้งอุปกรณ์ I²C และ I3C โหมดสัญลักษณ์เทอร์นารีจะมีข้อมูลสามบิตต่อนาฬิกาโดยใช้สัญลักษณ์สามบิต (เทอร์นารี) ที่เข้ารหัสบนสาย SCL และ SDA

โหมดการขนส่งจำนวนมาก HDR (HDR-BT) มอบข้อมูลสูงสุดโดยรองรับการสื่อสารผ่านสายข้อมูล SDA สี่สาย คู่สาย หรือสายเดียว ส่งผลให้ประสิทธิภาพอัตราข้อมูลเดี่ยวแบบดิบเพิ่มขึ้นแปด สี่ หรือสองเท่าที่อัตราสัญญาณนาฬิกาเดียวกัน

การเพิ่มความเร็วในการถ่ายโอนข้อมูลนี้ช่วยให้สามารถเปิดอุปกรณ์ได้ในระยะเวลาสั้นลง ซึ่งจะช่วยลดรอบการทำงานของพลังงานบัส ซึ่งจะลดการใช้พลังงานลงเมื่อเทียบกับ I²C (รูปที่ 3) การเปลี่ยนแปลงจากไดร์เวอร์ตัวเก็บรวบรวมแบบเปิดที่มีตัวต้านทานดึงขึ้นภายนอกไปเป็นไดร์เวอร์แบบผลักดึงช่วยลดการใช้พลังงานลงอีก เนื่องจากตัวต้านทานแบบดึงขึ้นต้องใช้พลังงานมากในการทำงาน

รูปที่ 3: I3C นำเสนอการปรับปรุงอัตราข้อมูลและการใช้พลังงานเมื่อเทียบกับ I²C (แหล่งที่มารูปภาพ: NXP Semiconductors)

รูปที่ 3: I3C นำเสนอการปรับปรุงอัตราข้อมูลและการใช้พลังงานเมื่อเทียบกับ I²C (แหล่งที่มารูปภาพ: NXP Semiconductors)

การระบุข้อความ

I²C ใช้ที่อยู่คงที่ความยาว 7 หรือ 10 บิตสำหรับอุปกรณ์บัสแต่ละตัว สิ่งนี้ได้รับการเปลี่ยนแปลงใน I3C เป็นการกำหนดที่อยู่แบบไดนามิก 7 บิต ซึ่งบัสมาสเตอร์จะตั้งค่าที่อยู่ของอุปกรณ์ในระหว่างการกำหนดที่อยู่แบบไดนามิก (DAA) และจัดเก็บไว้ในรีจิสเตอร์อุปกรณ์ การกำหนดที่อยู่คงที่ เช่นเดียวกับในกรณีของอุปกรณ์ต่อพ่วง I²C ยังคงใช้ใน I3C ได้

เนื่องจากการกำหนดที่อยู่แบบไดนามิก ที่อยู่อุปกรณ์จึงสามารถเปลี่ยนได้ในภายหลัง สิ่งนี้รองรับการเข้าร่วมแบบฮอตซึ่งทำให้สามารถเพิ่มอุปกรณ์ใหม่เข้าในบัสได้ในขณะที่กำลังทำงาน อุปกรณ์ใหม่ที่เชื่อมต่อกับบัส I3C จะส่งสัญญาณการมีอยู่ไปยังมาสเตอร์ I3C โดยการส่งคำขอเข้าร่วมแบบฮอต ตัวควบคุมหลักรับทราบคำขอและกำหนดที่อยู่เพื่อเพิ่มอุปกรณ์เข้าในบัส

IBI

I3C เป็นบัสสองสายจริงที่ใช้ IBI แทนสัญญาณอินเตอร์รัพท์เฉพาะเช่น I²C โดย IBI คือเมื่ออุปกรณ์เป้าหมายส่งสัญญาณความพร้อมใช้งานไปยังมาสเตอร์โดยการดึงสาย SDA ลงมา จากนั้นมาสเตอร์จะเริ่มนาฬิกาบนเส้น SCL และอุปกรณ์เป้าหมายจะส่งที่อยู่ของนาฬิกาไปยังบัส I3C เพื่อแจ้งให้ตัวควบคุมทราบถึงอินเตอร์รัพท์

รหัสคำสั่งทั่วไป

Common Command Codes (CCC) เป็นคำสั่งมาตรฐานที่ตัวควบคุมสามารถส่งไปยังอุปกรณ์ I3C ทั้งหมดพร้อมกันหรือไปยังอุปกรณ์เป้าหมายที่เฉพาะเจาะจงได้ โดยคำสั่งเหล่านี้มีไว้สำหรับรายการที่เกี่ยวข้องกับการจัดการบัส รูปแบบของโปรโตคอล CCC เริ่มต้นด้วยที่อยู่การบรอดคาสต์ I3C ซึ่งได้รับการยอมรับโดยอุปกรณ์ I3C ทั้งหมดบนบัส อุปกรณ์ I²C ใดๆ บนบัสจะไม่ตอบรับคำขอ เนื่องจากเป็นที่อยู่ I²C ที่สงวนไว้

คำสั่งแต่ละคำสั่งประกอบด้วยฟิลด์ ID ตัวอธิบาย 8 บิตและอาจตามด้วยเนื้อหาคำสั่ง คำสั่งที่ส่งไปยังอุปกรณ์เฉพาะจะส่งผ่านที่อยู่อุปกรณ์ในไบต์แรกของเพย์โหลด มีคำสั่ง CCC มากกว่าสี่สิบคำสั่ง รวมถึง:

- ป้อนการกำหนดที่อยู่แบบไดนามิก (ENTDAA)

- ตั้งค่าการกำหนดที่อยู่แบบไดนามิกใหม่ (SETNEWDA)

- เปิดใช้งานเหตุการณ์ (ENEC) / ปิดใช้งานเหตุการณ์ (DISEC)

- รีเซ็ตการกำหนดที่อยู่แบบไดนามิก (RSTDAA)

- เข้าสู่โหมดอัตราข้อมูลสูง (ENTHDRx)

- รับรีจิสเตอร์คุณลักษณะอุปกรณ์ (GETDCR)

เวนเดอร์ได้รับอนุญาตให้มี CCC ID เฉพาะเพื่อใช้คำสั่งของตนเอง

การตรวจจับและการกู้คืนข้อผิดพลาด

I3C มีข้อกำหนดสำหรับการตรวจจับและการกู้คืนข้อผิดพลาดต่างจาก I²C ซึ่งจะกำหนดให้มีวิธีแก้ไขข้อผิดพลาดและการกู้คืนหกวิธีสำหรับอุปกรณ์เป้าหมาย และมีอีกวิธีหนึ่งเป็นทางเลือก นอกจากนี้ยังมีวิธีการแสดงข้อผิดพลาดและการกู้คืนเพิ่มเติมสำหรับข้อผิดพลาดด้านมาสเตอร์โดยเฉพาะ

ส่วนประกอบที่รองรับ I3C

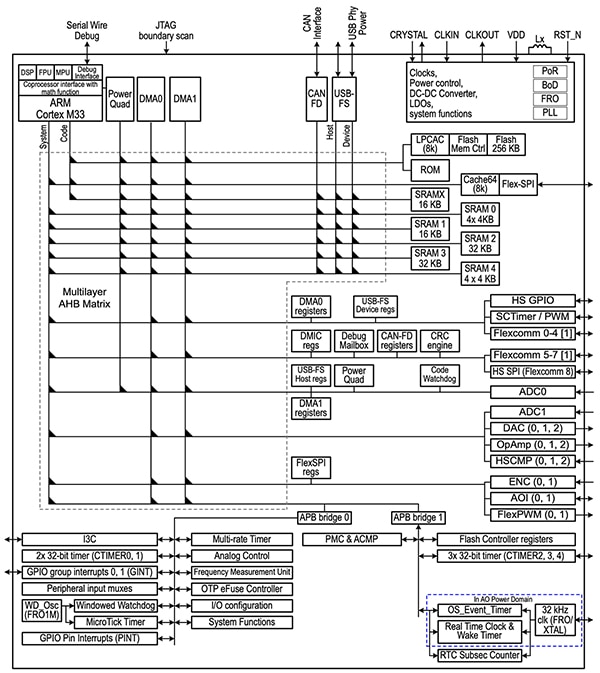

ตามที่แสดงในรูปที่ 2 (ซ้าย) เครือข่าย I3C พื้นฐานประกอบด้วยตัวควบคุมหลักอย่างน้อยหนึ่งตัวและเป้าหมายหรือสเลฟ I3C หนึ่งตัวขึ้นไป- มาสเตอร์หลักสามารถเป็น MCU เช่น NXP Semiconductors LPC5534JHI48-00MP (รูปที่ 4) เป็น MCU Arm® Cortex®-M33 ขนาด 32 บิต ที่มี SRAM ขนาด 128 กิโลไบต์ (Kbytes) และแฟลชขนาด 256 Kbytes อินเทอร์เฟซ Flexcomm รองรับอินเทอร์เฟซแบบอนุกรมที่แตกต่างกันแปดแบบ รวมถึง I3C

รูปที่ 4: MCU LPC5534JHI48/00MP มีอินเทอร์เฟซ I3C และอินเทอร์เฟซอนุกรมอื่นอีกเจ็ดแบบ (แหล่งที่มาภาพ: NXP Semiconductor)

รูปที่ 4: MCU LPC5534JHI48/00MP มีอินเทอร์เฟซ I3C และอินเทอร์เฟซอนุกรมอื่นอีกเจ็ดแบบ (แหล่งที่มาภาพ: NXP Semiconductor)

บัส I3C อนุญาตให้เพิ่มมาสเตอร์รองให้กับบัสเป็นสเลฟได้ โดย I3C สามารถมีมาสเตอร์ได้หลายตัว แต่สามารถเป็นตัวควบคุมได้เพียงตัวเดียวเท่านั้น เมื่อลงทะเบียนแล้ว มาสเตอร์รองสามารถร้องขอสถานะมาสเตอร์ปัจจุบันได้ และหากมาสเตอร์ปัจจุบันยินยอม การควบคุมของเขาจะถูกโอนไปยังมาสเตอร์รองที่ร้องขอ

เซ็นเซอร์ I3C ทั่วไปคือ P3T2030CUKAZ ของ NXP เซ็นเซอร์วัดอุณหภูมิตัวนี้แปลงอุณหภูมิตั้งแต่ -40°C ถึง +125°C ให้เป็นค่าดิจิทัล 12 บิต โดยมีความแม่นยำ ±2°C ประกอบด้วยอินเทอร์เฟซอนุกรมโหมด I²C และ I3C SDR

เซ็นเซอร์ที่ซับซ้อนยิ่งขึ้นคือ ไจโรสโคประบบไมโครอิเล็กโตรแมคคานิกส์สามแกน (MEMS) รุ่น ICM-42605 และเครื่องวัดความเร่งจาก TDK InvenSense เมื่อใช้ไจโรอัตราการหมุนจะวัดอัตราการหมุนตั้งแต่ ±15.2 ถึง ±2000 องศาต่อวินาที (°/s) ช่วงการวัดความเร่งคือ ±2 ถึง ±15 g ตรวจจับการเคลื่อนไหว, การเอียง, การแตะ, หรือจำนวนก้าว (เครื่องวัดระยะทาง) เนื่องจากเป็นเซ็นเซอร์ I3C จึงทำงานที่ความถี่ 12.5 MHz ในโหมด SDR และ 25 MHz ในโหมด DDR

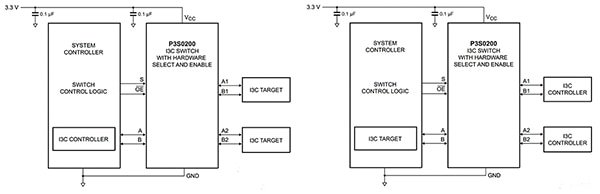

ไอซี เช่น สวิตช์ I3C รุ่น P3S0200GMX ของ NXP สามารถกำหนดค่าบัส I3C ใหม่ได้โดยการกำหนดเส้นทางสัญญาณบัส I3C ระหว่างตัวควบคุม I3C และอุปกรณ์เป้าหมายหลายชุด หรือระหว่างเป้าหมายเดียวและตัวควบคุม I3C หลายตัวตามที่กำหนดโดย MCU ภายนอก (รูปที่ 5)

รูปที่ 5: สวิตช์ P3S0200GMX I3C สามารถใช้เพื่อกำหนดค่าบัส I3C ใหม่ได้โดยการกำหนดเส้นทางสัญญาณบัส I3C ระหว่างตัวควบคุม I3C และอุปกรณ์เป้าหมายหลายชุด หรือระหว่างเป้าหมายเดียวและตัวควบคุม I3C หลายตัว (แหล่งที่มารูปภาพ: NXP Semiconductors)

รูปที่ 5: สวิตช์ P3S0200GMX I3C สามารถใช้เพื่อกำหนดค่าบัส I3C ใหม่ได้โดยการกำหนดเส้นทางสัญญาณบัส I3C ระหว่างตัวควบคุม I3C และอุปกรณ์เป้าหมายหลายชุด หรือระหว่างเป้าหมายเดียวและตัวควบคุม I3C หลายตัว (แหล่งที่มารูปภาพ: NXP Semiconductors)

การสวิตช์ระหว่างเป้าหมายสองเป้าหมายอาจจำเป็นหากเป้าหมายทั้งสองมีที่อยู่เดียวกันและไม่สามารถอยู่บนบัสเดียวกันได้ หรืออาจต้องแบ่งปันเป้าหมายเดียวระหว่างสองกระบวนการ ซึ่งจำเป็นต้องสวิตช์ระหว่างตัวควบคุม I3C สองตัว

สรุป

I3C เป็นอินเทอร์เฟซแบบอนุกรมที่ขยายบัส I²C ด้วยการเพิ่มอัตราข้อมูล ลดจำนวนสาย และเพิ่มความยืดหยุ่นในการควบคุมบัส เป็นการปรับปรุงที่ขยายประโยชน์ใช้สอยของอินเทอร์เฟซ I²C และ SPI รุ่นเก่า

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.