วิธีการออกแบบและรับรองระบบที่ใช้ RTD ที่ปลอดภัยในการใช้งาน

Contributed By DigiKey's North American Editors

2023-07-24

ตัวตรวจจับอุณหภูมิตามการเปลี่ยนแปลงของความต้านทาน (RTD) ซึ่งประกอบด้วยทรานสดิวเซอร์และวงจรการปรับสภาพสัญญาณฟรอนต์เอนแบบแอนะล็อก (AFE) นั้นถูกนำมาใช้อย่างแพร่หลาย มีความแม่นยำ และเชื่อถือได้ อย่างไรก็ตาม สำหรับการใช้งานที่มีความสำคัญและมีความน่าเชื่อถือสูง มักจำเป็นต้องมีการออกแบบและการรับรองระบบที่ปลอดภัยในการใช้งานผ่านกระบวนการรับรองส่วนประกอบ Route 1S หรือ Route 2S

การรับรองระบบเพื่อความปลอดภัยในการทำงานเป็นกระบวนการที่ซับซ้อน เนื่องจากส่วนประกอบทั้งหมดในระบบต้องได้รับการตรวจสอบเพื่อหาอาการและกลไกความล้มเหลวที่อาจเกิดขึ้น ซึ่งมีการวินิจฉัยความล้มเหลวหลายวิธี และการใช้ชิ้นส่วนที่ได้รับการรับรองช่วยลดภาระงานไปพร้อมกับกระบวนการรับรอง

โปรดทราบว่า "ความน่าเชื่อถือ" เกี่ยวข้องกับความปลอดภัยในการใช้งาน แต่ไม่ใช่สิ่งเดียวกัน โดยความน่าเชื่อถือหมายถึงการออกแบบและการนำไปใช้งานซึ่งทำงานตามข้อมูลจำเพาะโดยไม่มีปัญหาหรือความล้มเหลว ในขณะที่ "ปลอดภัยในการใช้งาน" หมายความว่าจะต้องตรวจพบความล้มเหลวใด ๆ โดยการออกแบบ ซึ่งจำเป็นต้องมีทั้งความน่าเชื่อถือและความปลอดภัยในการใช้งานสำหรับการใช้งานที่สำคัญ

บทความนี้จะศึกษาพื้นฐานของ RTD และวงจรการปรับสภาพสัญญาณในบริบทของการรับรองความปลอดภัยในการใช้งาน จากนั้นจะกล่าวถึงเกี่ยวกับความน่าเชื่อถือระดับต่าง ๆ และการรับรองความล้มเหลว และสิ่งที่จำเป็นเพื่อให้ผ่านการรับรองทั้งสอง โดยจะใช้ไอซี RTD AFE แบบหลายช่องสัญญาณสองตัว ไอซี AD7124 คู่จาก Analog Devices ควบคู่ไปกับรูปแบบบอร์ดประเมินผลที่เกี่ยวข้อง เพื่ออธิบายประเด็นสำคัญ

บทบาทของความปลอดภัยในการทำงาน

บทบาทของความปลอดภัยในการทำงานคือการปราศจากความเสี่ยงที่ยอมรับไม่ได้ในการบาดเจ็บหรือความเสียหายต่อสุขภาพของผู้คนผ่านการใช้งานฟังก์ชันการป้องกัน/ความปลอดภัยโดยอัตโนมัติอย่างน้อยหนึ่งฟังก์ชันอย่างเหมาะสม ซึ่งช่วยให้มั่นใจได้ว่าผลิตภัณฑ์ อุปกรณ์ หรือระบบยังคงทำงานอย่างปลอดภัยหากเกิดความผิดปกติขึ้น ซึ่งจำเป็นในการใช้งานอุตสาหกรรม เชิงพาณิชย์ และแม้แต่การใช้งานสำหรับผู้บริโภคบางประเภท เช่น:

- ยานพาหนะอัตโนมัติ

- ความปลอดภัยของเครื่องจักรและหุ่นยนต์

- ระบบควบคุมอุตสาหกรรม (ICS)

- ผลิตภัณฑ์บ้านอัจฉริยะสำหรับผู้บริโภค

- โรงงานอัจฉริยะและซัพพลายเชน

- ระบบเครื่องมือวัดความปลอดภัยและระบบควบคุมสถานที่อันตราย

ตัวอย่างการออกแบบที่ปลอดภัยในการใช้งาน เช่น ฟังก์ชันสวิตช์มาสเตอร์สำหรับการเปิด/ปิดจะยังคงรองรับการปิดเครื่อง แม้ว่าส่วนประกอบอื่นๆ ในระบบจะล้มเหลว (รูปที่ 1)

รูปที่ 1: ในระบบที่ปลอดภัยต่อการใช้งาน ไม่ต้องสงสัยว่าสวิตช์นี้ออกแบบมาเพื่ออะไร (แหล่งที่มาภาพ: Pilla ผ่าน City Electric Supply Co.)

รูปที่ 1: ในระบบที่ปลอดภัยต่อการใช้งาน ไม่ต้องสงสัยว่าสวิตช์นี้ออกแบบมาเพื่ออะไร (แหล่งที่มาภาพ: Pilla ผ่าน City Electric Supply Co.)

พื้นฐานเกี่ยวกับ RTD

ทำไมต้องดูอุณหภูมิและความปลอดภัยในการทำงาน? เหตุผลหนึ่งที่ดีคืออุณหภูมิเป็นพารามิเตอร์ทางกายภาพที่วัดมากที่สุด ซึ่งมักเกี่ยวข้องกับความปลอดภัยหรือการใช้งานที่สำคัญ และรองรับโดยทรานสดิวเซอร์ที่มีให้เลือกมากมาย หนึ่งในทรานสดิวเซอร์เหล่านั้น ได้แก่ RTD ซึ่งมีแนวคิดที่เรียบง่าย โดยใช้ประโยชน์จากค่าสัมประสิทธิ์การต้านทานอุณหภูมิ (TCR) เป็นที่รู้จักและเกิดซ้ำได้ของโลหะ เช่น นิกเกิล ทองแดง และแพลทินัม โดย RTD จากแพลทินัมที่มีความต้านทาน 100 โอห์ม (Ω) และ 1,000 โอห์มที่ 0°C นั้นถูกใช้อย่างแพร่หลายมากที่สุด และสามารถใช้ได้ในช่วงอุณหภูมิ -200°C ถึง +850°C

RTD เหล่านี้มีความสัมพันธ์เชิงเส้นตรงระหว่างความต้านทานต่ออุณหภูมิในช่วงอุณหภูมิดังกล่าว สำหรับกรณีที่มีความแม่นยำสูงพิเศษ จะต้องใช้ตารางการแก้ไขและชดเชยและปัจจัยต่าง ๆ ที่สามารถนำมาใช้ได้ โดย RTD แพลทินัมที่มีความต้านทาน 100 Ω (หรือ PT100) มีความต้านทานทั่วไปที่ 18 Ω ที่ -200°C และ 390.4 Ω ที่ +850°C

การใช้ RTD จำเป็นต้องกระตุ้นกระแสที่ทราบค่าซึ่งโดยปกติจะอยู่ที่ประมาณ 1 มิลลิแอมป์ (mA) เพื่อลดความร้อนในตัวเองให้เหลือน้อยที่สุด นอกจากนี้ยังใช้ค่ากระแสอื่น ๆ ขึ้นอยู่กับค่าความต้านทาน RTD ที่ระบุ

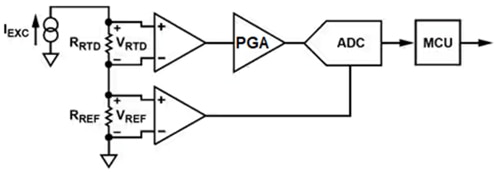

แรงดันตกคร่อม RTD จะถูกวัดพร้อมกันผ่าน AFE ซึ่งประกอบด้วยตัวขยายสัญญาณแบบตั้งโปรแกรมได้ (PGA) และในแทบทุกกรณี ตัวแปลงแอนะล็อกเป็นดิจิตอล (ADC) จะใช้งานร่วมกับไมโครคอนโทรลเลอร์ (MCU) (รูปที่ 2)

รูปที่ 2: การใช้ RTD เพื่อวัดอุณหภูมิจำเป็นต้องป้อนกระแสที่ทราบค่าให้กับ RTD และวัดแรงดันตกคร่อม จากนั้นใช้กฎของโอห์ม (แหล่งที่มาภาพ: Digi-Key)

รูปที่ 2: การใช้ RTD เพื่อวัดอุณหภูมิจำเป็นต้องป้อนกระแสที่ทราบค่าให้กับ RTD และวัดแรงดันตกคร่อม จากนั้นใช้กฎของโอห์ม (แหล่งที่มาภาพ: Digi-Key)

โทโพโลยีวงจรของโครงร่างพื้นฐานนี้เหมือนกับการใช้ตัวต้านทานตรวจวัดเพื่อกำหนดกระแสผ่านโหลด แต่ในที่นี่จะมีการเปลี่ยนตัวแปรที่ทราบค่าและไม่ทราบค่า สำหรับการตรวจจับกระแส จะทราบความต้านทานในขณะที่ไม่ทราบกระแส ดังนั้นการคำนวณคือ I = V/R สำหรับ RTD ที่ทราบค่ากระแส แต่ไม่ทราบค่าความต้านทาน ดังนั้นการคำนวณคือ R = V/I

PGA จำเป็นต่อการรักษาความสมบูรณ์ของสัญญาณและเพิ่มช่วงไดนามิกให้สูงสุด เนื่องจากระดับแรงดันไฟฟ้าทั่วทั้ง RTD สามารถอยู่ในช่วงตั้งแต่ 10 มิลลิโวลต์ไปจนถึงหลายร้อยมิลลิโวลต์ ขึ้นอยู่กับประเภทและอุณหภูมิของ RTD

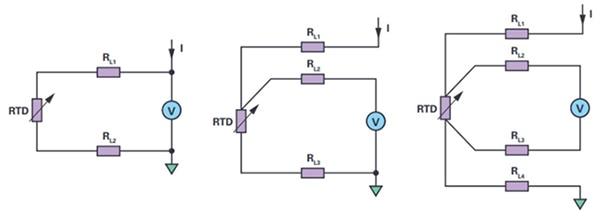

การเชื่อมต่อทางกายภาพระหว่างแหล่งกระตุ้น RTD และ PGA สามารถเป็นอินเทอร์เฟซสอง สาม หรือสี่สาย แม้ว่าโดยหลักการแล้วตัวนำสองสายจะเพียงพอ แต่ก็มีปัญหาที่เกี่ยวข้องกับการลดลงของ IR ในสายการเชื่อมต่อ พร้อมกับค่าอื่นๆ การใช้โทโพโลยีแบบสามสายและสี่สายในการเชื่อมต่อแบบเคลวินขั้นสูงทำให้ได้ประสิทธิภาพที่แม่นยำและสม่ำเสมอมากขึ้น แม้ว่าจะเพิ่มค่าใช้จ่ายในการเดินสาย (รูปที่ 3)

รูปที่ 3: สามารถขับเคลื่อนและตรวจจับ RTD ผ่านสายไฟเพียงสองเส้น (ซ้าย) แต่การใช้สายไฟสามเส้น (ตรงกลาง) และแม้แต่สี่สายไฟ (ขวา การเชื่อมต่อแบบเคลวิน) ช่วยให้สามารถกำจัดแหล่งที่มาของข้อผิดพลาดต่างๆ เนื่องจากสายไฟได้ (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 3: สามารถขับเคลื่อนและตรวจจับ RTD ผ่านสายไฟเพียงสองเส้น (ซ้าย) แต่การใช้สายไฟสามเส้น (ตรงกลาง) และแม้แต่สี่สายไฟ (ขวา การเชื่อมต่อแบบเคลวิน) ช่วยให้สามารถกำจัดแหล่งที่มาของข้อผิดพลาดต่างๆ เนื่องจากสายไฟได้ (แหล่งที่มาภาพ: Analog Devices)

เริ่มต้นด้วยคำศัพท์และมาตรฐาน

ความปลอดภัยในการทำงานมีคำศัพท์เฉพาะ ชุดข้อมูล และตัวย่อมากมายที่ใช้กันอย่างแพร่หลายในการอภิปรายที่เกี่ยวข้อง ในจำนวนนี้คือ:

- เวลาที่จะล้มเหลว (FIT): จำนวนความล้มเหลวที่อาจเกิดขึ้นได้ในหนึ่งพันล้าน (109) ชั่วโมงการทำงานของอุปกรณ์

- การวิเคราะห์อาการล้มเหลวและผลกระทบ (FMEA): กระบวนการตรวจสอบส่วนประกอบ ชุดประกอบ และระบบย่อยต่างๆ ให้ได้มากที่สุดเท่าที่จะเป็นไปได้ เพื่อระบุอาการขัดข้องที่อาจเกิดขึ้นในระบบ ตลอดจนสาเหตุและผลกระทบ

- การวิเคราะห์ผลกระทบและการวินิจฉัยอาการขัดข้อง (FMEDA): เทคนิคการวิเคราะห์อย่างเป็นระบบเพื่อให้ได้มาซึ่งอัตราความล้มเหลวในระดับระบบย่อย/ผลิตภัณฑ์ อาการขัดข้อง และความสามารถในการวินิจฉัย

จำเป็นต้องมีข้อมูล FIT พร้อมกับการวิเคราะห์ผลกระทบและการวินิจฉัยอาการขัดข้อง (FMEDA) ในส่วนประกอบต่างๆ ในระบบสำหรับการวิเคราะห์ทั้งหมด FMEA นำเสนอข้อมูลเชิงคุณภาพเท่านั้น ขณะที่ FMEDA นำเสนอข้อมูลทั้งเชิงคุณภาพและเชิงปริมาณ ช่วยให้ผู้ใช้สามารถวัดระดับวิกฤตไปสู่อาการขัดข้องและจัดลำดับตามความสำคัญได้ โดย FMEDA เพิ่มความเสี่ยง อาการขัดข้อง การวิเคราะห์ผลกระทบและการวินิจฉัย และข้อมูลความน่าเชื่อถือ

- ค่าระดับความปลอดภัย (SIL): มีค่าระดับแบบไม่ต่อเนื่องสี่ระดับที่เกี่ยวข้องกับ SIL: SIL 1, SIL 2, SIL 3 และ SIL 4 ยิ่งระดับ SIL สูง ระดับความปลอดภัยที่เกี่ยวข้องก็จะยิ่งสูงขึ้น และความน่าจะเป็นที่ระบบจะทำงานผิดพลาดก็จะยิ่งต่ำลง

ระดับ SIL 2 บ่งชี้ว่าสามารถวินิจฉัยความล้มเหลวภายในระบบได้มากกว่า 90% ในการรับรองการออกแบบ ผู้ออกแบบระบบต้องแสดงหลักฐานความล้มเหลวที่อาจเกิดขึ้นต่อหน่วยงานรับรอง ไม่ว่าจะเป็นความล้มเหลวที่ปลอดภัยหรือความล้มเหลวที่เป็นอันตราย และจะวินิจฉัยว่าเกิดความล้มเหลวได้อย่างไร

- IEC 61508 ชื่ออย่างเป็นทางการว่า “Functional Safety of Electrical/Electronic/Programmable Electronic Safety-related Systems” (และเรียกอย่างไม่เป็นทางการว่า “Electronic Functional Safety”) เป็นข้อกำหนดเฉพาะสำหรับการออกแบบที่ปลอดภัยต่อการใช้งาน โดยจะบันทึกขั้นตอนการออกแบบที่จำเป็นในการพัฒนาชิ้นส่วนที่ผ่านการรับรอง SIL จำเป็นต้องมีการสร้างเอกสารสำหรับแต่ละขั้นตอน ตั้งแต่แนวคิดและคำจำกัดความไปจนถึงการออกแบบ เค้าโครง การประดิษฐ์ การประกอบ และการทดสอบ

กระบวนการนี้เรียกว่า Route 1S และมีความซับซ้อน อย่างไรก็ตาม มีทางเลือกอื่นสำหรับ Route 1S ที่เรียกว่า Route 2S ที่เป็นวิธีการที่ “ได้รับการพิสูจน์ในการใช้งาน” และใช้ได้เมื่อผลิตภัณฑ์จำนวนมากได้รับการออกแบบเป็นผลิตภัณฑ์ขั้นสุดท้ายและระบบ และกำลังใช้งานในภาคสนามด้วยการทำงานสะสมหลายพันชั่วโมง

ภายใต้ Route 2S ผลิตภัณฑ์ยังคงได้รับการรับรองโดยแสดงหลักฐานต่อหน่วยงานออกใบรับรอง:

- ปริมาณที่ใช้ในฟิลด์

- การวิเคราะห์ผลิตภัณฑ์ส่งคืนใดๆ จากภาคสนามและรายละเอียดว่าผลิตภัณฑ์ส่งคืนไม่ได้เกิดจากความล้มเหลวภายในส่วนประกอบเอง

- เอกสารข้อมูลความปลอดภัยที่ให้รายละเอียดเกี่ยวกับการวินิจฉัยและความครอบคลุมที่มีให้

- FMEDA แบบ Pin และแบบ Die

การผสานอินเทอร์เฟซ RTD กับ SIL Route 2S

การรับรองระบบเป็นกระบวนการที่ยาวนาน เนื่องจากส่วนประกอบทั้งหมดในระบบต้องได้รับการตรวจสอบเพื่อหากลไกความล้มเหลวที่อาจเกิดขึ้น และมีวิธีการต่างๆ ในการวินิจฉัยความล้มเหลว ซึ่งการใช้ชิ้นส่วนที่ได้รับการรับรองแล้วช่วยลดขั้นตอนที่จำเป็นและทำให้กระบวนการรับรองสั้นลง

ส่วนประกอบอินเทอร์เฟซ RTD ที่ใช้งานได้และมีการบูรณาการสูงเป็นกุญแจสำคัญในการผ่อนปรนการรับรอง Route 2S เนื่องจากส่วนประกอบดังกล่าวกำหนดแพคเกจโซลูชันที่สมบูรณ์ และด้วยเหตุนี้จึงสามารถกำหนดคุณลักษณะได้อย่างสมบูรณ์ด้วยข้อมูลที่เกี่ยวข้องกับการใช้งานภาคสนามและความล้มเหลว ซึ่งแตกต่างจากการใช้ไอซีแบบสำเร็จรูปขนาดเล็กหลายตัว ซึ่งอินเทอร์เฟซและการโต้ตอบต่างๆ ของไอซีเหล่านั้นต้องได้รับการวิเคราะห์สำหรับการกำหนดค่าการเชื่อมต่อโครงข่ายเฉพาะที่ใช้

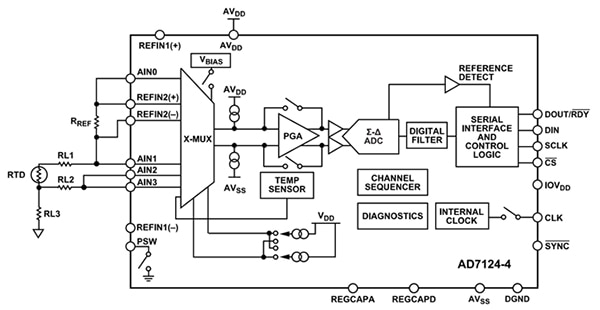

ตัวอย่างได้แก่ AD7124-4 สี่ช่องสัญญาณ (รูปที่ 4) และ AD7124-8 แปดช่องที่คล้ายกัน (จากนี้ไปจะเรียกโดยรวมว่า “AD7124” เมื่อพูดถึงคุณสมบัติหลายอย่างที่มีเหมือนกัน) ส่วนประกอบเหล่านี้เหมาะสมอย่างยิ่งสำหรับ Route 2S เนื่องจากมีคุณลักษณะการทดสอบและวินิจฉัยตัวเองในตัว ตลอดจน "บันทึกการติดตาม" ในภาคสนาม

รูปที่ 4: AD7124-4 สี่แชนเนลเป็นเชนสัญญาณระหว่างเซ็นเซอร์กับโปรเซสเซอร์ RTD ที่สมบูรณ์ในการทำงาน (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 4: AD7124-4 สี่แชนเนลเป็นเชนสัญญาณระหว่างเซ็นเซอร์กับโปรเซสเซอร์ RTD ที่สมบูรณ์ในการทำงาน (แหล่งที่มาภาพ: Analog Devices)

ไอซีเหล่านี้เป็นโซลูชันที่สมบูรณ์สำหรับการวัด RTD แบบหลายช่องสัญญาณ และรวมหน่วยโครงสร้างทั้งหมดที่จำเป็นตั้งแต่เซ็นเซอร์ไปจนถึงเอาต์พุตดิจิทัล และสำหรับการสื่อสารกับไมโครคอนโทรลเลอร์ที่เกี่ยวข้อง ซึ่งประกอบด้วยมัลติแชนแนลมัลติเพล็กเซอร์, PGA, ADC ซิกม่า-เดลต้า 24 บิต, แหล่งจ่ายกระแสสำหรับ RTD, แรงดันไฟฟ้าอ้างอิงสำหรับการทำงานภายใน, นาฬิการะบบ, การกรองแอนะล็อกและดิจิตอล และอินเทอร์เฟซแบบอนุกรมสามสายหรือสี่สายสำหรับ SPI, QSPI, MICROWIRE และการเชื่อมต่อระหว่างกันที่เข้ากันได้กับ DSP

อย่างไรก็ตามฟังก์ชันเหล่านี้ไม่ได้ให้พื้นฐานสำหรับการรับรอง SIL Route 2S สำหรับการออกแบบที่ปลอดภัยต่อการใช้งานนั้น จำเป็นต้องมีชุดการวินิจฉัยแบบฝังตัวสำหรับฟังก์ชันต่างๆ ที่ประกอบด้วยระบบ RTD โดยการวินิจฉัยแบบฝังหลายตัวใน AD7124 ช่วยลดทั้งความซับซ้อนในการออกแบบและเวลาในการออกแบบ และขจัดความจำเป็นในการขยายสายสัญญาณเพื่อความครอบคลุมในการวินิจฉัย

การวินิจฉัยเหล่านี้รวมถึงแต่ไม่จำกัดเพียงการตรวจสอบแหล่งจ่ายไฟ แรงดันอ้างอิง และอินพุตแบบแอนะล็อก การตรวจจับสายเปิดไปยัง RTD การตรวจสอบประสิทธิภาพการแปลงและการสอบเทียบ ตรวจสอบการทำงานของสายสัญญาณ การตรวจสอบฟังก์ชันการอ่าน/เขียน และการตรวจสอบรีจิสเตอร์

คำว่า "ระดับสูง" เหล่านี้แปลเป็นการวินิจฉัยบนชิปที่จำเป็นได้อย่างไร คำตอบมีหลายแง่มุม ได้แก่ :

การวินิจฉัย SPI: สำหรับการเขียนไปยัง AD7124 ทุกครั้ง ตัวประมวลผลจะสร้างค่าการตรวจสอบความซ้ำซ้อนแบบวนซ้ำ (CRC) ที่ต่อท้ายข้อมูลที่ส่งไปยัง ADC จากนั้น ADC จะสร้างค่า CRC ของตัวเองจากข้อมูลที่ได้รับและเปรียบเทียบกับค่า CRC ที่ได้รับจากโปรเซสเซอร์ หากค่าทั้งสองสอดคล้องกัน ข้อมูลจะยังคงอยู่และจะถูกเขียนไปยังรีจิสเตอร์บนชิปที่เกี่ยวข้อง

หากค่าไม่ตรงกัน แสดงว่าเกิดการเสียหายเล็กน้อยในการส่ง และไอซีจะตั้งค่าสถานะข้อผิดพลาดที่บ่งชี้ว่าข้อมูลเสียหายเกิดขึ้น นอกจากนี้ AD7124 ยังป้องกันตัวเองด้วยการไม่เขียนข้อมูลที่เสียหายลงในเครื่องบันทึก

ขั้นตอน CRC ที่คล้ายกันจะถูกนำมาใช้เมื่ออ่านข้อมูลจาก AD7124 ไปยังตัวประมวลผลระบบ สุดท้าย อินเทอร์เฟซยังนับพัลส์สัญญาณนาฬิกาเพื่อให้แน่ใจว่ามีเพียงแปดพัลส์ดังกล่าวในแต่ละเฟรมข้อมูลการอ่านหรือเขียน ดังนั้นจึงมั่นใจได้ว่าสัญญาณนาฬิกาจะไม่เกิดขึ้น

การตรวจสอบหน่วยความจำ: CRC ยังใช้เพื่อตรวจสอบเนื้อหาของรีจิสเตอร์เมื่อเปิดเครื่องหรือเมื่อใดก็ตามที่รีจิสเตอร์บนชิปมีการเปลี่ยนแปลง (เช่น เมื่อเปลี่ยนเกน) กระบวนการ CRC จะดำเนินการเป็นระยะเพื่อให้แน่ใจว่าไม่มีบิตหน่วยความจำ "พลิกกลับ" เนื่องจากสัญญาณรบกวนหรือสาเหตุอื่นๆ หากมีการเปลี่ยนแปลงและต่อมามีการเตือนโปรเซสเซอร์ว่าการตั้งค่ารีจิสเตอร์เสียหาย โปรเซสเซอร์สามารถรีเซ็ต ADC และรีโหลดรีจิสเตอร์ได้

การตรวจสอบสายสัญญาณ: สามารถตรวจสอบแรงดันไฟฟ้าสถิตที่สำคัญทั้งหมดได้ผ่าน ADC รวมถึงรางจ่ายไฟ เอาต์พุตควบคุมแรงดันต่ำ (LDO) และแรงดันอ้างอิง สามารถตรวจสอบการมีหรือไม่มีตัวเก็บประจุภายนอกทั่วทั้ง LDO นอกจากนี้ยังสามารถใช้แรงดันไฟฟ้าที่ทราบกับอินพุต ADC เพื่อตรวจสอบ ADC และการตั้งค่าฟังก์ชันเกน นอกจากนี้ ยังสามารถป้อนกระแสที่ทราบผ่านอินพุตแบบแอนะล็อกเพื่อตรวจสอบ RTD แบบเปิดหรือแบบลัดวงจร

การแปลงและการสอบเทียบ: ผลลัพธ์ของการแปลง ADC จะได้รับการตรวจสอบอย่างต่อเนื่องเพื่อดูว่าไปที่มีค่าศูนย์หรือเต็มสเกล ซึ่งทั้งสองอย่างบ่งชี้ว่ามีปัญหา โดยบิตสตรีมจากโมดูเลเตอร์ที่แกนกลางของ ADC จะถูกตรวจสอบเพื่อให้แน่ใจว่ายังไม่อิ่มตัว และถ้าเกิดความอิ่มตัว (หมายความว่ามี 20 รายการติดต่อกันหรือเป็นศูนย์จากโมดูเลเตอร์) จะมีการตั้งค่าสถานะข้อผิดพลาด

ความถี่สัญญาณนาฬิกาหลัก: ความถี่ของสัญญาณนาฬิกานี้ไม่เพียงแต่ควบคุมอัตราการแปลงเท่านั้น แต่ยังกำหนดความถี่นอตช์ของตัวกรองดิจิทัล 50/60 เฮิรตซ์ (Hz) โดยรีจิสเตอร์ภายใน AD7124 ช่วยให้โปรเซสเซอร์ที่ใช้ร่วมกันจับเวลาและด้วยเหตุนี้จึงตรวจสอบความถูกต้องของนาฬิกาหลัก

คุณลักษณะเพิ่มเติม: AD7124 มีเซ็นเซอร์อุณหภูมิ ซึ่งสามารถใช้ตรวจสอบอุณหภูมิของดายได้ ทั้งสองรุ่นมีอัตราการปล่อยไฟฟ้าสถิต (ESD) 4 กิโลโวลต์ (kV) เพื่อประสิทธิภาพที่ทนทาน และทั้งสองรุ่นอยู่ในแพ็คเกจ LFCSP ขนาด 5 × 5 มิลลิเมตร (มม.) ที่เหมาะสำหรับการออกแบบที่ปลอดภัย

เนื่องจากความซับซ้อนภายใน ความซับซ้อน และคุณสมบัติการทดสอบตัวเองขั้นสูงของ AD7124-4 และ AD7124-8 จึงเหมาะสมที่จะมีวิธีดำเนินการและประเมินไอซี

เพื่อให้บรรลุเป้าหมายนี้ Analog Devices ขอเสนอบอร์ดเชื่อมต่อคู่หนึ่ง: บอร์ดประเมินผล EVAL-AD7124-4SDZ สำหรับ AD7124-4 (รูปที่ 5) และ EVAL-SDP-CB1Z SDP (แท่นสาธิตระบบ)/บอร์ดอินเทอร์เฟซ (รูปที่ 6) ตัวแรกมีเฉพาะสำหรับ AD7124-4 และทำงานร่วมกับตัวหลัง ซึ่งให้การสื่อสารกับพีซีของผู้ใช้และซอฟต์แวร์การประเมินผ่านการเชื่อมต่อ USB

รูปที่ 5: EVAL-AD7124-4SDZ เป็นบอร์ดประเมินผลสำหรับ AD7124-4 (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 5: EVAL-AD7124-4SDZ เป็นบอร์ดประเมินผลสำหรับ AD7124-4 (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 6: EVAL-SDP-CB1Z/บอร์ดอินเทอร์เฟซ เป็นคู่หูของ EVAL-AD7124-4SDZ ซึ่งให้การเชื่อมต่อ USB กับโฮสต์พีซี (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 6: EVAL-SDP-CB1Z/บอร์ดอินเทอร์เฟซ เป็นคู่หูของ EVAL-AD7124-4SDZ ซึ่งให้การเชื่อมต่อ USB กับโฮสต์พีซี (แหล่งที่มาภาพ: Analog Devices)

การจัดการประเมินผลได้รับการสนับสนุนจากซอฟต์แวร์ AD7124-4 EVAL+ ซึ่งกำหนดค่าฟังก์ชันการลงทะเบียนอุปกรณ์ AD7124-4 อย่างสมบูรณ์และใช้งานไอซี นอกจากนี้ยังมีการวิเคราะห์โดเมนเวลาในรูปแบบของกราฟรูปคลื่น ฮิสโตแกรม และการวิเคราะห์สัญญาณรบกวนที่เกี่ยวข้องสำหรับการประเมินประสิทธิภาพของ ADC

เปลี่ยนไปสู่การออกแบบที่ปลอดภัยในการใช้งาน

สิ่งสำคัญคือต้องตระหนักว่า AD7124-4 และ AD7124-8 ไม่ได้รับการจัดระดับ SIL ซึ่งหมายความว่าไม่ได้ออกแบบและพัฒนาโดยใช้แนวทางการพัฒนาที่กำหนดโดยมาตรฐาน IEC 61508 อย่างไรก็ตาม เมื่อทำความเข้าใจกับการใช้งานสุดท้ายและผ่านการใช้การวินิจฉัยต่าง ๆ อย่างเหมาะสม จะสามารถประเมินเพื่อใช้ในการออกแบบตามระดับ SIL

เส้นทางสู่การรับรอง Route 1S มีข้อควรพิจารณาหลายประการสำหรับการวิเคราะห์และระบุถึงความล้มเหลว ซึ่งอาจเป็นระบบหรือแบบสุ่ม ความล้มเหลวของระบบเกิดจากข้อบกพร่องในการออกแบบหรือการผลิต เช่น การอินเตอรรัพท์ที่มีสัญญาณรบกวนเนื่องจากขาดการกรองบนพินการอินเตอรรัพท์ภายนอก หรือพื้นที่ไม่เพียงพอสำหรับสัญญาณ ในทางกลับกัน ความล้มเหลวแบบสุ่มเกิดจากสาเหตุทางกายภาพ เช่น การกัดกร่อน ความเครียดจากความร้อน หรือการสึกหรอ

ข้อกังวลที่สำคัญเรียกว่าความล้มเหลวที่ตรวจไม่พบที่เป็นอันตราย ซึ่งแก้ไขได้ด้วยเทคนิคหลายอย่าง เพื่อลดความล้มเหลวแบบสุ่ม นักออกแบบใช้หนึ่งหรือสามกลยุทธ์:

- ส่วนประกอบที่น่าเชื่อถือมากขึ้นและเครียดน้อยลง

- การวินิจฉัยที่อาศัยกลไกการตรวจจับในตัวที่ดำเนินการผ่านฮาร์ดแวร์หรือซอฟต์แวร์

- ความทนทานต่อความผิดพลาดผ่านวงจรสำรอง ด้วยการเพิ่มเส้นทางที่ซ้ำซ้อน ความล้มเหลวเพียงครั้งเดียวสามารถยอมรับได้ สิ่งนี้เรียกว่าระบบ Hardware Fault Tolerance 1 (HFT 1) หมายความว่าความล้มเหลวเพียงครั้งเดียวไม่สามารถทำให้ระบบล้มเหลวได้

เครื่องมือหนึ่งในการทำความเข้าใจความครอบคลุมระดับ SIL คือเมทริกซ์ที่วางแผนค่าสัดส่วนความล้มเหลวที่ปลอดภัย (SFF) (จำนวนความครอบคลุมการวินิจฉัย) และความทนทานต่อข้อบกพร่องของฮาร์ดแวร์ (ความซ้ำซ้อน) (รูปที่ 7)

|

|||||||||||||||||||||||

รูปที่ 7: เมทริกซ์นี้แสดงลักษณะของเศษส่วนความล้มเหลวที่ปลอดภัย (SFF) เทียบกับความทนทานต่อความผิดพลาดของฮาร์ดแวร์ (HFT) และให้ข้อมูลเชิงลึกเกี่ยวกับความครอบคลุมของ SIL (แหล่งที่มาภาพ: Analog Devices)

แถวแสดงจำนวนความครอบคลุมของการวินิจฉัย ขณะที่คอลัมน์แสดงค่าความทนทานต่อข้อบกพร่องของฮาร์ดแวร์ โดย HFT ของ 0 หมายความว่าหากมีข้อผิดพลาดในระบบ ฟังก์ชันความปลอดภัยจะหายไป การวินิจฉัยในระดับที่สูงขึ้นช่วยลดจำนวนความซ้ำซ้อนของระบบที่จำเป็นหรือปรับปรุงระดับ SIL ของโซลูชันด้วยระดับความซ้ำซ้อนที่เท่ากัน (ลดเมทริกซ์ลง)

โปรดทราบว่า FMEDA ในการใช้งานอุณหภูมิทั่วไปที่ใช้อุปกรณ์เหล่านี้แสดงเศษส่วนความล้มเหลวที่ปลอดภัย (SFF) มากกว่า 90% ตามมาตรฐาน IEC 61508 โดยปกติแล้ว ADC แบบดั้งเดิมสองตัวจะต้องใช้เพื่อให้ความครอบคลุมในระดับนี้ผ่านความซ้ำซ้อน แต่ AD4172 ต้องการเพียง ADC เพียงตัวเดียว จึงช่วยประหยัดต้นทุนรายการวัสดุ (BOM) และพื้นที่ในบอร์ดได้อย่างมาก

เอกสารประกอบสำหรับการออกแบบที่มีการจัดระดับ SIL

เพื่อให้ได้รับการรับรอง Route 1S จำเป็นต้องมีเอกสารประกอบมากมาย ในบรรดาเอกสารต้นฉบับที่จำเป็นได้แก่:

- เอกสารข้อมูลความปลอดภัย (คู่มือความปลอดภัยสำหรับชิ้นส่วนที่ได้รับการจัดระดับ SIL)

- FMEDA แบบ Pin และ FMEDA แบบ Die พร้อมโหมดความล้มเหลว เอฟเฟกต์ และการวิเคราะห์สำหรับทั้งสองอย่าง

- รายการตรวจสอบภาคผนวก F (กำหนดโดย IEC 61508)

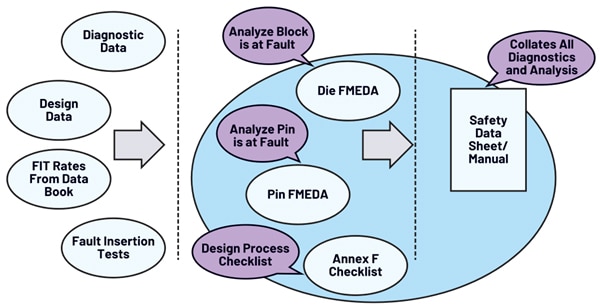

ในทางกลับกัน เอกสารนี้มาจากหลายแหล่ง (รูปที่ 8):

- ข้อมูลการวินิจฉัยจากเอกสารข้อมูลจะรวบรวมคุณลักษณะการวินิจฉัยทั้งหมดที่มีอยู่ในส่วนนั้น

- ข้อมูลการออกแบบหมายถึงข้อมูลภายใน ตัวอย่างเช่น พื้นที่ดายและผลกระทบของบล็อกภายในของชิ้นส่วนแต่ละชิ้น

- FIT พร้อมอัตราสำหรับส่วนประกอบต่างๆ สามารถดูได้จากเอกสารข้อมูล

- ทำการทดสอบข้อบกพร่องการถอดและประกอบสำหรับบล็อกที่ไม่สามารถวิเคราะห์โดยใช้ข้อมูลการออกแบบและการวินิจฉัย การทดสอบเหล่านี้มีการวางแผนตามข้อกำหนดการใช้งาน และผลของการทดสอบจะใช้เพื่อเสริมความแข็งแกร่งให้กับเอกสาร FMEDA และ FMEA

รูปที่ 8: แหล่งเอกสารที่หลากหลายถูกรวบรวมและดึงออกมาเพื่อให้ชุดข้อมูลที่สมบูรณ์ที่จำเป็นสำหรับการรับรอง SIL (แหล่งที่มาภาพ: Analog Devices)

รูปที่ 8: แหล่งเอกสารที่หลากหลายถูกรวบรวมและดึงออกมาเพื่อให้ชุดข้อมูลที่สมบูรณ์ที่จำเป็นสำหรับการรับรอง SIL (แหล่งที่มาภาพ: Analog Devices)

ดูเฉพาะในรายละเอียดเพิ่มเติม:

- คู่มือความปลอดภัยหรือเอกสารข้อมูลความปลอดภัย ใช้ข้อมูลที่รวบรวมทั้งหมดเพื่อจัดเตรียมข้อกำหนดที่จำเป็นเพื่อให้สามารถรวม AD7124-4 หรือ AD7124-8 ได้ โดยจะรวบรวมการวินิจฉัยและการวิเคราะห์ทั้งหมดที่มาจากเอกสารและชุดข้อมูลต่างๆ

- FMEDA แบบ Die สำหรับ AD7124-4 และ AD7124-8 จะวิเคราะห์บล็อกหลักในแผนผังแอปพลิเคชัน ระบุโหมดความล้มเหลวและผลกระทบ และตรวจสอบการวินิจฉัยและวิเคราะห์สำหรับฟังก์ชันความปลอดภัยเฉพาะ ตัวอย่างเช่น การวิเคราะห์โมดูลนาฬิกาจะแสดงโหมดความล้มเหลว ผลกระทบของแต่ละเอาต์พุต ปริมาณของการครอบคลุมการวินิจฉัย และการวิเคราะห์ผลกระทบ (รูปที่ 9)

|

รูปที่ 9: ตารางนี้กำหนดอาการความล้มเหลวของบล็อกนาฬิกาหลัก ผลกระทบ การวินิจฉัย และการวิเคราะห์ (แหล่งที่มาภาพ: Analog Devices)

FMEDA แบบ Die นี้ส่งผลให้เกิดอัตราความล้มเหลวเชิงปริมาณสำหรับความล้มเหลวที่ปลอดภัย ความล้มเหลวที่ตรวจพบที่เป็นอันตราย และความล้มเหลวที่ตรวจไม่พบที่เป็นอันตราย ทั้งหมดนี้ใช้ในการคำนวณ SFF

FDEMA แบบ Pin มองความล้มเหลวจากมุมมองที่แตกต่างออกไป โดยจะวิเคราะห์ความล้มเหลวประเภทต่าง ๆ บนพินของ AD7124-4 และ AD7124-8 และผลลัพธ์สำหรับ RTD ซึ่งทำเช่นนี้สำหรับแต่ละพินและอธิบายผลลัพธ์สำหรับกรณีที่พินเปิด ช็อตไปยังแหล่งจ่าย/กราวด์ หรือช็อตไปยังพินที่อยู่ติดกัน

รายการตรวจสอบภาคผนวก F เป็นรายการตรวจสอบการออกแบบเพื่อหลีกเลี่ยงความล้มเหลวอย่างเป็นระบบ ประกอบด้วย:

- ภาพรวมผลิตภัณฑ์

- ข้อมูลการสมัคร

- แนวคิดด้านความปลอดภัย

- การคาดการณ์ตลอดชีวิต

- FIT

- การคำนวณ FMEDA—SFF และ DC

- กลไกความปลอดภัยของฮาร์ดแวร์

- คำอธิบายการวินิจฉัย

- ความทนทาน EMC

- การดำเนินการในการกำหนดค่าซ้ำซ้อน

- ภาคผนวกและรายการเอกสาร

โดยสรุป การรับรองความปลอดภัยด้านการทำงานสำหรับส่วนประกอบที่เพิ่งเปิดตัวผ่าน Route 1S นั้นยาว ซับซ้อน ใช้เวลานาน รุนแรง และครอบคลุม แต่เป็นเรื่องที่ดีที่ Route 2S เป็นแนวทางทางเลือกที่ใช้ได้กับส่วนประกอบบางอย่าง ดังที่กล่าวไว้ข้างต้น

Route 2S: เส้นทางทางเลือก

เส้นทางที่รู้จักกันในชื่อ Route 2S ใช้ได้กับชิ้นส่วนที่มีประสบการณ์ภาคสนามและข้อมูล และกำหนดให้เป็น "ได้รับพิสูจน์จากการใช้งาน" โดยอ้างอิงจากการวิเคราะห์ผลิตภัณฑ์ส่งคืนของลูกค้าและจำนวนอุปกรณ์ที่จัดส่ง ซึ่งไม่สามารถใช้กับชิ้นส่วนใหม่ที่มี "ประวัติการติดตาม" เพียงเล็กน้อยหรือไม่มีเลยในการใช้งานจริง

Route 2S ช่วยให้การรับรอง SIL เหมือนกับว่าชิ้นส่วนได้รับการวิเคราะห์อย่างสมบูรณ์ภายใต้มาตรฐาน IEC 61508 พร้อมใช้งานสำหรับผู้ออกแบบโมดูลและระบบหากพวกเขาเคยใช้ไอซีนั้น ๆ ได้สำเร็จในอดีตและทราบอัตราความล้มเหลวจากภาคสนาม ซึ่งคุณลักษณะการทดสอบและการตรวจสอบที่ฝังอยู่ พร้อมด้วยข้อมูลประสิทธิภาพ ทำให้ AD7214-4 และ AD7214-8 เป็นตัวเลือกที่ดีสำหรับ Route 2S

การเรียกใช้ Route 2S ต้องการข้อมูลโดยละเอียดและมีนัยสำคัญทางสถิติเกี่ยวกับผลิตภัณฑ์ส่งคืนจากภาคสนามและผลิตภัณฑ์ที่ล้มเหลว ข้อกำหนดนี้เป็นเรื่องยากมากสำหรับผู้จำหน่ายไอซีที่จะปฏิบัติตามมากกว่าซัพพลายเออร์บอร์ดหรือโมดูล เหตุผลก็คือโดยทั่วไปแล้วผู้จำหน่ายไอซีไม่มีความรู้เพียงพอเกี่ยวกับการใช้งานขั้นสุดท้าย หรือเปอร์เซ็นต์ของผลิตภัณฑ์ที่ล้มเหลวจากหน้างานจะถูกส่งคืนให้พวกเขาเพื่อการวิเคราะห์

สรุป

Route 1S สำหรับการรับรองความปลอดภัยในการใช้งานของผลิตภัณฑ์ใหม่นั้นละเอียด ครอบคลุม และซับซ้อน นอกจากนี้ยังมีความท้าทายทางเทคนิคและใช้เวลานานอย่างแน่นอน ในทางตรงกันข้ามกระบวนการ Route 2S ช่วยให้ผลิตภัณฑ์ที่จัดจำหน่ายแล้วได้รับการรับรองตามประสบการณ์ภาคสนาม ความล้มเหลว และข้อมูลการวิเคราะห์ ซึ่งเป็นเส้นทางที่มีประโยชน์และรองรับโดยไอซีอินเทอร์เฟซ AD7214-4 และ AD7214-8 RTD เนื่องจากมีประวัติที่จำเป็น สิ่งที่สำคัญไม่แพ้กัน ไอซีเหล่านี้ได้รวมฟังก์ชันการวินิจฉัยและการทดสอบตัวเองและคุณลักษณะต่างๆ ไว้มากมาย ซึ่งทำให้มีคุณสมบัติเหมาะสมสำหรับการรับรองดังกล่าว

เนื้อหาที่เกี่ยวข้อง

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.